Изобретенве относится к радиотез& нике и может быть использовано для передачи дискретной информации с высокой скоростью.

Известно устройство для передачи и приема дискретной информапии, содержащее на передаюшей стороне регистр сдвига с цепью обратной связи а на приемной стороне - перилй регистр сдвига с цепью обратной связи, между входом и соответствующим выходом которого включен сумматор по модулю два, второй регистр сдвига с цепью обратной связи, счетчик и триггер управпе ния i .

Однако в известном устройстве велико время поиска сообщений,

изобретения является сокра-. щение времени приема сигналов днскрет ной информации.

Для этого, в устройство для передачи и приема дискретной информации, содержащее на передаюшей стороне регистр сдвига с цепью обратной связи, а на

приемной стороне - первый регистр сдвига с цепью обратной связи, между входом и соответствугопшм выходом которого включен сумматор по модулю два, второй регистр сдвига с -цепь (йр тной связи, счетчик и триггер управления на передающей стороне введены вычитающий счетчик, дешифратор, инвертор, триггер, блок совпадения, элемент ИЛИ и блок задержки, приватом выходы вычитакхшего счетчика подключены к соответствующим взюдам дешифратора, шлход которого непосредственно и через инвертор подключен к входам триггера, выход которого через последовательно соединенные блок совпадения и злемекг ИЛИ подключен к тактовому входу регистра сдвига с цепью обратной связи выход которого подключен к входу блока задержки, а на приемной стороне введены блок сравнения, инвертор, блок задержки, блок совпадения, элемент ИЛИ, суммируюшнй счетчик т промежуточный накопитель, при этом выход сумматора

по иодулю два подключен через инвертор к счетному входу счетчика, к входу Сброс которого подключены выход сумматора по модулю два и выход счетчика через блок задержки, между выходами соответствующих разрядов первого и второго регистров сдвига с цепями обратной связи включен блок сравнения, выход которого подключен к нулевому входу триггера управления, к единичному входу которого подключен выход счетчик а выходы триггера управления подключены к входам суммирующего счетчика непосредственно и через блок совпадения, выход которого подключен к соответствуикцему входу второго регистра сдвига с цепью обратной связи через элемент ИЛИ а выходы суммируюшего счетчика подключены к соответствующим входам промежуточного накопителя.

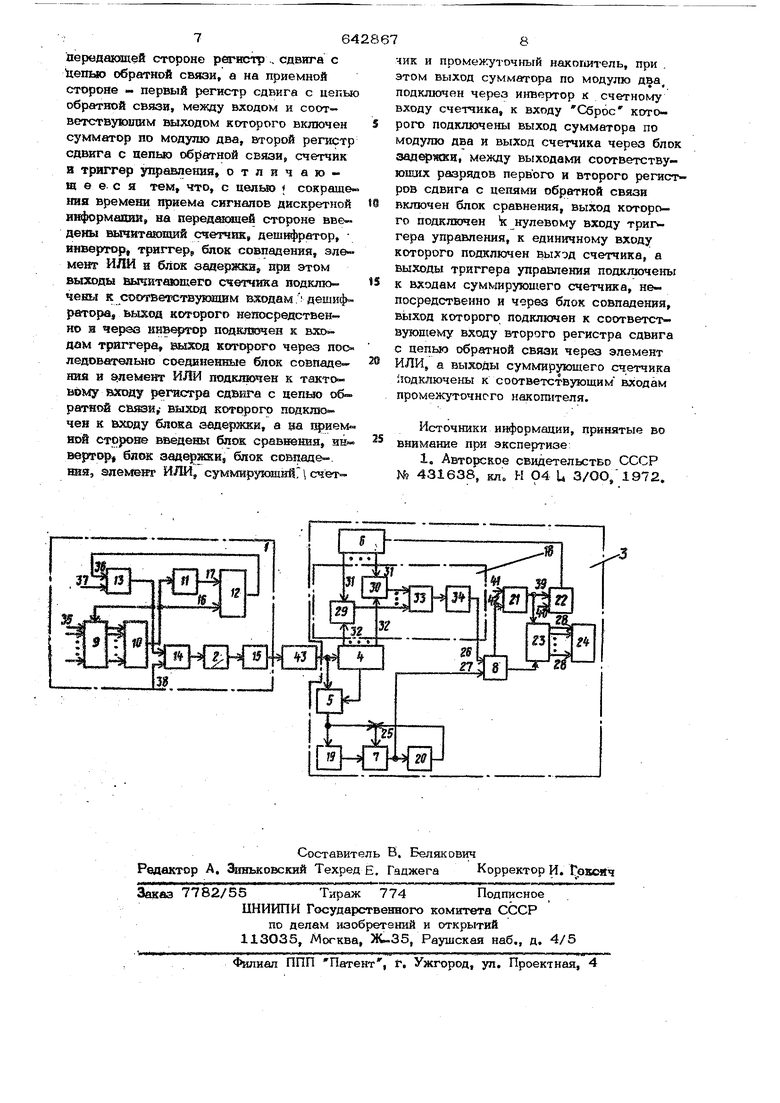

На чертеже приведена структурная электрическая схема устройства.

Устройство для передачи и приема дискретной инфор мании содержит на пе редающей стороне 1 регистр 2 сдвига с цепью обратной связи, а на приемной стороне 3 - первый регистр 4 сдвига с цепью обратной связи, между входом и соответствующим выходом которого включен сумматор 5 по модулю два, второй регистр 6 сдвига с цепью обратной связИз счетчйк 7 и триггер 8 управления, а также на .передающей стороне 1 вычитающий счетчик 9, дешифратор 10, инвертор И, триггер 12, блок 13 совпадения, элемент ИЛИ 14; и блок 13 задержки, при этом выходы вьшитаюшего счетчика 9 подключены к соответствующим входам дешифратора lOj выход которого непосредственно и через инвертор 11 подключен к входам 16 и 17 триггера 12, выход которого через последовательно соедииеннзае блок 13 совпадения и элемент ИЛИ 14 подключен к тактовому входу регистра 2 сдвига с цепью обратной связи, выход которого подключен к входу блока 15 задержки, а на приемной стороне 3 блок 18 сравнения, инвертор 19, блок 2О задержки, блок 21 соЕяадения, элемент ИЛИ 22, суммирующий счетчик 23 и промежуточный накопитель 24, при этом выход сумматора 5 1ТО модулю два подключен через инвертор 19 к счетному входу счетчика 7, к входу 25 Сброс которого подключены выход сумматора 5 по модулю два н выход счетчика 7 через блок

20 задержки, между выходами соответствукяцих разрядов первого и второго регистров 4 и 6 сдвига с цепями обратной связи включен блок 1В сравнения, выход которого подключен к нулевому входу 26 триггера 8 управления, к единичному входу 27 которого под ключей вгход счетчика 7, а выходы триггера 8 управления подключены к входам суммирующего счетчика 23 непосредственно и через блок 21 совпадения, выход которого подключен к соответствующему входу второго регистра 6 сдвига с цепью обратной связи через элемент ИЛИ 22, а выходы суммируюшего счетчика 23 подключены к соответствующим входам 28 промежуточного накопителя 24, блок 18 сравнения состоит из сумматоров 29 и 30, к вхо дам 31 которых подключены второй регистр 6 сдвига с цепыо обратной связи а к входам 32 первый регистр 4 сдвига с цепью обратной связи элемента ИЛИ 33 и инвертора 34, кроме того, на чертеже показаны входы 35 вычитающего счетчика 9, входы 36 и 37 блока 13 совпадения, вход 38 элемен-та ИЛИ 14 для подачи быстрых тактовых импульсов (ТИ) входы 39 и 4О элемента ИЛИ 22, входы 41 и 42 бло ка 21 совпадения и 43 свяви между передающей и приемной сторонами 1 и 3,

Устройство работает следующим образом.

По команде с управляющего устройства Сне показано) в ячейки двоичного вычитающего счетчика 9 параллельным кодом по входам 35 происходит запись комбинации первичного кода. Если записанная комбинация отличается от нулевой, то на выходе дешифратора 10 появится нуль, который инвертируется инвертором 11, поступает на вход трипгера 12 и устанавливает упомянутый триггер 12 в состояние . Сигнал с выхода триггера 12 поступает на вход 36 блока 13, который открывает и пропускает поступающие на вэюд 37 блока 13 быстрые тактовые импульсы, частота следования которых не менее чем в N раз превыщает номинальную тактовую частоту, где N -выраженная в числе элементов длина комбинации вторичного кода, передаваемого в канал 43. Значение М должно удовлетворять неравенству N iSp 2 - i , где rt -длина комбинации первичного кода.

Быстрые тактовые импульсы с выхода блока 13 поступают на счет1{ый вход вычитающего счетчика 9 и параллельно через элемент ИЛИ 14 на тактовый вход регистра 2, Быстрые тактовые импульсы будут подаваться до тех пор, пока вычитаюииий счетчик 9 не установится в нулевое состояние, В последнем случае срабатывает дешифратор Ю нулевого состояния, сигнал с выхода которого поступает на вход 16 триггера 12 и устанавливает его в нулевое состояние, что приводит к закрыванию блока 13 и прекращению подачи быстрых тактовых импульсов (ТИ) на счетный вход вычитающего счетчика 9 и на тактовь1Й вход регистра 2, Таким образом, количество поступивших на тактовый вход регистра 2 быстрых ТИ зависит от того, какая комбинация первичного кода была записана в ячейки вычитающего счетчика 9. Под действием этих быстрых тактов за время, не превьш1аюшее периода номинальной тактовой частоты (длительности одной элементарной посылки), производится сдвиг фазы, формируемой в регистре 2 псевдослучайной последовательности (ПСП) на число шагов, равное десятичной цяфре, соответствующей двоичной комбинаций первичного кода. Под действием ТИ номинальной частоты, поступаюших на вход 38. элемента ИЛИ 14 и далее через не« го на тактовый вход регистра 2, производится выдача на вход 41 через блок 15 псевдослучайной последовательности с новой фазой. Bnotc 15 нес ходим для того, чтобы избежать дробления послед него элемента предыдущей ПСП во вре- мвформвровавия последующей ПСП в ретистре 2.

Принимаемая с выхода канала 43 последовательность поступает параллельно на вход первого регистра 4 с элементом логического сложенвя и на пер вый вход сумматора 5, на ш-орой вход которого подается последовательность, формируемая регистром 4. Если с выхода канала 43 поступает ПСП, не содержащая ошибок, то с выхода сумматора 5 через инвертор 19 на счетный вход счетчика 7 поступает последовательность нулей. При наличии в принимаемой последовательности зачетного участка длиной Е « П k (здесь Ц емкость счетчика 7, Г1 -«оличество р рядов регистра 4), не содержащего сяиибок, происходит заполнение счетчика 7.

В противном случае каждая единуща с выхода сумматора 5 поступает на вход 25 счетчика 7, сбрасывает показания счетчика 7 и устанавливает его в исходное состояние.

При заполнении счетчика 7 сигнал с его выхода поступает на вход 27 установки триггера 8 в един1«ное состояние и параллельно но вход блока 2О, с выхода которого задержанный импульс пдается на вход 25 Сброса счетчика 7 в исходное нулевое состояние.

Триггер 8, установленный в состояние , выдает сигнал с прямого выхода на вход 42 блока 21, последний открывается и по входу 41 через блок 21 начиназот поступать быстрые ТП на счетный рход сумкотрующего счетчика 23 н параллельно на вход 39 элемента ИЛИ 22, с выхэда которого они подаются на вход второго регистра 6 с логической (Кратной и производят сдвиг ранее 1финятоа (предыдущей) ПСП относительно щзннимаемой. Сдвиг осу- шествляетса ш совпаденид.фаз укаваяных последовательностей, при этом на входах 31 и 32 сумматоров 29 и ЗО блока 18 будут иметь место одинаковые комбинации, поэтьму на выходах сумматоров 29 и ЗО будут кули, на выходе элемента 33 будет также нуль, который через инвертор 34 поступит на вход 22В триггера 8 и установит его в нулевое состояние. Сигналом с инверсного выхода три1 гера в производится считывание показаний сук мирующего счетчика 23 на вяоды 28, Информационная комбинация с входов 28 передается в случае необходимости непосредственно потребителю или записывается в промежуточный накопитель 24, обеспечивающий синхронную выдачу информации потребителю,

ПоЕазапия суммирухмдего счетчика 23 представояют co6ofi комбияавию первячного кода, введеннуто на передаче, которая выявлена на приеме нугсм под-, счета числа шагов, на которое различаются фазы соседних последовательно передаваемых ПСП. После выдвчн тф}р мащга потребителю устройство ца приемАой стороне 3 возвращается в исходное состояние.

Ф

ормула изобретения

Устройство для передачи н приема дискретной информации, содержащее на

оередаюшей стороне регистр ., сдвига с emao обратной связи, а на приемной сторойе - первый регистр сдвига с цепью обратной связи, между входом и соот ветствуюшим выходом которого включен сумматор по модулю два, второй решстр сдвига с цепью обратной связи, счетчик и триггер утфавлеюш отличаюш в е с я тем, что, с целыо ; сокраще ниа времени приема сигналов дискретной ииформшош, на передающей стороне введены вычйтаюншй счетчик, дешифратор, инвертор триггер блок совпадения, эле мет- ИЛИ а 6jioK задержки при этом выходы вычитающего счетчика подключены к соответ-ствукйзоим входам.; дешифратора, выход которого непосредственно в через подключен к входам триггера, йиход которого через поо ледоввгеяьно соединеншае блок совпадения и элемеш- ИЛИ подключен к тактовому входу регистра сдвига с цепью об.

ратНОЙ СВ5КЗй,- выход которого ПОДКЛЮ

чен к входу блока аадержкй, а на прием ной стороне введены блок сравнения, ин верто, бяок , блок сов:Е1аде«-. ВИЯ, элемент ИЛИ, суммирующий и промежуточный накогштель, при . этом выход сумматора по модулю два, подключен через инвертор к счетному входу счетчика, к входу Сброс ксхгорого подключень выход сумматора по модулю два и выход счетчика через блок задержки, между выходами соответствующих разрядов первого и второго регистров сдвига с цепями обратной связи

включен блок сравнения, выход которого подключен k нулевому входу триггера управления, к единичному входу которого подключен выход счетчика, а выходы триггера управления подключены

к входам суммирующего счетчика, непосредственно и через блок совпадения, выход которого подключен к соответствующему входу второго регистра сдвига с цепью обратной связи через элемент ИЛИ, а выходы суммирующего счетчика юдключены к соответствующим входам промежуточного накопителя.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 431638, кл. Н 04 U З/ОО, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1985 |

|

SU1298942A2 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Система для передачи и приема дискретной информации | 1980 |

|

SU886296A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФАЗОВОГО СДВИГА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2013016C1 |

| Устройство для передачи и приема дискретной информации | 1981 |

|

SU1027838A1 |

| СПОСОБ КОДИРОВАНИЯ ИНФОРМАЦИИ ОТРЕЗКАМИ ЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2568320C1 |

| Дискретный согласованный фильтр | 1978 |

|

SU771891A2 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

Авторы

Даты

1979-01-15—Публикация

1976-11-15—Подача