i (Л

I

ел

со ел

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| Устройство для измерения преобладаний дискретных сигналов | 1979 |

|

SU879805A1 |

| Устройство для передачи и приема дискретной информации | 1985 |

|

SU1298942A2 |

| Способ и устройство безопасной обработки служебно-технологических команд в инфокоммуникационных системах | 2018 |

|

RU2700400C1 |

| Способ и устройство изменения скорости передачи цифрового звукового сигнала телерадиовещания с предыскажением | 2024 |

|

RU2830465C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2005 |

|

RU2320080C2 |

| Дискретный согласованный фильтр | 1978 |

|

SU771891A2 |

| ЛИНИЯ РАДИОСВЯЗИ | 2001 |

|

RU2193278C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение пропускной способности. Устройство содержит на передающей стороне эл-ты И 1, 10, 11, 14 и 15, суммирующий счетчик 2, вычитающий счетчик 3, эл-ты ИЛИ 4 и 16, формирователь 5 импульсов, счетчик 6 импульсов, блоки задержки 7, 8 и 9, г-р 12 псевдослучайной последовательности (ПСП) и сумматор 13 по модулю два, а на приемной стороне выделитель 17 ПСП, блоки сравнения 18, 31 и 32, г-р 19 ПСП, RS-триггер 20, счетчик 21 импульсов, эл-т И 22, суммирующий счетчик 23, накопитель 24, регистры 25, 26, 27 и 28 сдвига, сумматоры 29 и 30 и кодопреобразователь 33, а также канал 34 связи. Передаваемый дискретный сигнал поступает на передающую сторону, где формируется кодовая последовательность, которая через канал 34 поступает на приемную сторону. Кроме того, на передающей стороне формируется маркерный импульс, сигнализирующий на приемную сторону о начале поступления очередной, следующей за ним, кодовой группы. Сигнал, преобразованный на приемной стороне, поступает на информационный выход устройства. 2 ил.

ки 7,8 и 9 задержки, г-р 12 псевдослучайной последовательности (ПСП) и сумматор 13 по модулю два, а на приемной стороне - выделитель 17 ПСП, блоки 18,31 и 32 сравнения, г-р 19 ПСП, RS-триггер 20, счетчик 21 импульсов, эл-т И 22, суммирующий счетчик 23, накопитель 24, регистры 25-28 сдвига, сумматоры 29 и ЗО-и кодопре- образователь 33, а также канал 34 связи. Передавае1-ый дискретный сигИзобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации .

Целью изобретения является повышение пропускной способности.

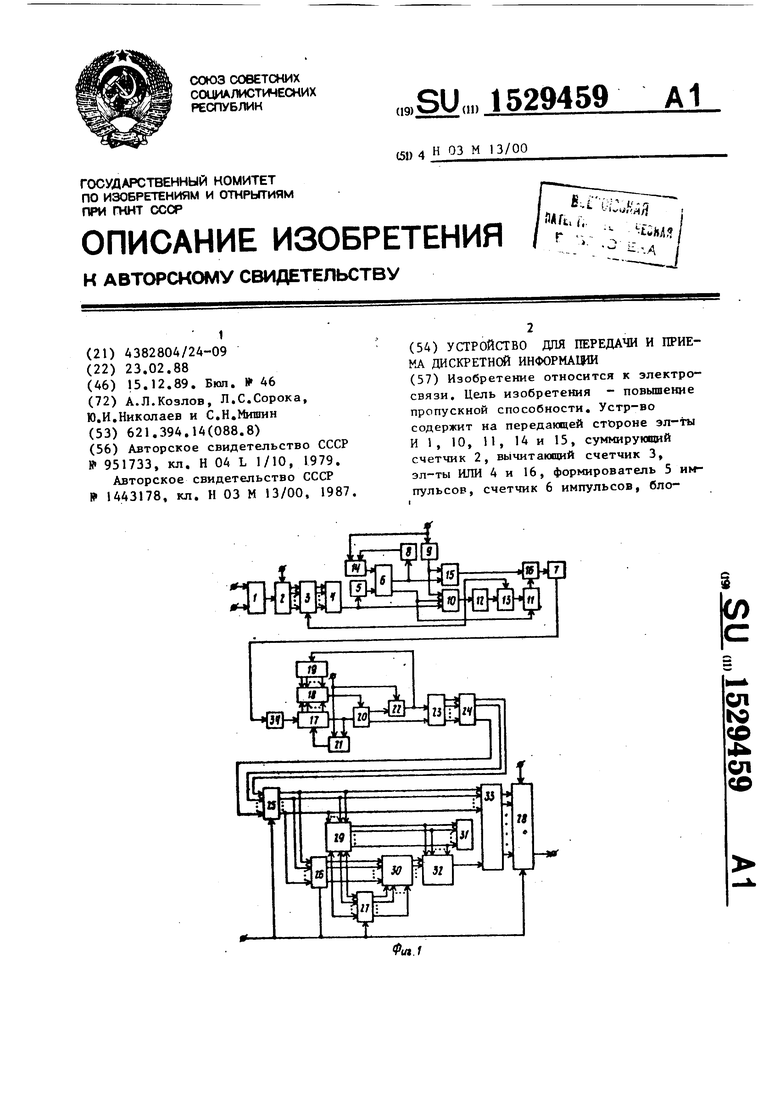

На фиг.1 представлена структурная электрическая схема устройства для передачи и приема дискретной информа- ции; на фиг.2 - временные диаграммы сигналов, поясняющие работу устройства для передачи и приема дискретной информации.

Устройство для передачи и прие1 а дискретной информации содержит на передающей стороне первый элемент И 1, суммирующий счетчик 2, вычитающий счетчик 3, первый элемент ИЛИ 4, фор- мирователь 5 импульсов, счетчик 6 импульсов, первый, второй и третий блоки 7-9 задержки, второй 10 и 4 третий 11 элементы К, генератор 12 псевдослучайной последовательности (ПСП), сумматор 13 по модулю два,четвертый 14 и пятый 15 элементы И,второй элемент Или 16, на приемной стороне - выделитель 17 псевдослучайной последовательности (ПСП), первый блок 18 сравнения, генератор 19 псевдослучайной последовательности (ПСП), RS-триггер 20, счетчик 21 импульсов, элемент И 22, суммирующий счетчик 23 накопитель 2А, перВЕз1й регистр 25 сдвига, третий регистр 26 сдвига, дополнительный регистр 27 сдвига, второй регистр 28 сдвига, первый 29 и второй 30 сумматоры, дополнительный блок 31 сравнения, второй блок 32 сравнения, кодопреобразователь 33. На фиг.1 представлен также канал 34 связи.

нал поступает на передающую сторону, где формируется кодовая последователь- ность, которая через канал 34 поступает на приемную сторону. Кроме того, на передающей стороне формируется маркерный импульс, сигнализирующий на приемную сторону о начале поступления очередной, следующей за ним, кодовой группы. Сигнал, преобразованный на приемной стороне, поступает на информационный выход устр-ва.2 ил.

Устройство для передачи и приема дискретной информации работает следующим образом.

Передаваемый дискретный сигнал (фиг.2а) поступает на информационный вход устройства для передачи и приема дискретной информации, т.е. на первый вход первого элемента И 1 (фиг.1). На второй вход последнего со считывающего входа устройства для передачи и приема дискретной информации поступает последовательность счетных импульсов (период следования которых равен С), показанная на фиг.2в. В произвольные относительно передаваемого дискретного сигнала моменты времени на опорный вход устройства для передачи и приема дискретной информации поступают импульсы опорной последовательности (фиг.2б), период следования которых Т должен быть меньще, чем минимальная длительность элемента передаваемого дискретного сигнала Т , т.е. . Причем период следования опорных импульсов Т, период следования счетных импульсов С и длительность Т связаны соотнощениями: Т (2 -1) t , Тд Т - 0,5 f , где m - число разрядов двоичного числа, определяющего количество стробирующих счетных импульсов периода О, формируемых за время Т, При этом в интервале времени между двумя опорными импульсами не может быть более одного фронта передаваемого дискретного сигнала, При поступлении опорного импульса на суммирующий счетчик 2 последний выдает информацию, которая была в нем записана, в вычитающий счетчик 3, а сам устанавливается в исходное состояние. При этом счетные импульсы

через первый элемент И I поступают на счетный вход суммирующего счетчика 2, если первый элемент И 1 открыт единичным потенциалом передаваемого дискретного сигнала.

При появлении комбинации, отличной от нулевой, в разрядах вычитающего счетчика 3 на выходе первого элемента ИЛИ 4 формируется- единичный сигнал, посредством которого на выходе формирователя 5 во время переднего фронта действия этого потенциала формируется короткий импульс,который переводит счетчик 6 в его предельное состояние. Состояния счетчика 6 уменьшаются при поступлении импульсов на его счетный вход. Счетчик 6 - двухразрядный, его выходы - это прямой и инверсный выходы его старшего разряда. Единичным потенциалом с прямого выхода c ieтчикa 6 открывается пятый элемент И 15. По тактовому входу устройства для передачи и приема дискретной информации поступают высокочастотные тактовые импульсы (ВТИ), длительность которых равна половине их периода следования t, который в 2 раз меньше длительности Т следования

10

опорных импульсов.

Первый импульс из последовательности ВТИ после перехода счетчика 6 в предельное состояние через пятый элемент И

мент ИЛИ 16 и первый блок 7 задержки выдается в канал 34 свя.зи. Этот импульс является маркером, сигнализирующим на приемную сторону о начале поступления очередной, следующей за ним, кодовой группы. Этот же импульс через четвертый элемент И 14 поступает на счетный вход счетчика 6 и переводит его в предельное состояние. Следующий за этим импульс переводит счетчик 6 в состояние, при котором на его прямом и инверсном выходах формируются нулевой и единичный соответственно потенциалы. Нулевой потенциал с прямого выхода счетчика 6 закрывает пятый элемент И 15 и через второй блок 8 задержки с временем задержки, равным времени срабатывания счетчика 6, также закрывает четвертый элемент И 14.

Время задержки третьего блока 9 задержки выбирается больше времени задержки второго блока 8 задержки и меньше половины периода t. Единичными

потенциалами с выхода первого элемента ИЛИ 4 и инверсного выхода счетчика 6 открывается второй элемент И 10, через который на тактовый вход генератора ПСИ 12 и счетный вход вычитающего счетчика 3 начинают поступать ВТИ до тех пор, пока вычитаюпшй счетчик 3 не установится в нулевое состояние, В этом случае подача ВТИ прекращается. Под действием этих ВТИ за время, не превышаю щее периода Т следования опорных импульсов, производится сдвиг фазы ПСП, J5 формируемой в генераторе ПСП 12, на число шагов, соответствующее числу счетных импульсов, поступающих на суммирующий счетчик 2. В сумматоре 13 и третьем элементе И 11 формируется кодовая группа биимпульсного кода, соответствующего коду, сформированному в генераторе ПСП 12, которая через второй элемент ИЛИ 16 и первый блок 7 задержки выдается в канале 34 связи сразу за маркерным импульсом.

Принимая с выхода канала 34 связи кодовую последовательность, выделитель ПСП I7 при наличии в принимаемой последовательности зачетного участка, не содержащего ошибок, определяет значение ее фазы, С выхода выделителя ПСП 17 сигнал устанавливает RS- триггер 20 в единичное состояние, что

20

25

30

40

приводит к открыванию элемента И 22,

15 и далее через второй эле- -, после чего с второго тактового входа устройства для передачи и приема

дискретной информации на вход суммирующего счетчика 23 и на вход генератора ПСП 19 начинают поступать ВТИ и производят сдвиг фазы принятой (предыдущей) ПСП относительно принимаемой. Сдвиг осуществляется до совпадения фаз указанных последовательностей. При зтом сигналом с выхода перво- дс го блока 18 сравнения RS-триггер 20 устанавливается в нулевое состояние. Сигналом с инверсного выхода RS-триг- гера 20 производится перезапись содержимого суммирующего счетчика 23 в накопитель 24, при этом сам суммирую- счетчик 23 обнуляется,

Суммирующий счетчик 23 осуществляет подсчет количества ВТИ, равного шагов сдвига фазы ПСП принятой последовательности относительно предыдущей. Счетчик 21 устанавливается в исходное состояние сигналом с фазирующего выхода выделителя ПСП 17, сигнализирующего о начале анализа

50

55

10

294596

потенциалами с выхода первого элемента ИЛИ 4 и инверсного выхода счетчика 6 открывается второй элемент И 10, через который на тактовый вход генератора ПСИ 12 и счетный вход вычитающего счетчика 3 начинают поступать ВТИ до тех пор, пока вычитаюпшй счетчик 3 не установится в нулевое состояние, В этом случае подача ВТИ прекращается. Под действием этих ВТИ за время, не превышаю щее периода Т следования опорных импульсов, производится сдвиг фазы ПСП, J5 формируемой в генераторе ПСП 12, на число шагов, соответствующее числу счетных импульсов, поступающих на суммирующий счетчик 2. В сумматоре 13 и третьем элементе И 11 формируется кодовая группа биимпульсного кода, соответствующего коду, сформированному в генераторе ПСП 12, которая через второй элемент ИЛИ 16 и первый блок 7 задержки выдается в канале 34 связи сразу за маркерным импульсом.

Принимая с выхода канала 34 связи кодовую последовательность, выделитель ПСП I7 при наличии в принимаемой последовательности зачетного участка, не содержащего ошибок, определяет значение ее фазы, С выхода выделителя ПСП 17 сигнал устанавливает RS- триггер 20 в единичное состояние, что

20

25

30

40

дс

дс

50

55

поступающей кодовой комбинации. После подсчета 2 на счетчика 21 формируется сигна ;, поступающий на дополнительный вход выделите- ля ПСП 17 и подгогавливагощий ei o к анализу очередной кодовой комбинации Время задержки в первом блоке 7 ta- держки выбирается таким,чтобы на при- емной стороне не было сбоев при ана- лизе очередной фазы ПСП из-за совпадения тактовых моментов определения фазы ПСП в выделителе ПСП 17 с поступлением ВТИ с второго тактового входа устройства для передачи и при- нма дискретной информации,

С второго опорного входа устройства для передачи и приема дискретной информации на его приемной стороне в произвольные моменты времени относительно времени действия опор)1ых импульсов на передающей стороне поступают импульсы опорной последовательности периода Т. По (1-1)-му опорно- му импульсу информация перезаписывается из накопителя 24 в первый регистр 25, Следующая кодовая группа аналогично по i-му опорному импульсу запи-сывается из накопителя 24 в пер- вый регистр 25, а предыдущая кодовая комбинация из первого регистра 25 перезаписывается в третий регистр 26 Очередная кодовая группа по (1+1)-му опорному импульсу заг1исывается i3

накопителя 24 в ггервый регистр 25 сдвига, а двв-IIpeд, кодовые комбинации ан;1логично перезаписываются , в третий и дополнительный регистры 26 и 27, Тактовые входы первого и тре- тьего регистров 25 и 26 выполнены задержанными, причем задержка у первого регистра 25 больше, чем у третьего регистра 26,, Это позволяет без сбоев перезаписывать информацию,

хранящуются в предыдущем регистре, в Последующие регистры. Таким образом, в первом, третьем и дополнительном регистрах 25-27 хранятся соответственно соседние тройки чисел Sj,, S - и S ;+,, равные числу щагов сдвига фаз ПСП по (i-1), i и (i+l) опорным интервалам соответственно. Первый и второй сумматоры 29, 30 осуществляют сложение чисел, хранящихся в первом и третьем регистрах 25, 26 и третье - и дополнительном регистрах 26, 27 соответственно, т.е, (Sj,+ S ) и

(S , + S :,,).,

/v/MijjiM i -льиый 31 сравнения осущеспшярт -равнение первой суммы

( Sj-l- Sj,,) с контрольным П

пос. 1

:- S ,-j., и располагается в начале (i+l)-ro опорного цикла кодирования, Ксли же указанная сумма не превышает числа п, то проверяется выполнение услэвия (S., + S.) 7 (S. -I- S i,), вслс дствие чего в случае выполнения этого условия делается вывод, что на передающей стороне во время (i+l)-го опорного цикла кодирования передавалась нулевая посылка длительностью Тпвс.о причем (n-S 1, -0,5) 1} Я noc,o(ri-S j, +0,5) t , а на приемной стороне восстанавливается эта посыпка длительностью . о (п- -S 14.,) и распопагается в начале (i+l)-го опорного цикла кодирования

Комбинации, нолучаемые в кодопреобразователе 33, перезаписываются во вт орой регистр 28 по опорному им-

пульсу, посту яюш.сму на чадержльнь Й тактовый вход второго регистра 28. Разрядность второго регистра 28 рчв- на 2 . Информаци ; из кодопреобрачо- вателя 33 йо второй регистр 28 запн- сь/хзаетсл ц парйллельном коде в пер

т 1

вые i - . его разрядов, а считывается эта инф(-и-м,1гтия с последнего

разряда второго регистра. 28 в последовательно : коде посредством считывающих импульсов периода С , поступающих на считывающий вход второго регистра 28 с второго считывающего входа устройства для .передачи и прие ма дискретной информации.

В качестве примера рассмотрим случай передачи исходного дискретного сигнала, изображенного на фиг.2а. Для m 2 временные диаграммы следования опорных и счетных импульсов представлены на фиг.2б и 2в соответственно. На фиг.2г изображены пачки счетных импульсов, поступающих на счетный вход суммирующего счетчика 2 после первого элемента И 1, и соответствующие этим пачкам импульсов кодовые 1 руппы, считываемые из суммирующего счетчика 2 и вычитающий счетчик 3 за соответствующие интервалы кодирования длительностью Т. Далее допустим, что на приемной стороне при раскодировании указанного дискретного сигнала анализ начат в момент времени t (фиг,2д). При этом в мо- мент времени t , в первый регистр 25 будет считана комбинация 117, соответствующая интервалу (to,t,), из накопителя 24. В момент времени t в третьем регистре 26 будет записана комбинация 1П, а в первый регистр 25 запишется следующая комбинация 01 , При этом дополнительный блок 31 сравнения выработает ро время интервала (t,t) сигнал 1 (фиг.2д), так как сумма числа 5, U, соответствующего комбинации ч117, и S 2 1 соответствующего комбинации 017, превышает число п 3. В следующий момент времени t в дополнительном регистре 27 будет перезаписан., комбинация 11, в третьем регистре 26 - комбинация 01, в первом, регистра 25 будет присутствовать комбинация «С 01, соответствующая интервалу (t .,t j). При этом апалогичнь;м 1)бразом дополнительный блок 31 срл г1нения выработает во время интерна.г1а сигнал 0 (фиг .2д) , так как сумма чисел S , 5 1 +

0

5

не превышает п 3. Второй блок 32 сравнения выработает во время интервала (t2,tj) сигнал О (фиг.2е), так как сумма чисел 5., 3 и J превьпиает сумму чисел S 1 и Sj 1. Вследствие этого кодопреобразователь 33 согласно описанному выпю его алгоритму вырчботает комбинацию (фиг.2ж), которая перезапишется в момент времени t, во второй регистр 28, откуда -считается через интервал времени С (так как второй регистр 28 при m 2 - четырехразрядный) с поспеднего разряда второго регистра 28 на информационньш выход для передачи и приема дискретной информации устройства. Кодовые комбинации, записываемые во второй регистр 28 в 0 моменты времени L . и соответствующая им огибающая двоичного дискретного сигнала также приведены на фиг,2ж и 2з соответственно.

25 Формула изобретения

0

0

5

0

5

Устройство для передачи и приема дискретной информации, содержащее на передающей стороне последовательно соеди}1енньге первый элемент И, суммирующий счетчик, вычитающий счетчик, первьм элемент И.ПИ, второй элемент И, генератор ПСП, сумматор по модулю два, третий элемент И, второй элемент ИЛИ и первый блок задержки, последовательно соединенные второй блок задержки, четвертый элемент И, счетчик импульсов TI пятый элемент И, выход которого подсоединен к второму входу второго элемента ИЛИ, а также третий блок задержки и формирователь импульсов, вход и выход которого подключены соответственно к выходу первого элемента ИЛИ и устанавливающему входу счетчика импульсов, инверсный выход которого подсоединен к вторым входам второго и .третьего элементов И, прямой выход счетчика импульсов подсоединен к входу второго блока задержки, вюрой вход Четвертого элемента И подключен к входу третьего блока задержки, выход которого подсоединен к второму входу пятого элемента И и третьему входу второго элемента И, выход которого подсоединен к счетному входу вычитающего счетчика и второму входу сумматора по модулю два, причем первый и второй входы первого элемента И, опорный вход суммирующего счетчика, вход третьего блока задержки и выход первого блока задержки являются соответственно информационным входом, пер- вым считывающим входом, первым опорным входом, первым тактовым входом и канальным выходом устройства, на приемной стороне - последовательно соединенные счетчик импульсов, вы- делитель псевдослучайной последовательности, RS-триггер, элемент И, суммиругаций счетчик, накопитель, первый регистр сдвига, кодопреобразователь и второй регистр сдвига, последовательно соединенные генератор псевдослучайной последовательности и первый блок сравнения, вторые входы которого подключены к соответствующим информационным выходам вьщелителя (ПСП), а также третий регистр сдвига и второй блок сравнения, выход которого подсоединен к соответствующему входу кодопреобраэо зователя, считывающий вход суммирующего счетчика подключен к инверсному входу RS-триггера, R-вход которого подключен к выходу первого блока сравнения, вход генератора псевдо .случайной последовательности подключен к выходу элемента И, второй вход которого подзспючен к счетному входу счетчика импульсов, устанавливающий вход которого подключен к фазирующему выходу выделителя псевдослучайной последовательности, а тактовый вход первого регистра сдвига объединен с

та: тС Е-),1м ( ;чж кодопреобразователя, причем информационный вход выделителя псевдослучайной последовательности, второй Еход элемента И, считывающий вход и выход второго регистра сдвига являются соответственно канальным входом, вторым тактовым входом, вторым считывающим входом и информационным выходом устройства, отличающееся тем, что, с целью повыщения пропускной способности, на приемной стороне введены последовательно соединенные первый сумматор и дополнительный блок сравнения, выход которого подсоединен к соответ- ствукщему входу кодопреобразователя, последовательно соединенные дополнительный регистр сдвига и второй сумматор, при этом первые входы первого сумматора и информационные входы третьего регистра сдвига подключены к соответствующим выходам первого регистра сдвига, тактовый вход которого объединен с тактовьпчи входами третьего и дополнительного регистров сдвига, выходы третьего регистра сдвига подсоединены к соответствующим информационным входам дополнительного ре- . гистра сдвига и соответствующим вторым входам первого и второго сумматоров , выходы которых подсоединены соответственно к соответствующим первым и вторым входам второго блока сравнения, причем тактовый вход первого регистра сдвига является вторым опорным входом устройства.

И

I I I .

ж1

I I I

о 7 i; 7 loofliJ 7j 7iJ4 jP7;jj LeiMjliij L

LLXLf

0i/e.Z

| Устройство для передачи и приема дискретной информации | 1981 |

|

SU951733A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-02-23—Подача