1 . 1

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации.

Целью изобретения является повышение скорости передачи информации пу- тем уменыйения длины кодового слова.

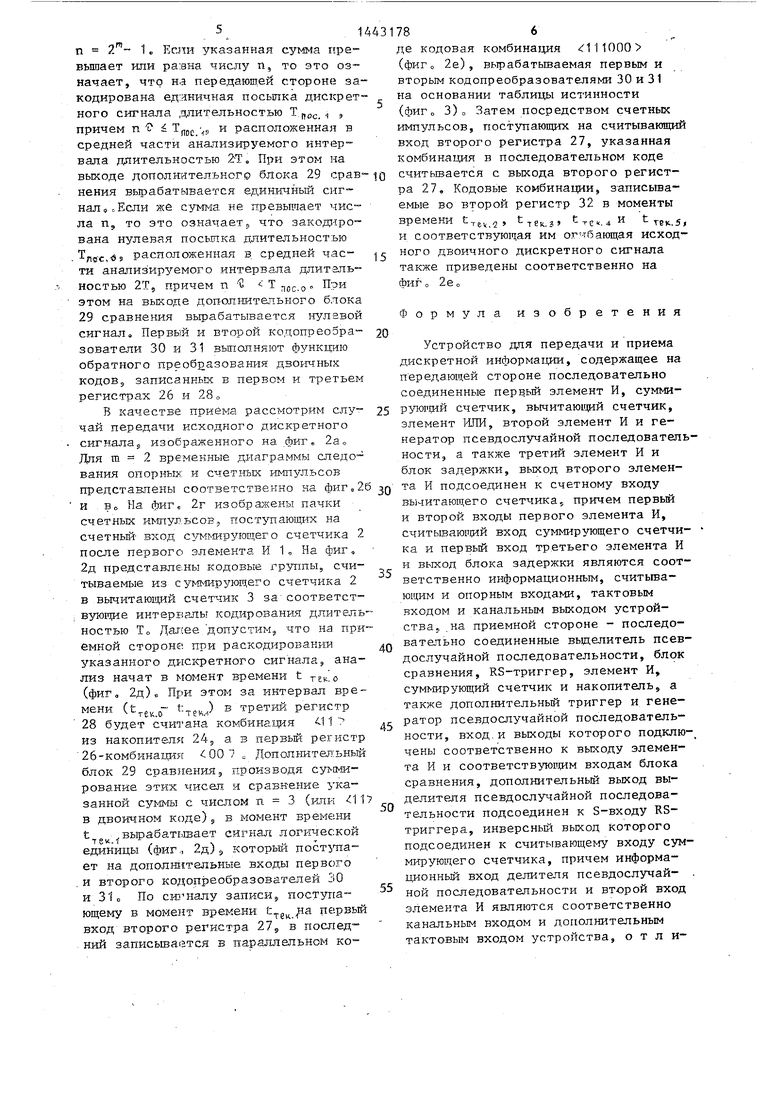

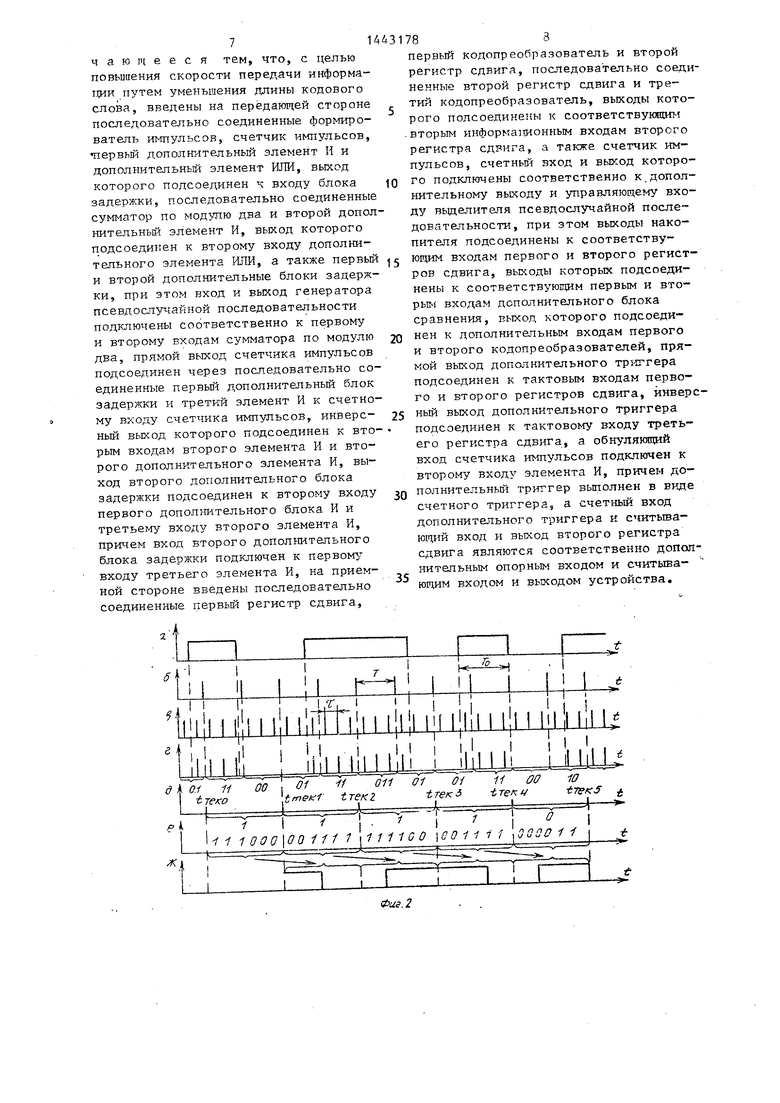

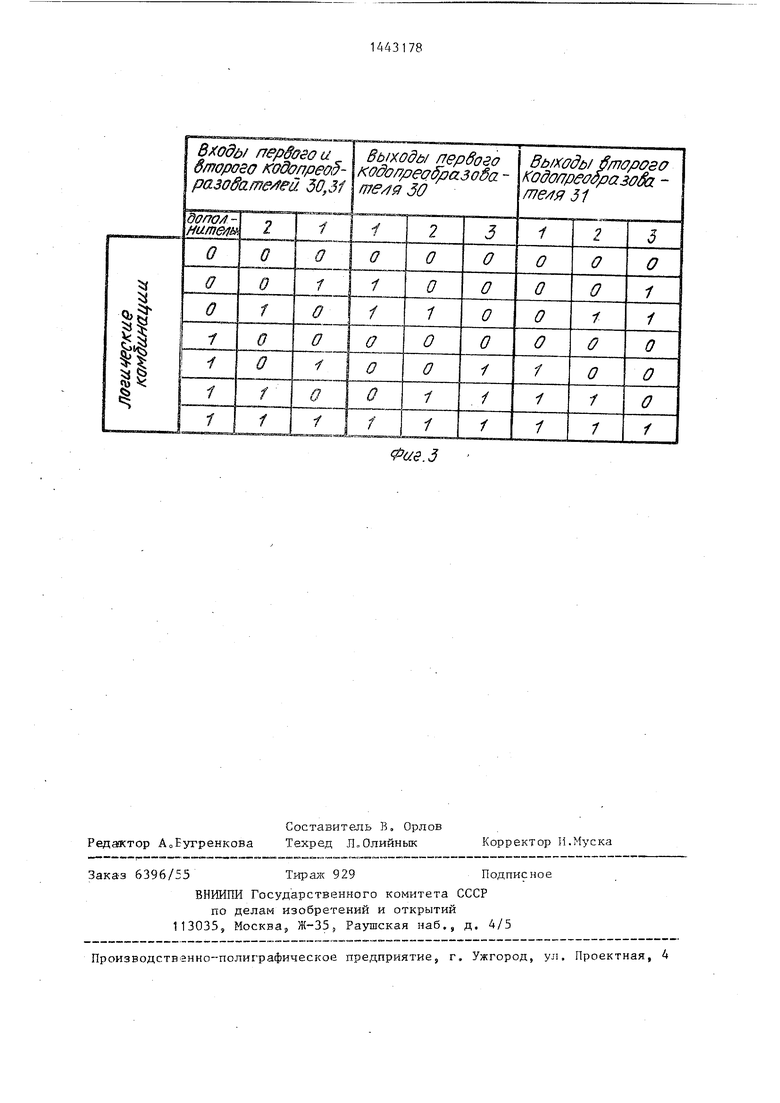

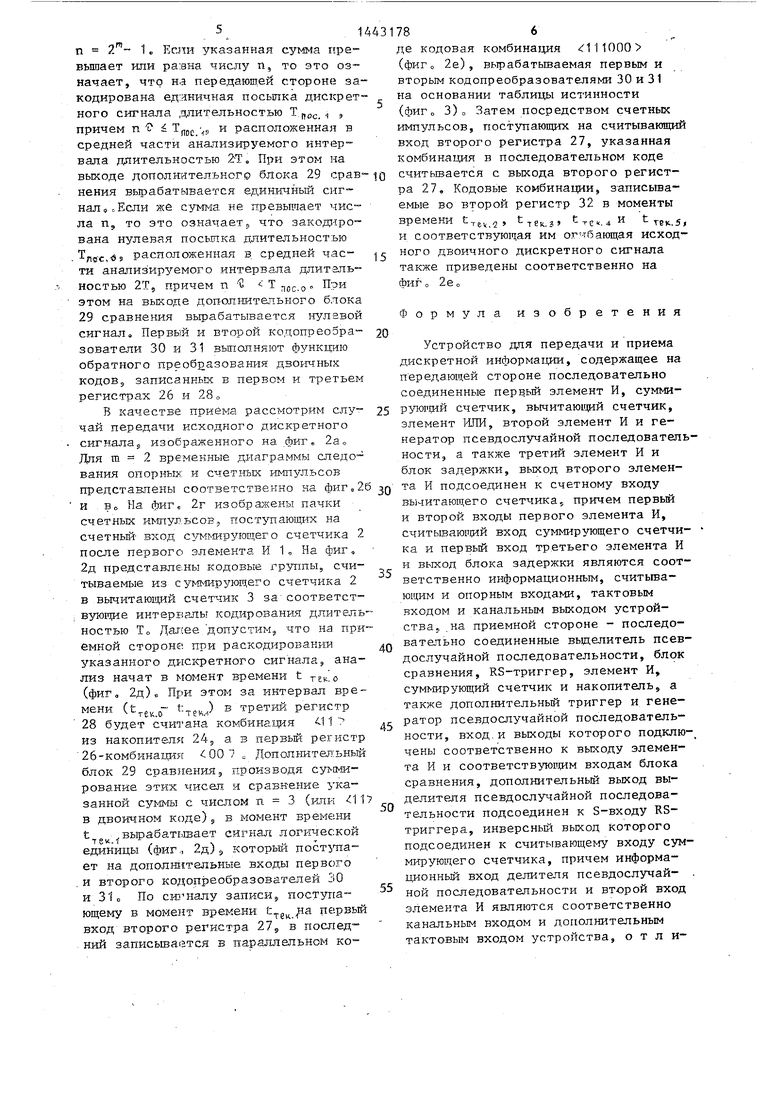

На фиг, 1 представлена структурная электрическая схема устройства для передачи и приема дискретной ин™ формацииf на фиг 2 -- временные диаграммы сигналов, поясняющие работу устройства для передачи и приема дискретной информации; на фиг 3 - таб опица истинности,

Устройство для передачи к приема дискретной информации содержи-т на передающей стороне первьй элемент И 1, суммирующий счетчик 2, вычитающий .счетчик Зд элемент ИЛИ 4, фор- мирователь 5 импульсов,, счетчик 6 импульсов, блок.7 задержки первьй и второй дополнительные блоки 8 и 9 задержки, второй и третий элементы И 10 и 11, генератор 12 псевдослу- чайной последовательности (ПСП), сумматор 13 по модулю два, первый и второй дополнитальные элементы И 14 и 15, дополнительньй элемент ИЛИ 16, на приемной стороне выделитель 17 пселдослучайной последовательности блок 18 сравнения5 генератор 19 ПСП. КЗ-триггер 20э счетчик 21 импульсов, элемент И 22, суммирующий счетчик 23, накопитель 24, дополнительный триггер 25, первьй, второй и третий ре гистры 26-28 сдвига, блок 29 сравнения, первый и второй кодопреобразователи 30 и 31 о

На фнг. 1 также представлен канал 32 связи.

Устройство для передачи и приема дискретной информации работает следующим образомо

Передаваемьй дискретньй сигнал (фиг о 2а) поступает на информационный вход ус ройства для передачи и приема дискретной информации (фиг,1) т.е. на перзьй вход первого элемента И 1 На второй вход последнего со считьшающего входа устройства для передачи и приема дискретной информации поступазт поспедовательность счетных импульсов5 период следования которых D показан/ на фиг, 2во В произвольные относительно передаваемого дискретного сигнала моменты времени на опорный вход устройства для передачи и приема дискретной информации по

2

ступают и1-тульсы опорной последовательности (фиг. 26), период следования которых Т должен быть меньше, чем минимальная длительность элемента передаваемого дискретного сигнала

т„.е Т Т„

Причем период следоJQ15

20 25 ЗО

35

0

5

вания опорных импульсов Т, период следования счетных импульсов С и длительность Т о связаны соотношениями Т (2 - 1) То Т + Т + 1}, где./тг- число разрядов двоичного числа, определяющего количество стрсбирующих импульсов периода , фор1 гируемых за время Т, При этом в интервале времени между двумя опорными импульсами не может быть более одного фронта передаваемого дискретного сигнала. При поступлении опорного импульса на сум- шpyюl ий счетчик 2 последний вьщает информацию, которая была в нем записана, в вычитaюllJ5iй счетчик 3, а сам устанавливается в исходное состояние. При этом счетные импульсы через первый элемент И 1 поступают на счетньй вход суммирующего счетчика 2, если первый элемент И 1 открыт единичньш потенциалом передаваемого дискретного сигнала.

При появлении комбинации, отличной от нулевой, в разрядах вычитающего счетчика 3 на выходе элемента ИЛИ 4 формируется единичньй сигнал, посредством которого на выходе форми роватапя 5 во время переднего фронта действия этого потентщала формируется короткий импульс, который переводит счетчик 6 в его предельное состояние Состояния счетчика 6 уменьшаются при поступлении импульсов на его счетный вход Единичным потенциалом с прямого вькода счетчика 6 открывается первьй дополнительньй элемент И 14о По тактовому входу устройства для передачи и приема дискретной информации поступают высокочастотные тактовые импульсы (ВТИ)., длительность которых равна половине их периода следования t, который в (п+1) раз меньше длительности Т наименьшего по длительности элемента передаваемого дискретного сигнала.

Первьй импульс из последовательности ВТИ после перехода счетчика 6 в предельное состояние через первьй дополнительньй элемент И 14 и далее через дополнительньй элемент ИЛИ 16 и блок 7 задержки выдается в канал 32 связи. Этот импульс является мар314А31

кером, сигнализирующим (приемную сторону) о начале поступления очередной, следующей за ним, кодовой группы, Это- же импульс через третий элемент И 11 поступает на счетный вход счет- чика 6 и переводит его в предпредель- ное состояние. Следующий за этим импульс переводит счетчик 6 в состояние, при котором на его прямом и IQ инверсном выходах формируются соответственно нулевой и единичный потенциалы Нулевой потенциал с прямого выхода счетчика 6 закрывает первый дополнительный элемент И 14 и через 15 первый дополнительный блок 8 задержки с временем задержки, равньш времени срабатывания счетчика 6, также за-, крывает третий элемент И 11.

Бремя задержки второго дополни- 20 тельного блока 9 задержки выбирается больше времени задержки первого дополнительного блока 8 задержки и меньше половины периода tj,. Единичными потенциалами с выхода элемента 25 ИЛИ 4 и инверсного выхода счетчика 6 , открывается второй элемент И 10, через которьй на тактовый вход генератора 12 и на счетный вход вычитающего счетчика 3 начинают поступать ВТИ зо до тех пор, пока вычитающий счетчик 3 не устанавливается в нулевое состояние. В этом случае подача ВТИ прекращается Иод действием этих ВТИ за время, не превышающее периода Т еле- ,jg дования опорных импульсов, производится сдвиг фазы ПСП, формируемой в генераторе 12, на число шагов, соответствующее числу счетных импульсов, поступаюш;их на вход суммирующего 40

счетчика 2. В сумматоре 13 и втором дополнительном элементе.И 15 формируется кодовая группа биимпульсного кода, соответствующего коду, сформированному в генераторе 12, которая 45 через дополнительный элемент РШИ 16 и блок 7 задержки вьздается в канал 32

связи сразу за маркерным импульсом.

Принимаемая с выхода канала 32 связи последовательность поступает на gQ вьделитель ПСП 17, При наличии в принимаемой последовательности зачетного участка, не содержащего ошибок, с помощью вьщелителя 17 ПСП определяется значение ее фазыо С выхода вьщелите- gg ля 17 ПСП сигнал устанавливает RS- триггёр 20 в единичное состояние, что приводит к открьшанию элемента И 22, после чего с дополнительного тактово78 .

го выхода устройства для передачи и приема дискретной информации на вход суммирующего счетчика 23 и на вход генератора 19 начинают поступать ВТИ и производят сдвиг принятой (пре- дьщущей) ПСП относительно принимаемой Сдвиг осуп;ествляется до совпадения фаз указанных последовательностей При этом сигналом с выхода блока 18 сравнения RS-триггер 20 устанавливается в нулевое состояние. Сигналом с инверсного выхода Р RS- триггера 20 производится перезапись содержимого суммирующего счетчика 23 в накопитель 24,

Суммирующий счетчик 23 осуществляет подсчет каждых (п+1) ВТИ, что эквивалентно определению конца интервала анализа кодовой комбинации в выделителе 17 ПСПо Счтетчик 21 устанавливается в исходное состсяние сигналом с дополнительного выхода вьдели- теля 17 ПСП, сигнализирующего о начале анализа поступающей кодовой комбинации. После подсчета (п+0 ВТИ на выходе счетчика 21 формируется сигнал, поступающий на управляющий вход вьщелитачя 17 ПСП и подготавливакиций его к анализу очередной кодовой комбинации,

С дополнительного опорного входа устройства для передачи и приема дискретной информации на его приемной стороне в произвольные моменты времени относительно времени действия опорных импульсов на передающей стороне поступают импульсы опорной последовательности с периодом Т, Каждый такой импульс поступает на счетный вход дополнительного триггера 25 (яв- лякнцегося счетным триггером). Для раскодирования принимаемых комбинаций и принятия решения о полярности передаваемого сигнала анализируются по две следуюпще друг за другом кодовые группы, Теку1цая кодовая группа из накопителя 24 по импульсу записи, поступающему с инверсного выхода дополнительного триггера 25 на третий регистр 28, записывается в последний Следующая кодовая группа аналогично по импульсу записи, поступающему с прямого выхода дополнительного триггера 25, записьшается в первый регистр 26. Дополнительный блок 29 срар нения суммирует числа, записанные в первом и третьем регистрах 26 и 28, и указанную сумму соавнивает с число

n 2 1 „ Екпи указанная сумма пре- вьшает или равна числз j то это означает, что на передающей стороне закодирована единичная посыпка дискретного сигнала .длительностью Т „о,, , причем n TfiDC. расположенная в средней части анализируемого интервала длительностью 2-Т, При этом на выходе дополнительного блока 29 срав нения вырабатывается единичньш сигнал,. Если же сумма не лревыиает числа п, то это означает,, что закодирована нулевая посылка длительностью ., расположенная в. средней части анапизирз емого интерва,ла ностью 2Т,, причем n 2 Т /.о этом на выходе дополнительного блока 29 сравнения вырабатывается нулевой сигнал Первьш и второй кодопреобразователи 30 и 31 выполняют функцию обратного преобразования двоичных кодоВэ записанных в первом и третьем регистрах 26 и 28

В качестве приема рассмотрим случай передачи исходного дискретного сигнала изображенного на .фиг, 2ао Для m 2 временные диаграммы следования опорных и счетных импульсов представлены соответственно на фиг,2 и Во На фиг, 2г изображены пачки счетных импульсов, поступающих на счетньй- вход с тммирующего счетчика 2 после первого элемента И 1 ,, На фиг,. 2д представлены кодовые группы, считываемые из суммирующего счетчика 2 в вычитающий счетчик 3 за соответствующие интервалы кодирования длительностью То Далее допустим, что на приемной стороне при раскодировании указанного дискретного сигнала, анализ начат в момент времени t тек о (фиг, 2д)6 При этом за интервал времени (t t;) в третий регистр 28 будет считана комбиназдия 11 Т

из накопителя 24, а з первьй регистр 26-комбинация -С00 7 Дополнительный блок 29 сравнения, производя суммирование этих чисел и сравнение указанной суммы с числом n 3 (или в двоичном коде)g в момент времени вырабатьшает сигнал логической единицы (фиг, 2д) э который постз па- ет на дополнительные входы первого и второго кодопреобразователей 30 и 31 о По сш налу записи5 поступающему в моиез1т времени пефвый вход второго регистра 275 последний записьюается в параллельном ко5

0

3

Q

5

0

5

0

5

0

5

1786

де кодовая комбинатдия ГИООО (фиг о 2е), вырабатьшаемая первым и вторым кодопреобразователями 30 и 31 на основании таблицы истинности (фиг о 3)о Затем посредством счетных импульсов, поступающих на считывающий вход второго регистра 27, указанная комбинация в последовательном коде считьшается с выхода второго регистра 27, Кодовые комбинации, записываемые во второй регистр 32 в моменты

времени t тек.з С..и t ,5, и соответствующая им ог -тбающая исходного двоичного дискретного сигнала также приведены соответственно на фиг о 2ео

Формула изобретения

Устройство для передачи и приема дискретной информахщи, содержащее на передающей стороне последовательно соединенные первый элемент И, сумми- руюгтй счетчик, вьмитаюидий счетчик, элемент ЮТИ, второй элемент И и генератор псевдослучайной последовательности, а также третий элемент И и блок задержки, выход второго элемента И подсоединен к счетному входу вычитающего счетчика, причем первьй и второй входы первого элемента И, считьюаюр ий вход суммирующего счетчика и первый вход третьего элемента И и выход, блока задержки являются соответственно информационным, считьгеа- Ю1ЦИМ и опорным входами, тактовым входом и канальным выходом устройства., на приемной стороне - последовательно соединенные выделитель псевдослучайной последовательности, блок сравнения, RS-триггер, элемент И, суммирующий счетчик и накопитель, а также дополнительньй триггер и генератор псевдослучайной последовательности, вход.и выходы которого подклю- чены соответственно к выходу элемента И и соответствуювщм входам блока сравнения, дополнительный выход выделителя псевдослучайной последовательности подсоединен к S-входу RS- триггера, инверсный выход которого подсоединен к считывающему входу суммирующего счетчика, причем информа- ционньй вход делителя псевдослучай- . ной последовательности и второй вход элемента И являются соответственно канальным входом и дополнительным тактовым входом устройства, о т л и71

чающееся тем, что, с целью повышения скорости передачи информа- исии путем уменьшения длины кодового слова, введены на передающей стороне последовательно соединенные формирователь импульсов, счетчик импульсов, «первьй дополнительный элемент И и дополнительный элемент ИЛИ, выход которого подсоединен к входу блока задержки, последовательно соединенные сумматор по модулю два и второй дополнительный элемент И, выход которого подсоединен к второму входу дополнительного элемента Ш1И, а также первый и второй дополнительные блоки задержки, при этом вход и выход генератора псевдослучайной последовательности подключены соответственно к первому и второму входам сумматора по модулю два, прямой выход счетчика импульсов подсоединен через последовательно соединенные первьй дополнитепьньй блок задержки и третий элемент И к счетному входу счетчика импульсов, инверсный выход которого подсоединен к вторым входам второго элемента И и второго дополнительного элемента И, выход второго дополнительного блока задержки подсоединен к второму входу первого дополнительного блока И и третьему входу второго элемента И, причем вход второго допол ттельного блока задержки подключен к первому входу третьего элемента И, на приемной стороне введены последовательно соединенные первый регистр сдвига.

r

0

5

0

5

1788

первый кодопреобразователь и второй регистр сдвига, последовательно соединенные второй регистр сдвига и третий кодопреобразователь, выходы которого подсоединены к соответствуюидп- .вторым информа1.шонным входам второго регистра сдвига, а также счетчик импульсов, счетный вход и выход которого подключены соответственно к,дополнительному вькоду и управляющему входу вьщелителя псевдослучайной последовательности, при этом выходы накопителя подсоединены к соответствующим входам первого и второго регистров сдвига, выходы которых подсоединены к соответствующим первым и вторым входам дополнительного блока сравнения, выход которого подсоединен к дополнительным входам первого и второго кодопреобразователей, прямой выход дополнительного подсоединен к тактовым входам первого и второго регистров сдвига, инверсный выход дополнительного триггера подсоединен к тактовому входу третьего регистра сдвига, а обнулякяций вход счетчика импульсов подключен к второму входу элемента И, причем дополнительный триггер выполнен в виде счетного триггера, а счетный вход дополнительного триггера и считьта- ющий вход и выход второго регистра сдвига являются соответственно дополнительным опорным входом и считыва- ющим входом и выходом устройства.

Фае.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для передачи и приема дискретной информации | 1985 |

|

SU1298942A2 |

| Устройство для передачи и приема дискретной информации | 1976 |

|

SU642867A1 |

| Устройство для передачи и приема дискретной информации | 1981 |

|

SU951733A1 |

| Система для передачи и приема дискретной информации | 1980 |

|

SU886296A1 |

| Устройство для передачи и приема дискретной информации | 1981 |

|

SU1027838A1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

Изобретение относится к электро- связио Цель изобретения - повышение скорости передачи информа1даи. Устр- во содержит на передающей стороне. эл-ты И 1, 10, 11, 14 и 15, суммиру- Ю1 1ий и BbrqHTaKiiipiH счетчики 2 и 3, эл-ты ИЛИ 4 и 16, формирователь 5 импульсов, счетчик 6 импульсов, блоки задержки 7, 8 и 9, г-р 12 псевдослучайной последовательности (ПСП) ,и сумматор 13 по модулю два. На приемной стороне устр-во содержит вьдели- тель 17 ПСП, блоки .сравнения 18 и 29, г-р 19 ПСП, RS-триггер 20, счетчик 21 импульсов, эл-т И 22, суммирукндий счетчик 23, накопитель 24, триггер 25, регистры 26, 27 и 28 сдвига, кодопреобразователи 30 и 31 и канал связи 32. Цель достигается путем уменьшения длины кодового слова 3 ил, (С (Л 00 Ч 00

| Устройство для приема трехкратно повторяемых команд управления | 1979 |

|

SU873436A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для передачи и приема дискретной информации | 1981 |

|

SU951733A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-13—Подача