(54) РЕГИСТР СДВИГА

гера последующего разряда, шина записи подключена к R-входу первого RS-триггера первого разряда, щины управления - к.выходам вторых инверторов, шина заполнениярегистра - к инверсному выходу второго RSтриггера первого разряда, шина наличия данных в регистре - к инверсному выходу второго RS-триггера последнего разряда, к одному из входов которого подключена шина считывания, а к другому - шина сброса. При таком построении регистра сдвиговые импульсы формируются элементами регистра, а перенос осуществляется асинхронно со скоростью, определяемой быстродействием элементной базы регистра, скорость поступления данных может приближаться к скорости переноса в регистре. Запись данных и считывание их в регистре независимы, что позволяет производить одновременно операции записи и считывания.

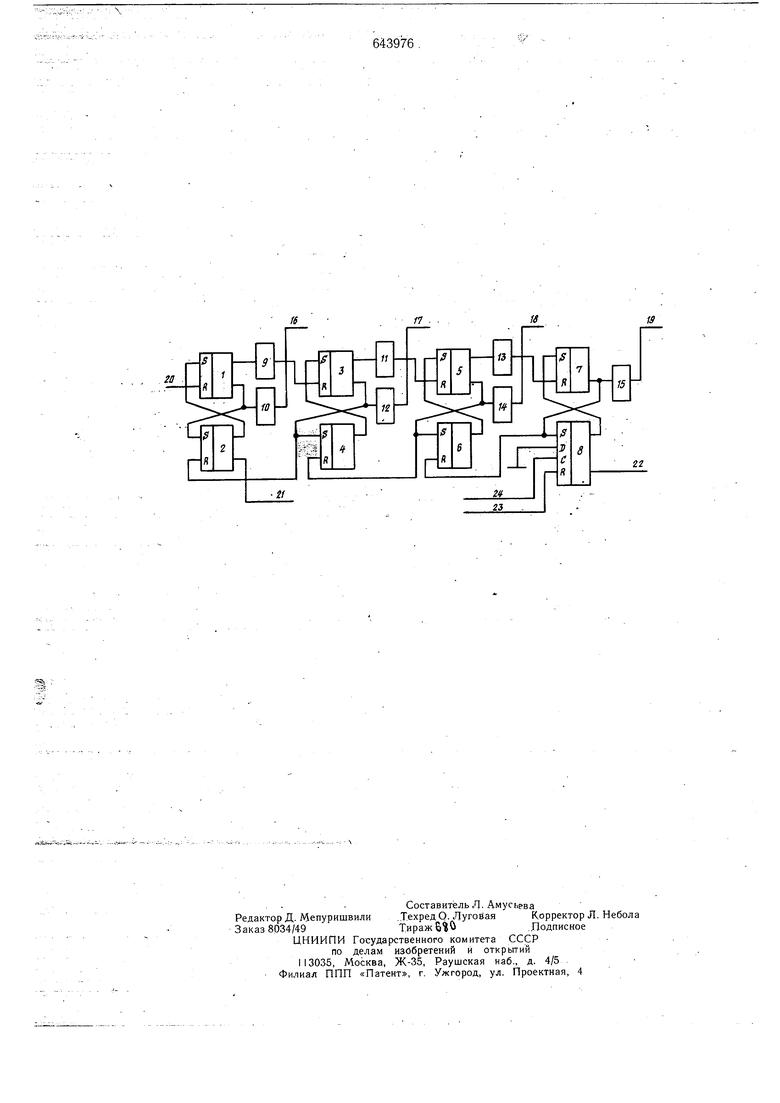

Работа предлагаемого регистра рассматривается на примере 4-разрядного регистра сдвига, схема которого приведена на чертеже.

Схема содержит RS-триггеры 1;-8 , инверторы 9:-15, щины 16-19 управления, шину 20 записи в регистр, шину 21 заполнения регистра, шину 22 наличия данных в регистре, шину 23 обнуления регистра, шину 24 считывания данных.

RS-триггеры 1, 2 и инверторы 9, 10 образуют 1-й разряд (входной) регистра; RS-триггеры 3, 4 и инверторы 11, 12 образуют 2-й разряд регистра; .RS-Tpnrrepbi 5, 6 и инверторы 13, 14 - 3-й разряд; RS-триггеры 7, 8 и инвертор 15 образуют 4-й (выходной) разряд регистра. Шина 16 подключена на выход инвертора 10, шина 17 подключена на вбтход инвертора 12, шина 18 .подключена на выход инвертора 14, шина 19 подключена на выход инвертора 15, шина 20 подключена на R-вход RS-триггера 1, шина 21 подключена на инверсный выход RS триггера 2, шина 22 подключена на инверсный выход RS-триггера 8, шина 23 подключена на R-вход RS-триггера 8, щина 24на счетный вход RS-триггера 8, D-вход триггера 8 подключен к шине нулевого потенциала.

В исходном состоянии RS-триггеры 2, 4, 6, g сброшены. На шине 20 присутствует нулевой уровень. Нулевые уровни присутствуют на входах S и R триггеров 1, 3, 5, 7 и на обоих выходах этих триггеров присутствуют единичные уровни. На шинах 16-19 присутствуют нулевые уровни, т.к. на входы инверторов 10, 12, 14, 15 поступают единичные уровни. На шинах 21, 22, 23 присутствуют единичные уровни и на шине 24 нулевой уровень.

Сигнал записи единичного уровня поступает на шину 20 и RS-триггера 1 устанавливается в единичное состояние. Нулевым уров нем инверсного плеча RS-триггера 1 установится в единичное состояние-RS-Tpnrrep 2

и на управляющей щине установится единичный уровень. С прямого выхода RS-триггера 2 единичный уровень поступит на Sвход триггера 1. По окончании сигнала за пись RS-триггер 1 сбросится. На шине 16 установится нулевой уровень, а на выходе инвертора 9 установится единичный уровень, который поступает на R-вход RS-триггера 3. RS-триггер 3 установится в единичо ное состояние. С инверсного выхода RSтриггера 3 нулевым уровнем сбросится RSтриггер 2 и установится в единичное состояние RS-триггер 4. С прямого выхода RSтриггера 2 на S-вход триггера 1 поступит нулевой уровень и на прямом выходе триггера 1 установится единичный уровень, который поступит на вход инвертора 9. На выходе инвертора 9 установится нулевой уровень, который поступит на R-вход триггера 3 и сбросит его. Таким образом, на

- входе инвертора 12 будет присутствовать нулевой уровень, который поступает с инверсного плеча RS-триггера 3 в течение времени, длительность которого равна задержке на RS-триггерах 1, 2, 3 и инвертора 9. В течение этого времени на управляющей шине 17 будет присутствовать сигнал с - единичным уровнем. После сброса RS-триггера 3 на выходе инвертора 11 установится единичный уровень, который поступает на Rвход RS-триггера 5. RS-триггер 5 установится в„единичное состояние. С инверсного выхода RS-триггера 5 установится в единичное состояние RS-триггер 6 и сбросится RS-триггер 4. С прямого выхода RSтриггера 4 на вход RS-триггера 3 ноступит нулевой уровень. На прямом выходе RS-триг35 гера 3 установится единичный уровень, который поступит на вход инвертора 11. С выхода инвертора 11 на R-вход RS-триггера 5. поступит нулевой уровень и сбросит его. На время задержки сигнала на RS-триггерах 3, 4, 5 и инверторе 1I на входе инвертора 14 будет присутствовать нулевой уровень. В течение этого времени на управляющей шине 18 будет присутствовать сигнал единичного уровня. После сброса RS-триггера 5 На выходе инвертора 13 установится единичный уровень, который поступит на Rвход RS-триггера 7, RS-триггер 7 установится в единичное состояние. С инверсного выхода RS-триггера 7 нулевым уровнем установится в единичное состояние RS-триггер 8 и сбросится RS-триггер 6. С прямого выхода RS-триггера 6 на S-вход RS-триггера 5 поступит нулевой уровень. На прямом вь1ходе RS-триггера 5, установится единичный уровень, который поступает на вход инвертора 18. Нулевой уровень с выхода инвертора 13 поступит на R-вход RS-триггера 7

и сбросит его.

На время задержки на RS-триггерах 5, 6, 7 и инвертора 13 на входе инвертора 15 присутствует нулевой уровень. В течение этого времени на управляющей щине 19

будет .присутствовать сигнал единичного уровня.

RS-триггер 8 останется в единичном состоянии и на шине 22 установится нулевой уровень. При поступлении второго сигнала записи, цикл сдвига повторится-, но так как на S-входе RS-триггера 7 присутствует единичный уровень, сдвиг остановится на ячейке, образованной RS-триггерами 5, 6 и инверторами 13, 14, и RS-триггер 6 установится в единичное состояние, а управляющие сигналы сформируются поочередно на шинах 16, 17, 18. При поступлении третьего сигнала записи установится в.единичное состояние триггер 4, а управляющие сигналы сформируются на шинах 16, 17. При поступлении четвертого сигнала записи установится в единичное состояние триггер 2, а управляющий сигнал сформируется на шине 16. На шине 21 установится нулевой уровень - сигнал заполнения регистра.

При заполненном регистре вновь поступающие данные будут теряться.

Для поразрядного считывания с . регистра на шину 24 поступает сигнал единичного уровня, триггер 8 сбрасывается. На Sвход RS-триггера 7 поступит нулевой уровень и RS-триггер 7 устанавливается в единичное состояние. С инверсного выхода RSтриггера 7 нулевым уровнем RS-триггер 8 установится в единичное состояние и сбросится триггер 6. На S-вход триггера 5 поступит нулевой уровень и он установится в единичное состояние и соответственно на выходе инвертора 13 установится нулевой уровень, который поступит на R-вход триггеру 7. RS-триггер 7 сбросится, так как на еГо S-входе присутствует единичный уровень, поступающий с RS-триггера 8. На время задержки на RS-триггерах 5, 6, 7 и инверторе 13 на шине 19 будет присутствовать управляющий сигнал и произойдет сдвиг с третьей ячейки в выходную и на шине 22 установится нулевой уровень. С RSтриггера 5 нулевым уровнем с инверторного выхода RS-триггер 6 установится в единичное состояние, RS-триггер 4 сбросится. Аналогично на шине 18 сформируется управляющий сигнал, а затем управляющий сигнал сформируется на шине 1,7 и сбросится RS-триггер 2. На шине 21 установится единичный уровень. При каждом поступлении сигнала единичного уровня на шину 24 происходит сдвиг в регистре вправо, при

поступлении каждого четвертого единичного сигнала регистр обнуляется и на шине 22 устанавливается единичный уровень.

Для обнуления всего регистра используется шина 23.

Использование предлагаемого регистра сдвига позволяет получить следующие преимущества . перед использованием известных:а) увеличить скорости приема данных;

б)увеличить скорости переноса в регистре;

в)уменьщить количество и номенклатуру используемого оборудования;

г)производить одновременную запись и считывание данных с различным быстродействием.

Формула изобретения

Регистр сдвига, содержащий в каждом разряде два RS-триггера и два инвертора,

- щины записи, управления, считывания и сброса, отличающийся тем, что, с целью повышения быстродействия регистра и обеспечения возможности одновременной записи и

5 считывания, в нем вход первого инвертора каждого разряда регистра соединен с прямым выходом первого RS-триггера данного разряда, инверсный выход которого соединен с R-входом второго RS-триггера преды0 дущего разряда, с входом второго, инвертора и S-входом второго RS-триггера данного разряда, прядЮЙ выход которого соединен с S-входом первого RS-триггера, а выход первого инвертора данного разряда соединен с R-входом RS-триггера последующего разряда, шина записи подключена к Rвходу первого RS-триггера первого разряда, шины управления - к выходам вторых инверторов, шина заполнения регистра - к инверсному выходу второго RS-триггера первого разряда, шина наличия данных в регистре - к инверсному выходу второго RS-триггера последнего разряда, к одному из входов которого подключена шина считывания, а к другому - шина сброса. Источники информации, принятые во вни5 мание при экспертизе

1.Авторское свидетельство СССР № 432602, кл. G 11 С 19/00, 19.09.72.

2.Авторское свидетельство СССР Хо 503296, кл. G И С 19/12, 22.03.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| Устройство для программного управления | 1987 |

|

SU1596307A1 |

| Устройство разделения и синхронизации сигналов | 1984 |

|

SU1211863A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Цифровой измеритель длительности периода | 1988 |

|

SU1582176A1 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сложения | 1981 |

|

SU968809A1 |

| Делитель частоты следования импульсов с программным управлением | 1979 |

|

SU873416A1 |

| Устройство для задержки импульсов | 1976 |

|

SU663094A1 |

Авторы

Даты

1979-01-25—Публикация

1976-10-18—Подача