(5) УСТРОЙСТВО ЛЛЯ СЛОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Накапливающий счетчик | 1981 |

|

SU1001481A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

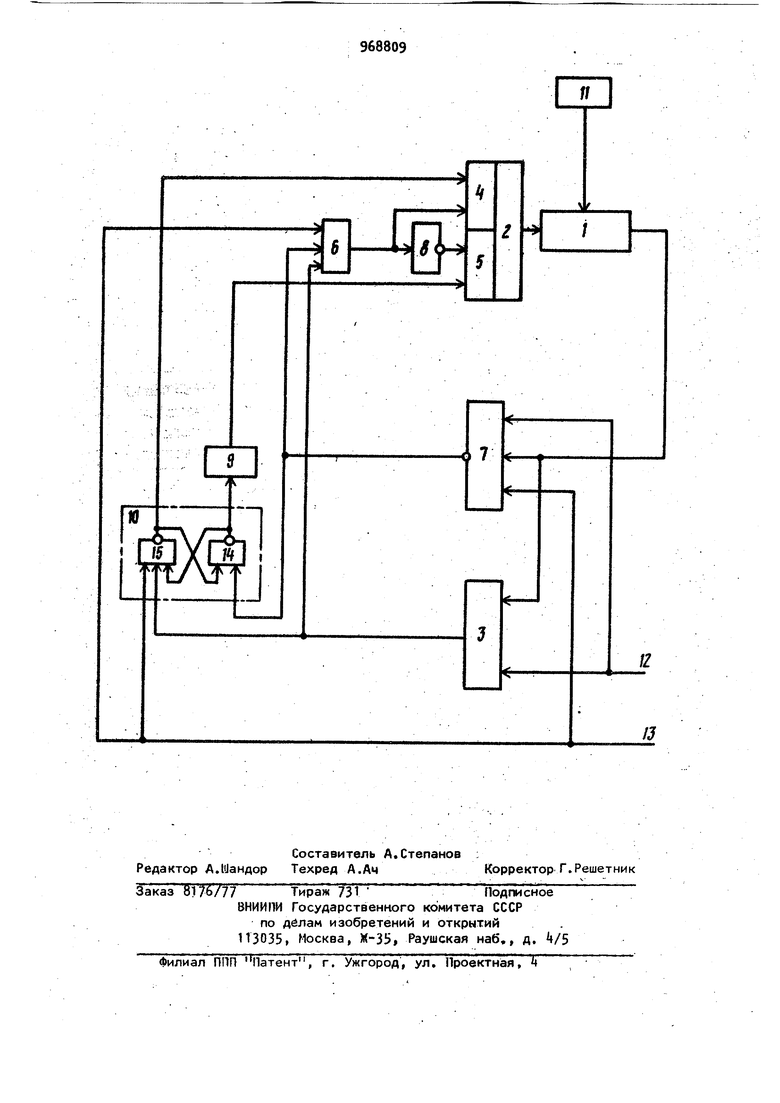

Изобретение относится к вычислительной технике и может быть исполь зовано в арифметических устройствах ЭВМ. Известно устройство для сложения содержапее два регистра сдвига, триггер, четыре элемента И, два эле мента ИЛИ, элемент НЕ и два элемента задержки 1}. Недостатком устройства является сложность конструкции. Известно также устройство для сложения, содержащее два регистра сдвига, триггер, два элемента И, дв элемента И1М и элемент задержки 2 Недостатком известного устройств является низкое быстродействие . Целью изобретения является повышение быстродействия устройства для сложения. Пбставленная цель достигается тем, что устройство для сложения, содержащее регистр сдвига, первый элемент ИЛИ, три элемента И, элемент задержки и RS-триггер, причем вход синхронизации регистра сдвига соединен с выходом генератора Импульсов, выход первого элемента ИЛИ соединен с входом старшего разряда регистра сдвига, первый вход первого элемента ИЛИ соединен, с выходом первого элемента И, первый вход которого соединен с выходом элемента задержки, вход которого подключен к прямому выходу RS-триггера, содержит также элемент И-НЕ, второй элемент ИЛИ и элемент НЕ, причем выход младшего разряда регистра сдвига соединен с первым входом элемента И-НЕ и первым входом второго элемента ИЛИ, второй вход которого соединен с вторым входом элемента И-НЕ и подключен к входу устройства, второй вход первого элемента ИЛИ соединен с выходом второго элемента И, первый вход которого подключен к инверсному выходу RS-триггера, а второй вход - к выходу третьего элемента И и к входу элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход элемента И-НЕ соединен с первым входом третьего элемента И и с инверсным S-входом RS-триггера, выход второго элемента ИШ соединен с вторым входом третьего элемента И и с первым инверсным R-входом RS-триггера, третий вход элемента И-НЕ соединен с шиной сброса устройства, с третьим входом третьего элемента И и с вторым инверсным R-входом RS-триг гера, На чертеже представлена структур ная схема устройства для сложения. Устройство содержит регистр 1 сд гу, элементы ИЛИ 2 и 3, элементы И 5 и 6, элемент И-НЕ 7, элемент НЕ F, элемент 9 задержки, RS-тригге 10, генератор импульсов, 11, входную шину12 и шину сброса 13. ftSтриггер 10 состоит из двух элементов И-НЕ 14 и 15. Работает устройство для сложения следующим образом. 8 исходном состоянии на шине сбро са 13 действует сигнал логического нуля, который устанавливает триггер IQ в нулевое состояние и закрывает элементы 6 и 7. С прямого выхода триггера 10 через элемент 9 сигнал логического нуля поступит на один и входов элемента 5 и далее через эле мент 2 на вход старшего разряда регистра 1, который за N тактов, где N-разрядность .регистра 1, заполняется нулями. Последовательный двоичный код первого числа, поступающий по входной шине 12, проходит через элемент ИЛИ 3 и элемент И 6 на входы элемен тов 4 и 8, Элемент 6 в течение N тактов открыт сигналом логической единицы выхода элемента И-НЕ 7, так как на его второй вход с выхода регистра сдвига 1 сдвигается нулевой код исходного состояния. Триггер 10 сохранит в это время нулевое состояние, при котором на входах элементов k и 5 действуют соответственно сигнал логической единицы инверсного выхода триггера 10 и сигнал логического нуля прямого выхода триг гера 10. В результате, последователь ный двоичный код первого числа проходит через элементы 4 и 2 и по так товым импульсам генератора 11 записы вается в регистр сдвига 1, начиная с младших разрядов. 1Ърледовательный двоичный код второго числа, поступакнчий в следующие N тактов по входной шине 12, суммируется с последовательным двоичным кодом первого числа, который сдвигается из регистра 1 следующим образом. Если начиная с младших разрядов в одноименных разрядах первого и второго числа не содержатся одно временно код логической единицы, то на входах элемента 7 отсутствует совпадение сигналов, а на его выходе действует сигнал логической единиды, который поддерживает элемент 6 в открытом состоянии. В этом случае на выходе элемента 3 формируется последовательный ДВОИЧНЫЙ код дизъюнкции двоичных кодов первого и второго чисел, который через элементы 6, 4,5, и 2 записывается в регистр сдвига 1. Так будет продолжаться до совпадения на входах элемента 7 единичных кодов одноименных разрядов первого и второго чисел, В случае совпадения на входах |Элемента 7 сигналов логической еди|нйцы, наВыходе этого элемента сформируется сигнал логического нуля, который закроет элемент 6 и установит триггер 10 в единичное состояние, в котором на его инверсном выходе сформируется сигнал логического нуля, поступающий на вход элемента Ц и вход регистра 1, а на прямом выходе - сигнал логической единицы, который задерживается на такт элементом 9. Следовательно, в данном такте на выходе элемента 9 действует сигнал логического нуля предыдущего состояния триггера 10, который поступает на третий вход- элемента 5.В результате первого совпадения сигналов логической единицы на входах элемента И-НЕ 7, на входах элементов 4 и 5 действуют сигналы логического нуля и в данный разряд регистра сдвига 1 записывается нулевой код, В .следующем такте на выходе элемента 9 формируется сигнал логической единицы, который поступает на вход элемента 5 и далее на вход регистра 1. Если при единичном СОСТОЯ.НИИ триггера 10 на входах элемента 7 действует комбинация нуля и единицы, то на входах элементов 3 и 7 будет сигнал логической единицы, который откроет элемент 6 и через элемент 8 закроет элемент 5. Таким образом, в соответствующий раз ряд регистра 1 будет записан нулевой код. Триггер 10 будет установлен в О при появлении на выходе элемента 3 сигнала логического нуля за счет наличия нулевых кодов в одноименных разрядах суммируемых чисел. На вход регистра 1 поступит в этом случае код предыдущего состояния триггера 1 Таким образом, устройство суммирует два двоичных числа, одно из которых сдвигается с выхода регистра сдвига 1, а другое поразрядно поступает но входной шине 12. Результат суммирования запоминается в регистре сдвига 1, так как а случае отсутствия переполнения регистра сдвига 1 триггер 10 вернется в нулевое состоя ние, а прекращение поступления Двоич ного кода по входной шине 12 обеспечивает формирование на выходе элемен та 7 сигнала логической единицы, который поддерживать элемент 6 в открытом состоянии. Цепь циркуля ции двоичного кода результата суммирования с выхода регистра сдвига 1на его вход замыкается чере;з элементы 3, 6, t и 2. В случае поступления по входной шине 12 последовательности двоичных кодов нескольких чисел в регистре сдвига 1 сформируется двоичный код суммы этих чисел. Сложение двух чисел предлагаемое устройство выполняет за один цикл, содержащий N тактов, где N-количество разрядов регистра сдвига 1, тогда как в известном устройстве сложение производится за два цикла или 2тактов. Таким образом имеет место двухкратное увеличение быстродействия ус ройства для сложения. формула изобретения .Устройство для сложения, содержащёе регистр сдвига, первый элемент 9 РГПИ, три элемента И, элемент задержки и KS-триггер, примем вход синхронизации регистра сдвига соединен с выходом генератора импульсов, выход первого элемента ИЛИ соединен с входом старшего разряда регистра сдвига, первый вход первого элемента ИЛИ соединен с выходом первого элемента И, первый вход которого соединен с выходом элемента задержки, вход которого подключен к прямому выходу RS-триггера, отличающееся тем, что, с целью повышения быстродействия, устройство содержит элемент И-НЕ, второй элемент ИЛИ и элемент НЕ, причем выход младшего разряда регистра сдвига соединен с первым входом элемента И-НЕ и первым входом второго элемента ИЛИ, второй вход которого соединен с вторым вхоftOM элемента И-НЕ и подключен к входу устройства, второй вход первого элемента ИЛИ соединен с выходом вто рого элемента И, первый вход которого подключен к инверсному выходу КЗ-триггера, а второй вход - к выходу третьего элемента И и к входу элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход элемента И-НЕ соединен с первым входом третьего элемента И и с инверсным S-входом RS-триггера, выход второго элемента ИЛИ соединен свторым входом третьего элемента И и с первым инверсным R-входом RS-триггера, третий вход элемента И-НЕ соединен с шиной сброса.устройства , с третьим входом третьего элемента И и с вторым инверсным R-входом KS-триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР If , кл. G 06 F 7/50, 1976. 2.Авторское свидетельство СССР tf 798829, кл. G 06 F 7/50, 1978 (прототип).

Авторы

Даты

1982-10-23—Публикация

1981-05-06—Подача