1

Изобретение относится к вычислительной технике, в частности к заломи.- нающим устройствам.

Известно постоянное запоминающее устройство трансформаторного,типа с ивдуктквной связью между вводом и выводом, которое ссстоит из адресных и выходных обмоток, прошивающих фер- ритовы сердечники, у которых выбор адреса осуществляется в части адресных формирователей без обычных Дек{ дирующих устройств непосредственно КЗ адресных сигналов, поступакацнх в любом, обычно двоичном, коде, а считывание ответов осуществляется автоматически в результате поступления управляющего, импульса без использования цепи выбора дискретных данньчх с установочными элементами ij . Наиболее близким к изобретению является устройство постоянной памяти с инс1уктивной связью, которые в больщинсгве случаев имеют линейную выборку а дреса, средства реализации которой pficnoложены вне самой запоктанающей среды, Ока состоит всегда из электронного блока выборки адреса и собственно пвгмяти (запоминающей матрицы), состояЩей из считывающих сердечников и о&моток. Это устройство имеет значительно сложные входные цепи декодирующего устройства и сложные проводные связи этих цепей с матрицей. До сих

пор известные постоянные запоминающие устройства (ПЗУ) всегда оснащаются специальными цепями со считыванием инффмации 2.

Цель изобретения - повьпцение надежности устройства. Кроме .того, в

нем достигается исключительно большая объемная плотность двоичной информации в кубическом сантиметре в результате ТОГО, что числовые обмотки прошдаt eaoT входной трансформатор а выход л инейного усилителя подключен к соответсгвующим входам усилителей считывания.

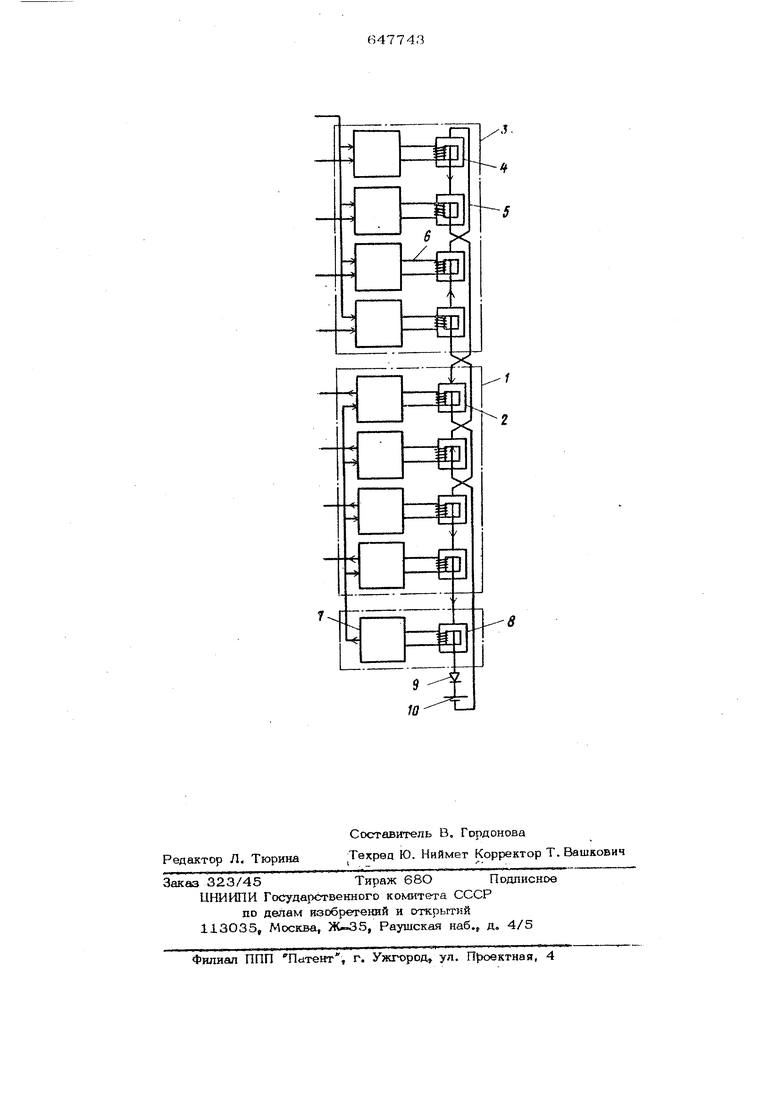

На чертеже показана . блок-схема нрьэдложенного устройства. OHO содержит усилители считыва|шя 1, считывающие трансформаторы 2 с Выходными обмотками, адресные форми рователи 3, адресньш трансформаторы 4 с адресными обмотками 5, числовые обмотки 6, блок стробнрования из линейно 14), усилителя 7, входной трансформатор 8, диод 9 и источник питания 10. На первые входы адресных формирователей подаются адресные сигналы, а на общий вход адресных формирователей поступает управляющий импульс, С выходов усилителей считывания 1 снимают ся выходные сигналы. Сигнал с входно го трансформатора, 8 для Выборки диокретных данных усиливается линейным усилителем 7 и, после усиления, посту пает на соответствующие- входы усилите лей считывания. 1. Адресные формирова- тели 3, нечетные адресные трансформаторы первого адресного формирователя 4 и третьего адресного формирователя 3 возбуждаются, если на их общий вход В период считывания подается управляющий импульс, а на их входы подается информация 1, Четные адресные сердечники четных адресных формирователей возбуждаются, как только на их общий вход подается управляющий импульс и одновременно на их входы поступает адресный сигнал с информацией СУ, В числовых обмотках 6, проходя-, щих через, адресные и считывающие трансформаторы индуцируются при электродвигкущие силы, положительные или отрицательные, в зависимости от направления обмотки возбуждения и типа укладки адресного провода. Отрицательные электродвижущие силы не проявляются, так как в каждой числовой обмотке провода включен диод 9, поляризова1 ный соответствующим образом, тельные эл езГтрйдВйжушиё СЙЙЁГ вйнуяйдают ток проходить через адресные обмотки только в том случае, если сумма значений больще потенциала постоянного тока, включенного в петлю адресной обмётки с диодом 9. При большем/количестве адресных формирователе: возбуж дается пропорциональное число Электро- движущих сил, индуцируемых в число-, вых обмотках. Однако по типу протяжки числовых обмоток их полярность раз лйчна. При идентичности полярностей величина электродпшкуп1ихсил в числовой обмотке возрастает до такой величины, что оконечный, диод 9 Ьткрываети ся и течет ток, который индуцируется

647743 В считывающих обмотках считывающих трансформаторов (ответы иоложйтель ной полярности для информации и отрицательной для информации О). Время длительности информации на входах усилителей считывания может бь1ть оформлено, как угхздно, например с домощью триггерных цепей. Длительность цикла зависит от физических свойств фероитовьгх сердечников и сое- тавлй.ет дробную доли микросекунды. Число адресных трансформаторов не должно ограничиваться четырьмя, как это показано в конкретном примере выполнения. ЕСЛИ число адресов составляет Р|, то число адресных трансформаторов равно 2f, , а число числовых обмото&2 . В оощём случ число считьюающих трансформаторов составляет от 1 до К. Предложенное устройство может быть использовано в качестве управляющей памяти автоматических вычислительных мащин и служить для хранения команд и микропрограмм,, для генерирования функций, констант и знаков, а также в связи со своим, незначительным объемом найти успещное применение в качестве декодирующего устройства в различных периферийных устройствах. Формула изобретения Постоянное запоминающее устройство трансформаторного типа, содержаИёё усилители считывания, подключенные к выходным обмоткам считывающих трансформаторов, адресные формирователи, подключенные к входным обмоткам адресных трансформаторов, числовые обмотки, прошивакицие считывающие и адресные трансформаторы, и блок стробирования, состоящий из линейного уси- лигеля и входного трансформатора, выходная обмотка которого подключена KU линейного усилителя о т л и- ч а ю щ е ее я тем, что, с целью повышения надежности устройства, в / нем числовые обмотки прощивают вход- ной трансформатор, а выход линейного усилителя подключен к соответствующим входам усилителей считывания. Источники информации, принятые во вним15ние при экспертизе . 1.Авторское свидетельство СССР N 131552, кл. Q 11 С 17/02, I960. 2. Специальные элементы запомин юттих устройств ЭВМ. Проектирование и расчет. М., Советское Радио , 26.03.1971, с. ЗО7 - 313.

| название | год | авторы | номер документа |

|---|---|---|---|

| Индикатор | 1976 |

|

SU647707A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| МАТРИЧНОЕ ФЕРРИТ-ДИОДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU395899A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU289448A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

Авторы

Даты

1979-02-15—Публикация

1972-07-31—Подача