Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭГО.

Цель изобретения - упрощение устройства и увеличение быстродействия.

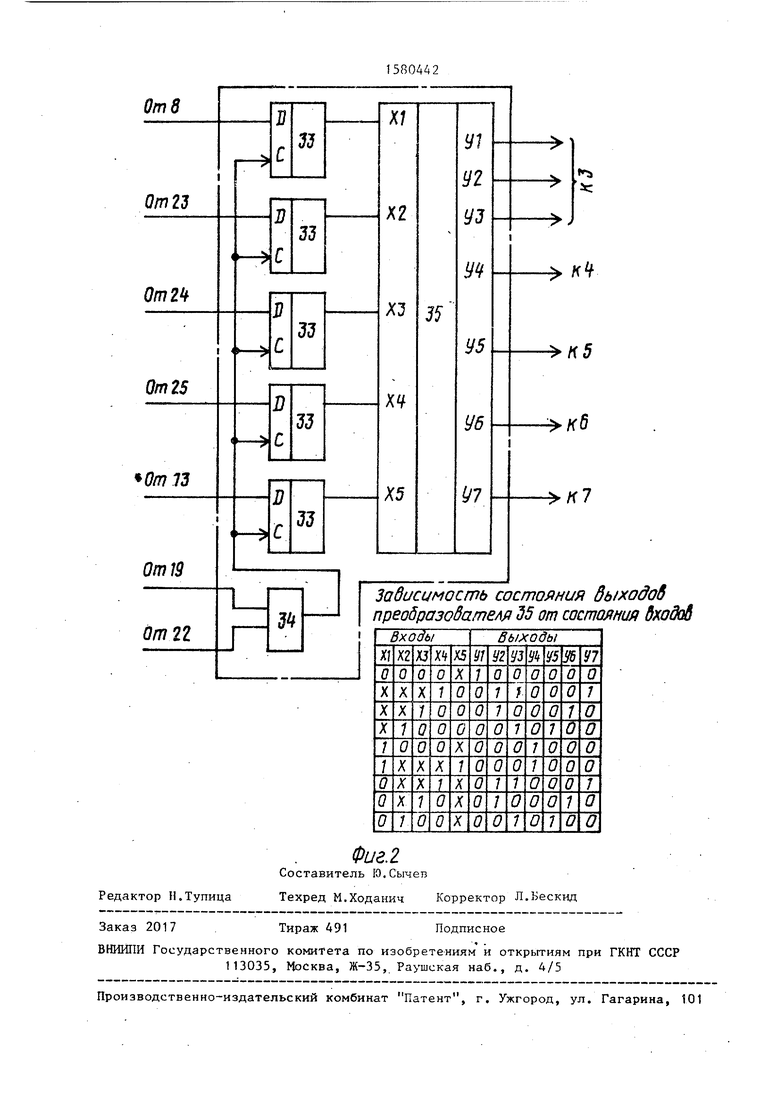

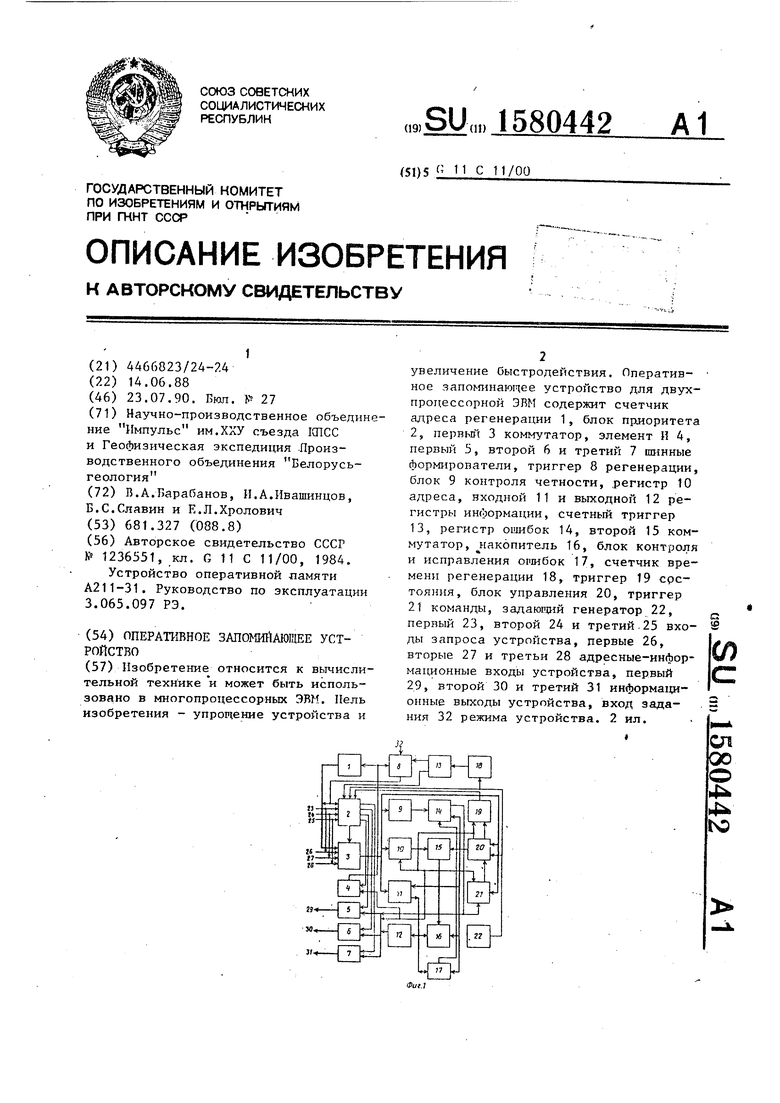

На фиг.1 приведена структурная схема оперативного запоминающего устройства для двухпроцессорных ЭВМ; на фиг.2 - структурная схема блока приоритета.

Оперативное запоминающее устройство содержит счетчик 1 адреса регенерации, блок 2 приоритета, первый коммутатор 3, элемент И 4, первый 5, второй 6 и третий 7 шинные формирователи, триггер 8 регенерации, блок 9 контроля четности, регистр 10 адреса, входной регистр 11 информации, выходной регистр 12 информации, счетный триггер 13, регистр 14 ошибок, второй коммутатор 15, накопитель 16, блок 17 контроля и исправления ошибок (JQIO),,счетчик 18 времени регенерации, триггер 19 состояния, блок 20 управления, триггер 21 команды, задающий генератор 22, первый 23, второй 24 и третий 25 входы запроса устройства, первые 26, вторые 27 и третьи 28 адресные-информационные входы устройства, первые 29, вторые 30 и третьи 31 информационные выходы устройства, вход 32 задания режима устройства, триггеры 33, элемент И 34 и преобразователь 35 кодов.

Для упрощения на фиг.1 не приведены цепи сброса и схемы формирования контрольных разрядов выходной информации, входы которой подключают к выходам выходного регистра 12 информации, а выходы,- к информационным входам первого 5, второго 6 и третьего 7 шинных формирователей, которые могут быть выполнены на основе ГО1С К531АП4 или К580ВА86. -Блок 9 контроля четности может быть выполнен на основе ИМС К531Ш5. Регистр 10 адреса, входной регистр 11 информации и выходной регистр 12 информации могут быть выполнены на ИМС К531ИР23. Накопитель 16 может быть выполнен на основе ИМС К565РУ5. Блок КИО 17 может быть реализован на большой ин- теграпьной схеме типа K555BJ41.

Оперативное запоминающее устройство для двухпроцессорной ЭВМ работает следующим образом.

В исходном состоянии блок 20 управления не запущен, триггер 19 сос

5

0

5

0

5

0

5

0

5

тояния, триггер 8 регенерации сброшены и работа блока 2 приоритета разрешена сигналом, поступающим с быхо- да триггера 19 состояния на вход разрешения работы бпока приоритета. При отсутствии сигналов на входах запросов блока 2 приоритета сигналы с его выходов запрещают прохождение информации через коммутатор 3, шинные формирователи 5-7, а также работу элемента II 4.

Задающий генератор 22 формирует сигналы, которые подаются на вход счетчика 18 времени регенерации. На выходе его формируются сигналы с периодом, равным половине периода времени, в течение которого должен выпоЛяться цикл регенерации очередной строки. Сигналы с выхода счетчика 18 времени регенерации поступают на счетный вход счетного триггера 13, который устанавливается в единичное состояние первым, третьим, пятым и т.д. сигналом с выхода счетчика 18 времени регенерации и в нулевое состояние вторым, четвертым, шестым и т.д. сигналом с выхода счетчика 18 времени регенерации.

При установке счетного триггера 13 в единичное состояние сигнадом с его первого выхода, поступающим на вход синхронизации триггера 8 регенерации, последний устанавливается в единичное состояние, так как на его информационный вход подан уровень логической единицы с входа 32 устройства. В исходном состоянии устройство остается до тех пор, пока на одном или нескольких входах запросов блока 2 приоритета, т.е. на выходе триггера 8 регенерации, или одном из входов 23-25 запросов устройства не появятся сигналы.

Появление сигнала на первом входе запроса блока 2 приоритета соответствует требованию выполнить регенерацию очередной строки накопителя. Появление сигнала на втором входе запроса, являющимся входом 23 устройства, соответствует обращению к устройству одного из процессоров двухпроцессорной ЭВМ, например первого.

Третий вход запроса, являющийся входом 24 устройства, служит для подачи сигнала обращения от второго процессора, а четвертый, являющийся входом 25 устройства, - от канала прямого доступа в память. Если счетный триггер 13 установлен в 1,

о запросу, поступающему на первый ход запроса блока 2 приоритета, приваивается наименьший приоритет, запросу, поступающему на четвертый ход запроса блока 2 приоритета, - аибольший приоритет. Тогда при подя- е на входы запросов блока 2 приоритета одного или нескольких сигналов запросов будет обрабатываться только тот запрос, который имеет высший из поступивших запросов приоритет.

Если обрабатывается запрос, поступивший на первый вход запроса блока 2 приоритета с выхода триггера 8 регенерации, сигналами с выходов блока 2 приоритета, поступающими на управляющие входы коммутатора 3, включается первое направление коммутатора 3, на первый информационный вход которого поступает адрес регенерируемой строки с выхода счетчика 1 адреса регенерации и сигнала запроса с выхода триггера 8 регенерации. Одновременно сигнал с первого выхода блока

2приоритета, поступая на первый вход элемента И 4, разрешает его работу. При отработке запроса от первого 23, второго 24 или третьего 25 входов запросов устройства через коммутатор

3проходят сигналы соответственно с второго, третьего или четвертого входов, являющихся входами 26-28 устройства. Одновременно сигналы второго, третьего и четвертого выходов блока 2 приоритета, поступающие на управляющие входы первого 5, второго 6 и третьего 7 шинных формирователей, разрешают прохождение информации через первый 5, второй 6 или третий 7 шинные формирователи (соответствукщий входу, запрос от которого обрабатывается) на один из выходов 29-31 устройства.

Сигнал запроса с выхода коммутатора 3 поступает на вход запуска блока 20 управления, который по этому сигналу формирует сигнал на своем первом выходе, который, поступая на вход установки в 1 триггера 19 состояния, устанавливает его в 1, запрещая тем самым работу блока 2 приоритета, который не изменяет состояния сигналов на своих выходах до тех пор, пока его работа не будет вновь разрешена. Одновременно сигнал с первого выхода блока 20 управления, поступающий на вход синхронизации триггера 21 команды, фиксирует на нем код команды (чтение или запись), поступающий на

0

5

0

5

0

5

0

5

0

5

его информационный вход с пыходов коммутатора 3. В цикле регенер-щии производится выполнение команды чтения, так как в этом случае код команды с выхода коммутатора 3 на информационный вход триггера 21 команды не поступает и на этом входе присутствует уровень логической 1.

Указанный выше сигнал с первого выхода блока 20 управления поступает также на управляющий вход регистра 10 адреса, фиксируя на нем адрес, по которому производится обращение к устройству и который поступает на информационный вход регистра 10 адреса с выхода коммутатора 3. Этот же сигнал, поступая на информационные входы первого 5, второго 6 и третьего

7шинных формирователей и на второй вход элемента И 4, при обработке одного из внешних запросов через первый 5, второй 6 или третий 7 шинный формирователь, работа которого разрешена, проходит на один из выходов 29-31 устройства как сигнал о том, что начата обработка поступившего

на соответствующий вход 23-25 запроса. В случае обработки запроса от триггера 8 регенерации работа всех шинных формирователей 5-7 запрещена и разренГена работа элемента И 4. Сигнал с выхода этого элемента, поступая на вход установки в О триггера

8регенерации, сбрасывает его, тем самым снимая запрос с первого входа запроса блока 2 приоритета. Этот же сигнал, поступая на вход счетчика 1 адреса регенерации, увеличивает его содержимое на единицу. Измененное содержимое счетчика 1 адреса регенерации используется в следующем цикле регенерации.

Далее блок 20 управления формирует последовательность управляющих сигналов, причем различия в этой последовательности, необходимые для выполнения чтения или записи, обуславливаются поступающим на вход задания режима блока 20 управления кода команды с выхода триггера 21 команды. При этом как при записи, так и при чтении блок 20 управления выдает управляющий сигнал на управляющий вход коммутатора 15, обеспечивая прохождение адреса, хранящегося в регистре 10 адреса через мультиплексор на адресные входы накопителя 16. При записи и при чтении одинаково формируются сигналы, подаваемые на входы управления накопителя 16, за исключением сигнала, определяющего запись. Этот сигнал формируется только при выполнении команды записи. На входы управле- ния блока КИО 17 при записи подается последовательность сигналов, обеспечивающих формирование контрольных разрядов к поступающему на его информационные входы-выходы записываемому числу с выходов входного регистра 11 информации. Это же число поступает на соответствующие информационные - входы накопителя 16, Контрольные разряды поступают в накопитель 16 с соответствующих входов-выходов блока КИО 17, При этом в режиме записи на входы управления входного регистра 11 информации поступают сигналы, обеспечивающие Фиксацию на этом ре™

гистре записываемого числа, поступающего на его информационный вход с выхода коммутатора 3 а в режиме чтения выходы входного регистра 11 информации отключаются, т.е. прре- водятся в состояние высокого выходного сопротивления.

Подаваемые в режиме чтения на входы управления блока КИП 17 сигналы обеспечивают прием блоком КИО 17 поступающей на его входы-выходы из накопителя 16 считанной информации, контроля ее, исправления одиночной ошибки и выдачу исправленной информации в выходной регистр 12 инфор- мации, на котором она фиксируется сигналом, поступающим на вход управления этого регистра. При этом, если включен один из шинных формирователей 5, 6 или 7, считанная информа- ция поступает через него на один из выходов устройства 29, 30 или 31. Если при чтении обнаружена ошибка, то на выходе блока КИО 17 формируется сигнал ошибки, поступающий на второй вход регистра 14 ошибок, где наличие этой ошибки запоминается. Регистр 14 ошибок служит также для фиксации ошибок по четности в поступающем з уст ройство адресе (как при записи, так и при чтении) и информации (только при записи). Для этого входы блока 9 контроля по четности подключены к выходам коммутатора 3, с которых поступают адрес и информация, сопровож- даемые контрольными разрядами. Сигна об ошибке по четности с выхода блока 9 контроля четности поступает на первый вход регистра 14 ошибок, где фиксируется. Фиксацию сигнала ошибки по четности в адресе и (или) инЛормации обеспечивают стробирующие сигналы, поступающие на входы управления регистра 14 ошибок с выхода блока 20 управления, причем в режиме чтения строб фиксации ошибки по четности в поступающей информации не формируется. Сигнал с выхода регистра 14 ошибок, свидетельствующий о появлении при выполнении данного цикла одной из ошибок, через один из включенных шинных формирователей 5, 6 или 7 (за исключением случая, когда отрабатывается запрос от триггера 8 регенерации) передается на один их выходов 29, 30, или 31 устройства как сигнал об ошибке в его работе. Этот же сиг-нал, поступая на вход установки в I триггера 21 команды, устанавливает его в 1, что при выполнении команды чтения ничего не меняет, а при записи переключает устройство на выполнение команды чтения, что предотвращает искажение информации в накопителе при неправильно принятых адресе или информации.

После окончания выполняемого цикла на втором выходе блока 20 управления появляется сигнал, который поступает на вход установки в О триггера 19 состояния, и он сбрасывается, разрешая работу блока 2 приоритета. Блок 2 приоритета начинает анализировать наличие сигналов на своих входах запросов. Если таковые отсутствуют, то устройство переходит в исходное состояние. При наличии одного или нескольких запросов описанный цикл повторяется, при этом обрабатывается запрос, имеющий наивысший приоритет „ среди поступивших.

Работа блока 2 приоритета и блока 20 управления синхронизируется поступающими на их входы синхронизации сигналами с выхода задающего генератора 22.

При работе устройства при одновременном появлении запроса от триггера 8 регенерации и других запросов первый не будет обработан до тех пор, пока не будут обработаны все поступишие одновременно с ним запросы, а таже запросы, поступающие що время их обработки. С одной стороны, это снижает время реакции устройства на запросы из-за отсутствия никлов регенерации при интенсивном потоке за

просов. С другой стороны, недопустима такая задержка цикла регенерации очередной строки, которая может привести к искажению информации в накопителе.

Если сигнал запроса на регенерацию очередной строки, сформированный по сигналу с выхода счетчика 18 времени регенерации, не был обработан в течение одного интервала таймера, тогда следующий сигнал с выхода счетчика 18 времени регенерации сбрасывает счетный триггер 13, при этом состояние триггера 8 регенерации не изменяется. Таким образом, на первый вход запроса блока 2 приоритета продолжает поступать сигнал запроса с выхода триггера 8 регенерации. После окончания очередного цикла работы и сброса триггера 19 состояния блока 2 приоритета разрешается, но так как на его вход управления подан сигнал с второго выхода счетного триггера 13, который в это время сброшен, то порядок присваивания приоритетдв изменяется по сравнению с описанным.

Наивысший приоритет присваивается запросу, поступающему на первый вход запроса, т.е. запросу от триггера 8 регенерации. Следующий приоритет присваивается запросу, поступающему на четвертый вход запроса блока 2 приоритета. Самый низкий приоритет присваивается запросу, поступающему на второй вход запроса блока 2 приоритета. Поэтому на выходе блока 2 приоритета появляются сигналы, открывающие первое направление коммутатора 3 и разрешающие работу элемента И 4, т.е. начинает выполняться цикл регенерации. В процессе выполнения этого цикла сигналом с выхода элемента И 4 триггер 8 регенерации сбрасывается, сигнал запроса с первого входа запроса блока 2 приоритета снимается и не влияет на обработку сигналов запросов, поступающих на остальные входы запросов блока 2 приоритета.

По очередному сигналу с выхода счетчика 18 времени регенерации устанавливается в 1 счетный триггер 13, а за ним триггер 8 регенерации, и устройство продолжает работу, как описано выше.

Формула изобретения

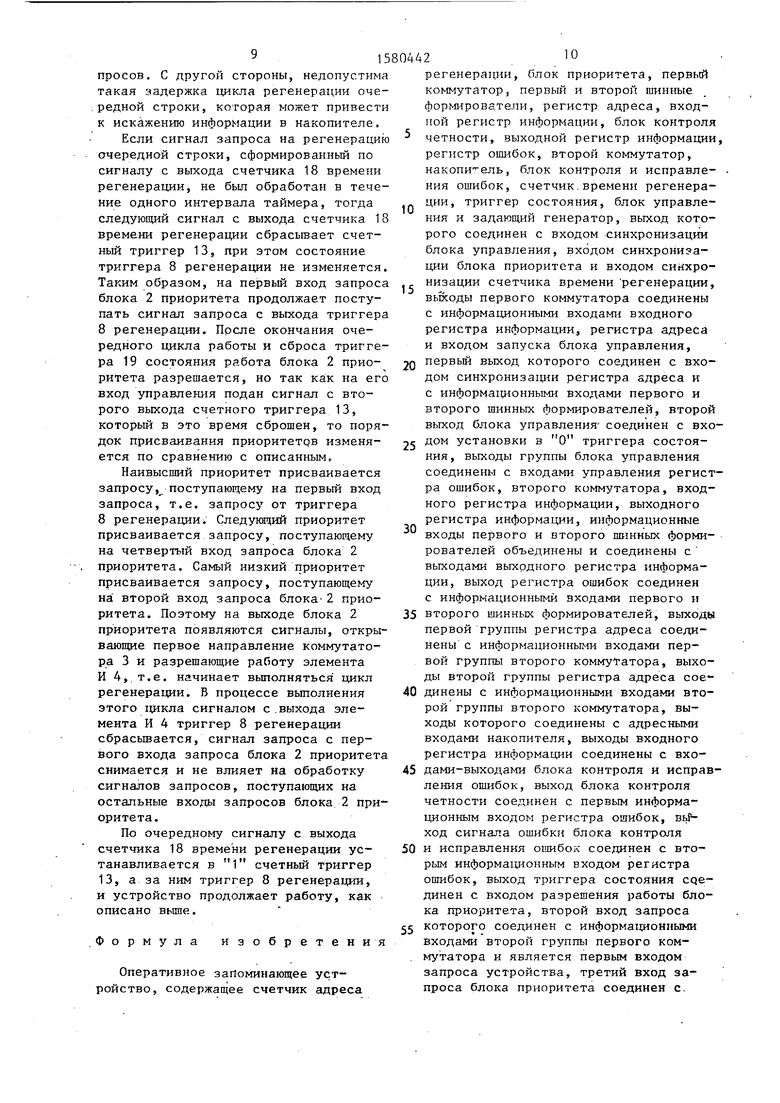

Оперативное запоминающее устройство, содержащее счетчик адреса

0

5

5

регенерации, блок приоритета, первый коммутатор, первый и второй шинные формирователи, регистр адреса, входной регистр информации, блок контроля четности, выходной регистр информации, регистр ошибок, второй коммутатор, накопитель, блок контроля и исправле- ния ошибок, счетчик времени регенерации, триггер состояния, блок управления и задающий генератор, выход которого соединен с входом синхронизации блока управления, входом синхронизации блока приоритета и входом синхронизации счетчика времени регенерации, выходы первого коммутатора соединены с информационными входами входного регистра информации регистра адреса и входом запуска блока управления, первый выход которого соединен с входом синхронизации регистра адреса и с информационными входами первого и второго шинных формирователей, второй выход блока управления соединен с вхо- 0

дом установки в

триггера состояния, выходы группы блока управления

0

соединены с входами управления регистра ошибок, второго коммутатора, входного регистра информации, выходного регистра информации, информационные входы первого и второго шинных формирователей объединены и соединены с выходами выходного регистра информации, выход регистра ошибок соединен с информационными входами первого и

5 второго шинных формирователей, выходы первой группы регистра адреса соединены с информационными входами первой группы второго коммутатора, выходы второй группы регистра адреса динены с информационными входами второй группы второго коммутатора, выходы которого соединены с адресными входами накопителя, выходы входного регистра информации соединены с вхо5 дами-выходами блока контроля и исправления ошибок, выход блока контроля четности соединен с первым информационным входом регистра ошибок, ход сигнала ошибки блока контроля

0 и исправления ошибок соединен с вторым информационным входом регистра ошибок, выход триггера состояния cqe- динен с входом разрешения работы блока приоритета, второй вход запроса которого соединен с информационными входами второй группы первого коммутатора и является первым входом запроса устройства, третий вход запроса блока приоритета соединен с

5

информационными входами третьей группы первого коммутатора и является вторым входом запроса устройства, информационные входы второй и третьей групп первого коммутатора являются соответственно первыми и вторыми адресными информационными входами устройства, выходы первого шинного формирователя являются первыми ин- ф| рмационными выходами устройства, выходы второго шинного формирователя являются вторыми информационными выходами устройства, отли чающееся тем, что, с целью упрощения устройства и повышения быстродействия, в него введены триггер регенерации, счетный триггер, триггер команды, элемент И и третий тинный формирователь, выход переполнения счетчика времени регенерации соединен с входом синхронизации счетного триггера, прямой выход которого соединен с входом синхронизации триггера регенерации, инверсный выход счетного триггера соединен с входом управления блока приоритета, выход триггера регенерации соединен с первым входом запроса блока приоритета и информационными входами первой группы первого коммутатора, выходы счетчика адреса регенерации соединены с информационными входами первой группы первого коммутатора, четвертый вход запроса блока приоритета соединен с информационными входами четвертой группы первого коммутатора и является третьим входом запроса устройства, выходы группы блока приоритета соединены с управляющим входами первого коммутатора, первый выход блока приоритета соединен с первым входом элемента И, второй, третий и четвертый выходы блока приоритета соединены с управляющими входами первого, вто

0

5

0

5

0

рого и третьего -шинных формирователей соответственно, второй вход элемента И соединен с первым выходом блока управления, выход элемента И соединен с входом установки в О триггера регенерации и входом синхронизации счетчика адреса регенерации, выходы группы блока управления соединены с входами обращения и записи-чтения накопителя, входами управления блока контроля и исправления ошибок и с информационными входами третьего шинного формирователя, первый выход блока управления соединен с входом синхронизации триггера команды, с информационными входами третьего шинного формирователя и с входом установки в 1 триггера состояния, выходы первого коммутатора соединены с входами блока контроля четности и с информационным входом ггриггера команды, выход которого соединен с входом задания режима блока управления, выходы выходного регистра информации соединены с информационными входами первого, второго и третьего шинных формирователей, выход регистра ошибок соединен с входом установки в 1 триггера команды и с информационными входами третьего шинного формирователя, выходы входного регистра информации соединены с информационными входами-выходами накопителя и с информационными входами выходного регистра информации, выходы третьего шинного формирователя являются третьими информационными выходами устройства, информационный вход триггера регенерации является входом задания режима устройства, информационные входы четвертой группы первого коммутатора являются третьими адресными- информационными входами устройства.

Редактор Н.Тупица

Фиг. 2

Составитель Ю.Сычев

Техред М.Ходанич Корректор Л.Бескид

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭВМ. Цель изобретения - упрощение устройства и увеличение быстродействия. Оперативное запоминающее устройство для дбухпроцессороной ЭВМ содержит счетчик адреса регенерации 1, блок приоритета 2, первый 3 коммутатор, элемент И 4, первый 5, второй 6 и третий 7 шинные формирователи, триггер 8 регенирации, блок 9 контроля четности, регистр 10 адреса, входной 11 и выходной 12 регистры информации, счетный триггер 13, регистр ошибок 14, второй 15 коммутатор, накопитель 16, блок контроля и исправления ошибок 17, счетчик времени регистрации 18, триггер 19 состояния, блок управления 20, триггер 21 команды, задающий генератор 22, первый 23, второй 24 и третий 25 входы запроса устройства, первые 26, вторые 27 и третьи 28 адресные-информационные входы устройства, первый 29, второй 30 и третий 31 информационные выходы устройства, вход задания 32 режима устройства. 2 ил.

Заказ 2017

Тираж 491

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Оперативное запоминающее устройство | 1984 |

|

SU1236551A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ добывания бензина и иных продуктов из нефти, нефтяных остатков и пр. | 0 |

|

SU211A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-06-14—Подача