1

Изобретение относится к области вычислительной техники и может быть использовано в качестве буферного запоминающего устройства:.

Известны буферные запоминающие 5 устройства, содержащие поразрядно соединенные регистры, схемы управления перезаписью по числу регистров, выход и один вход каждой из которых подключены соответственно к входу 10 считывания и к выходу маркерного разряда одноименного регйстра,агд;{)угой вход каждой схемы управления перезаписью, кроме последней, подключен к выходу маркерного разряда следующего 15 регистра.

Однако эти устройства не обладают достаточной надежностью ввиду отсутствия контроля работы схем управления перезаписью.20

Наиболее близким техническим решением к данному является буферное запоминающее устройство, содержащее поразрядно соединенные регистры, инверторы, элементы И, ИЛИ и маркер- 25 ,ные триггеры.

Недостатком этого устройства является возможность потери или появление ложной информации при сбоях схем управ;1ения перезаписью. Кроме 30

того, отсутствие синхронизации входных импульсов записи с тактовыми сигналами схем управления перезаписью снижает надежность работы известного устройства.

Целью изобретения является повышение надежности работы устройства за счет обнаружения сбоев схем управления перезаписью.

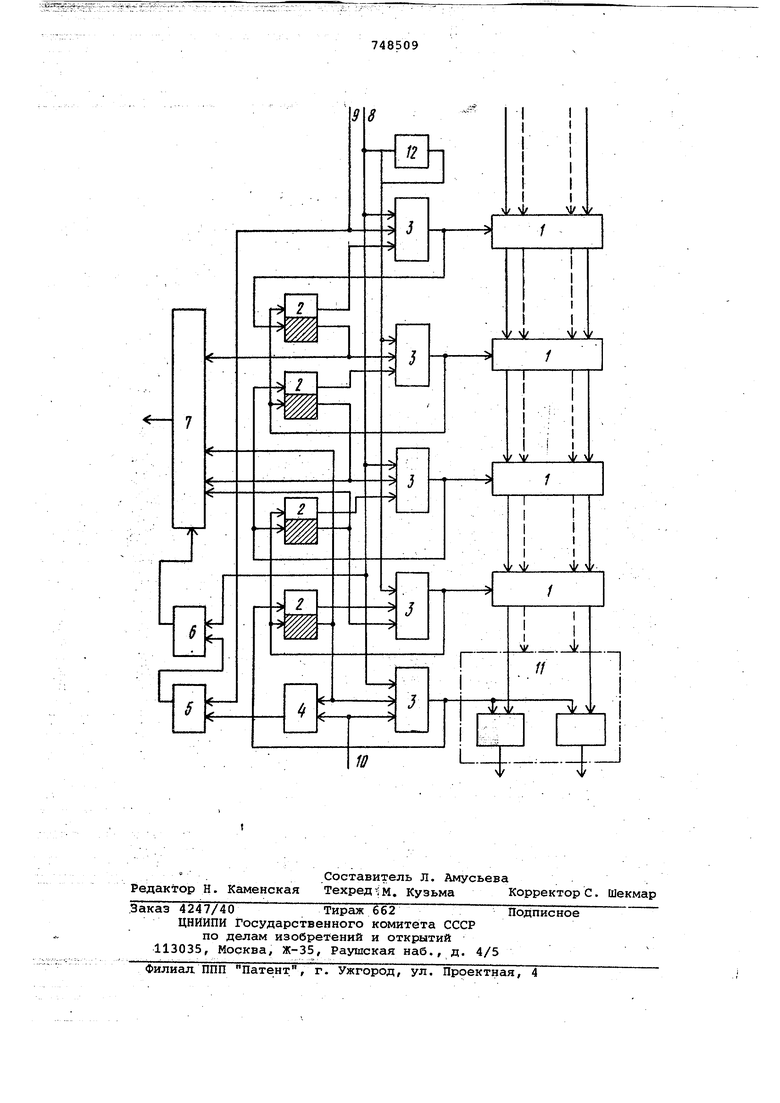

Поставленная цель достигается тем, что буферное запоминающее устройство содержит регистры, одноименные разрядные шины которых соединены последовательно, а .входы записи подключены к выходам одноименны: блоков управления, кроме последнего, выходы блоков управления соединены с единичными и нулевыми входами соответствующих маркерных триггеров, нулевые выходы которых подключены к первым входам одноименных блоков управления, кроме последнего, а единичные выходы - ко вторым входам блокЬв управления, а третьи входы нечетных блоков управления подключен ы к тактовой шине непосредственно, а четных - через инвертор, элемент И, счетный триггер, первый и второй сумматоры по модулю два, информационные входы первого сумматора по модулю два додключены к единичным выходам маркерных триггеров, а управляняций вход к выходу счетного триггера, один вхо которого подключен к тактовой шине и третьему входу последнего блока упра Ленин, другой - через второй сумматор по модулю два - к шине записи и выходу элемента И, один из входов которого подключен к шине считывания и первому входу блока управления, а другой - к единичному выходу последнего маркерного триггера, к соответствуквдему входу пёрвбго сумматора и ко второму входу последнего блоки управления. На чертеже представлена схема уст ройства. Устройство содержит п регистров 1 одноименные разряды которых соединены последовательно, п триггеров 2, п + 1 блоков 3 управления, элемент 4 И, сумматор 5 по модулю , триггер б, например T-V типа, управляемый сумматор 7 по модулю два на п входов, тактовую шину 8, шину 9 запи си, шину 10 считывания, выходные эле менты 11 И для вывода информации и инвертор 12. Единичные выходы триггеров 2 подключены к первым входам блоков 3 управления каждого регистра, за исключением первого, и к информационным входам управляемого сумматора 7 по модулю два. Ко вторым входам блоков 3 управле ния, за исключением последнего, подключены нулевые выходы триггеров 2, а выходы блока 3 управления, за исключением последнего, подключены к входам, записи регистров 1, входам ус таноЕ1Ки в единичное состояние тригге ров 2 следуюцих регистров и входам у тановки в нулевое состояние триггеров 2 одноименных регистров. Шина 9 записи информации и шина 1 считываний информации подключены: со ответственно , к первому входу блбка управления пёрезаписыо первого регис ра и второму входу последнего блок управления. Шина 10 считывания информации через элемент 4 И, второй вход которой подключен к единичному выходу п-го триггера 2, соединена с сумматором п модулю два, второй вход которого под ключен к шине 9 зациси йнфбрмацИи, а выход подключен к входу V тригге ра 6, вход Т которого соединён с ши ной 8 тактовых сигналов и третьими вkoдaми нечетных схем 3 управления пе резаписью, и через инвертор 12 с трет ми входами четных схем 3 управления перезаписью. Выход триггера б являет ся входом управления сумматора 7 по модулю ДВ1а. Устройство работает слёдуклцим образом. в исходном состоянии триггеры 2 и счетный триггер 6 находятся в нулевом состоянии. На шину 8 постоянно поступают так говые сигналы, частота которых не нигже частоты записи информации. Для записи информации в запоминающее устройство на шину 9 поступает запрос на запись. Информация со входов переписывается в первый регистр 1 по переднему фронту тактового импульса при наличии единичного потенциала на нулевом выходе триггера 2 этого регистра и запроса на запись. При этом триггер 2 этого регистра устанавливается в единичное состояние. Вторая схема 3 управления перезаписью перепишет информацию из первого регистра 1 во второй по заднему фронту тактового импульса при единичном состоянии триггера 2 первого регистра 1 и нулевом состоянии триггера 2 второго регистра. При этом триггер 2 второго регистра 1 устанавлиъ ется в единичное состояние, а триггер 2 первого регистра 1 - в нулевое. Дальнейшее продвижение информации из регистра в регистр осуществляется аналогично. При считывании информации на шину 10 поступает запрос на считывание. При этом, если триггер 2 последнего регистра 1 находится в единичном состоянии, по переднему фронту тактового импульса информация через элементы 11 И выводится из устройства и триггер 2 последнего регистра 1 уста , навливается в нулевое состояние. Таким образом, по переднему фронту тактового импульса информация пере писывается из четного регистра 1 в нечетный, по заднему фронту происходит перезапись информации из нечетного регистра 1 в четный. Контроль правильности продвижения . информации в регистре происходит следующим образом. Сумма по модулю два состояний триггеров 2 изменится, если в каждом такте будет происходить запись информационного слова в запоминающее устройство, либо считывание слова из него.. При этом на выходе сумматора 5 по модулю два будет присутствовать единичный потенциал, что приведет к срабатыванию счетного триггера б. В противном случае триггер б не будет изменять своего состояния. Сумматор 7 по модулю два осуществляет контроль информации на нечетность при единичном состоянии триггера б или на четность при нулевом состоянии счетного триггера б. Таким образом, при правильной работе буферного запоминающего устойства на выходе yпpaвJ Iяeмoгo сумматора 7 по модулю два будет присутствовать высокий потенциал. Данное устройство позволяет обнаруживать факты сбоя блоковугхравления, что может обеспечить устранение возникновения ложной информации при одиночных сбоях, характерным признаком которой может быть многократное повторение одного и того же сообщения. Особое значение обнаружения факта сбоя блоков управления имеет в случае сбоев, приводящих к п терям, так как такие сбои приводят к нарушению временной последовательнос ти сообщений, а это в свою очередь искажает достоверность целых массиВОВ. Наличие же информации о возникновении этих сбоев позволит учесть эти потери и сохранить временную последовательность всего массива. Формула изобретения Буферное запоминающее устройство, содержащее регистры, одноименные раз рядные шины которых соединены последовательно, а входы записи подключены к выходам одноименных блоковуправления, кроме последнего, выходы блок1эв управления соединены с единичными и нулевыми входами соответствующих маркерных триггеров, нулевые выходы которых подключены к первым входам одноименных блоков управления, кроме последнего, а единичные выходы - ко вторым входам блоков управления, третьи входы нечетных блоков управления подключены к тактовой шине непосредственно, а четных - черсэ инвертор, отличающееся тем, что, с целью повышения надежности устройства, оно содержит элемент И, счетный триггер, первый и второй сумматоры по модулю два, информационные входы первого сумматора по модулю два подключены к единичным выходам маркерных триггеров, а управляющий вход - к выходу счетного триггера, один вход которого подключен к тактовой шине и третьему входу последнего блока управления, другой - через второй сумматор по модулю два, к шине записи и выхдду элемента И, один из входов которого подключен к шине считывания и к первому входу блока управления, а другой - к единичному выходу последнего маркерного триггера,к соответствунмцему первого сумматора и ко второму входу последнего блока управления.

ч

L.J.. V

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU842973A1 |

| Буферное запоминающее устройство | 1981 |

|

SU991512A1 |

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

| Буферное запоминающее устройство | 1975 |

|

SU551702A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU993444A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Генератор случайных чисел | 1984 |

|

SU1310813A1 |

Авторы

Даты

1980-07-15—Публикация

1978-05-15—Подача