и вторым инверсным вх.одом второго элемента И, вьтход которото соединен с прямым управляющим входом коммутатора управления выводом, седьмой выход блока синхронизации соединен с первым входом девятого элемента И, выход которого соединен с входом считывания блока памяти, восьмой выход блока синхронизации соединен с вторыми входами седьмого и девятого элементов И, вторым входом сброса блока ввода данных и первым входом третьего элемента ИЛИ выход которого соединен с R-входом триггера запроса, первый входом чет вертого элемента ИЛИ и входом сброса блока вывода данных, девятый выход блока синхронизации соединен с вторым управляющим входом коммутатора управления считьгеан ем, R-входом триггера стирания, вход сброса устройства .соединен с R-входом триггера сброса, с -первым входом пятого элемента ИЛИ и входом сброса блока местного управления, выход регистрации переполнения кото рого соединен с информационным входом блока вывода данных, десятый выход блока синхрониз.ации соединен с J-входами триггеров записи, триггеров считывания, входом снятия переполнения блока местного управле ния и J-входом триггера стирания, единичный выход которого соединен с прямым входом десятого элемента И и третьим входом седьмого элемента И, группа информационных входов устройства соединена с группой информационных входов блока ввода дан ных, группа информационных выходов и выход наличия данных которого соединены соответственно с группой информационных входов блока памяти и четвертым входом седьмого элемента И, выход первого элемента И соединен с третьим входом девятого эле мента И и входом обращения блока памяти, группа выходов которого соединена с группой информационных входов блока вывода данных, первый информационный выход блока в.ывода данных соединен с информационным входом блока местного управления и первым информационным входом коммутатора управления считыванием, группа информационных выходов и вто рой информационный выход блока вы,вода данных соединены соответственно с группой информационных выходов 83 устройства и вторым ||ходом четвертого элемента И, выход которого соединен с J- и С-входами триггера запроса, выход которого соединен с первым информационным входом коммутатора управления выводом, инверсным входом четвертого элемента И, выходом запроса группы управляющих выходов устройства и инверсным входом четвертого элемента ИЛИ, выход которого соединен с R-входами первого и второго триггеров управления выводом, -выход первого триггера управления выводом соединен с третьим входом синхронизации блока местного управления,. вторым входом синхронизации блока вывода данных, вторым информационным входом коммутатора управления выводом и вторым входом восьмого элемента И, выход которого соединен с выходом маркера данных группы управляющих выходов устройства, J- и С-входами второго триггера управления выводом, единичный выход второго триггера управления вьгоодом соединен, с третьим информационным входом коммутатора управления выводом, нулевой выход второго триггера управления выводом соединен с третьим входом восьмого элемента И и четвертым информационным входом коммутатора управления выводом, выход которого соединен с J, С- и R-входами первого триггера управления выводом, К-входы второго триггера управления выводом, триггера стирания, триггера готовности, триггера запроса, первого и второго триггеров регистрации, триггеров записи и триггеров считывания соединены с шиной нулевого потенциала, вход разрешения регистрации устройства соединен с инверсным входом первого элемента ИЛИ и вторым входом третьего элемента И, выход которого соединен с J- и С-входами триггера готовности, выход которого соединен с инверсным входом третьего элемента И, третьим входом четвертого элемента И, вход запрещения регистрации устройства соединен с R-входами первого и-второго триггеров регистрации и третьим входом пятого элемента И, выход которого соединен с J- и С-входами первого триггера регистрации, выходы первого и второго триггеров регистрации соединены соответственно с вторым и третьим входами шестого

элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ и J- и С-входами второго триггера регистрации, нулевой выход триггера стирания памяти соединен с вторым информационным входом коммутатора управления считьшанием и вторым входом второго элемента ИЛИ, выход которого является установочным выходом устройства и соединен с первыми информационными входами элементов 2И-Ш1И, единичные выходы триггеров записи соединены с группой информационных входов блока местного управления и входами шестого элемента РШИ, выход которого соединен с инверсными входами седьмого элемента ИЖ и десятого элемента И, а также с третьим информационным входом коммутатора управления считьшанием, выход каждого элемента И первой группы соединен с С-входом одноименного триггера записи, нулевой выход которого соединен с вторым входом одноименного элемента И первой группы, единичный выход каждого триггера записи, кроме последнего, соединен с третьим входом последующего элемента И первой группы и вторым информационным входом последунщего элемента 2И-ИЛИ, единичный выход последнего триггера записи соединен с вторым информационным входом первого элемента 2И-ИЛИ и прямым входом седьмого элемента ИЛИ, выход которого соединен с третьим входом первого элемента И первой группы, выходы элементов И второй группы соединены с первыми управляющими входами элементов 2И-ИЛИ, выходы которых соединены с R-входами соответствующих триггеров записи, выход каждого элемента И второй группы соединен с С-входом одноименного триггера считывания , нулевой выход которого соединен с вторым входом одноименного элемента И второй группы, единичный выход каждого триггера считывания, кроме последнего, соединен с третьим входом последующего элемента И второй группы, а также с вторым управляющим входом одноименного элемента 2И-ИЯИ, единичный выходпоследнего триггера считывания соединен с вторым управляющим входом последнего элемента 2И-ИЛИ и, первым информационным входом коммутатора управления сбросом, выход которого соединен с J, С- и К-входами триггера сброса, выход которого соединен с вторым информационным входом коммутатора управления сбросом и вторым входом пятого элемента ИЖ, выход десятого элемента И соединен с третьим входом пятого элемента ИЛИ, выход которого соединен с R-входами триггеров считывания, выходы элементов И второй группы соединены с входами восьмого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход последнего элемента И второй грзшпы соединен с С-входом триггера стирания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления с контролем | 1983 |

|

SU1156074A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для контроля микропрограмм | 1982 |

|

SU1034042A1 |

| Устройство для отображения информации | 1981 |

|

SU963082A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее блок памяти, блок синхронизации, блок местного управления, блок ввода данных, блок вывода данньпс, коммутатор управления считыванием, коммутатор управления выводом, первую и вторую группы элементов И, группу элементов РШИ, элементы .И с первого по десятый, элементы ИЛИ с первого по восьмой, причем вход сброса устройства соединен с входом блока синхронизации, выходы элементов И первой и второй групп соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходь которых соединены с адресными входами блока памяти, вход блока синхронизации является входом сброса устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены элементы 2И-ИЛИ, триггеры записи, триггеры считывания, коммутатор управления сбросом, триггер сброса, триггер стирания, первый и второй триггеры вьшода, триггер готовности, триггер запроса. первый и второй триггеры регистрации, причем вход сброса устройства соединен с первым входом сброса блока ввода данных и прямым входом первого элемента ИЛИ, выход которого соединен с R-входом триггера готовности, первый выход блока синхронизации соединен с первым управляющим входом коммутатора управления считыванием, второй выход - с первым входом первого элемента И, первыми входами синхронизации блока ввода данных, блока вывода данных и блока местного управления, выходы переполнения и контроля которого и первый вход второго элемента ИЛИ являются (Л выходом контроля устройства, третий выход блока синхронизации соединен с управляющим входом коммутатора управления сбросом, вторым входом синхронизации блока местного управления, первым инверсным входом, втог рого элемента И и первыми входами третьего-шестого элементов И, четвертый выход блока синхронизации СХ) соединен с вторым входом синхроо ;D эо низации блока ввода данных, вторым входом пятого элемента И и первьтм входом седьмого элемента И, вькод которого соединен с первыми входасо ми элементов И первой группы, пятый выход блока синхронизации соединен с третьим входом синхронизации блока ввода данных, инверсными управляющими входами коммутатора управления выводом и коммутатора управления считьгоанием, выход которого соединен с первыми входами элементов И второй группы, шестой выход блока синхронизации соединен с первым входом восьмого элемента И

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах обработки информации и контрольно-роварочных комплексах в качестве быстродействующих устройств, осуществляющих хранение, управление и контроль данных перед вьщачей их на регистрацию.

Целью изобретения является повыщение быстродействия и расширение области применения устройства.

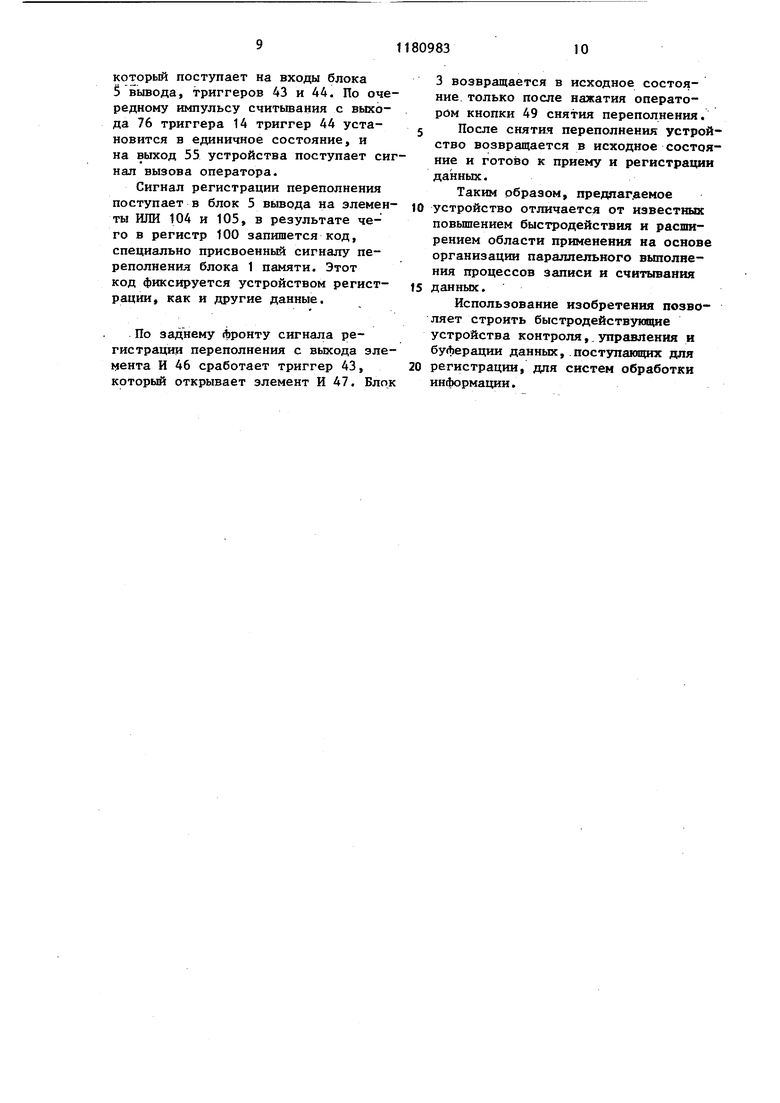

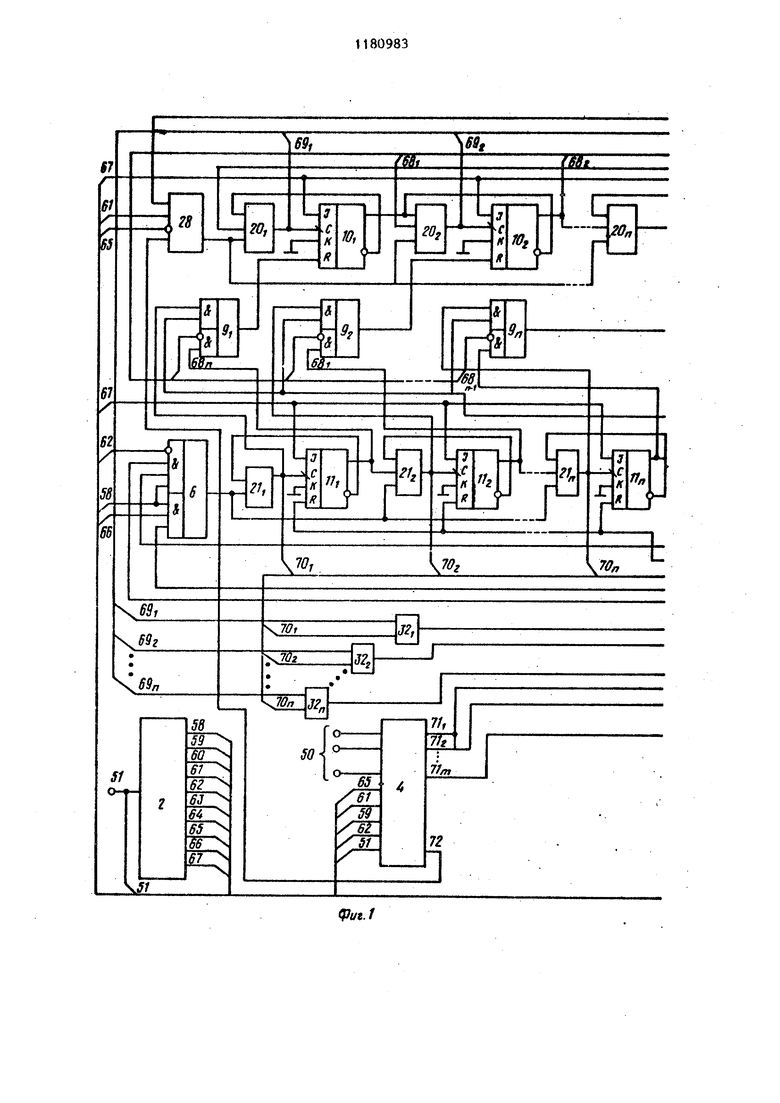

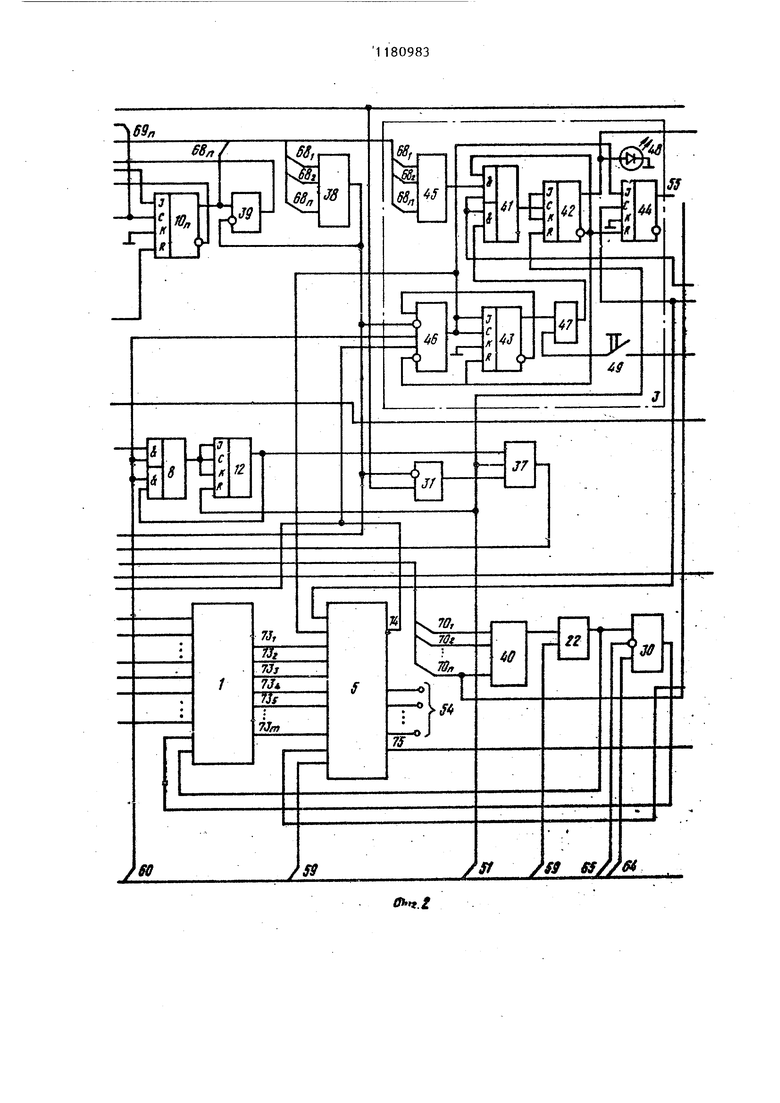

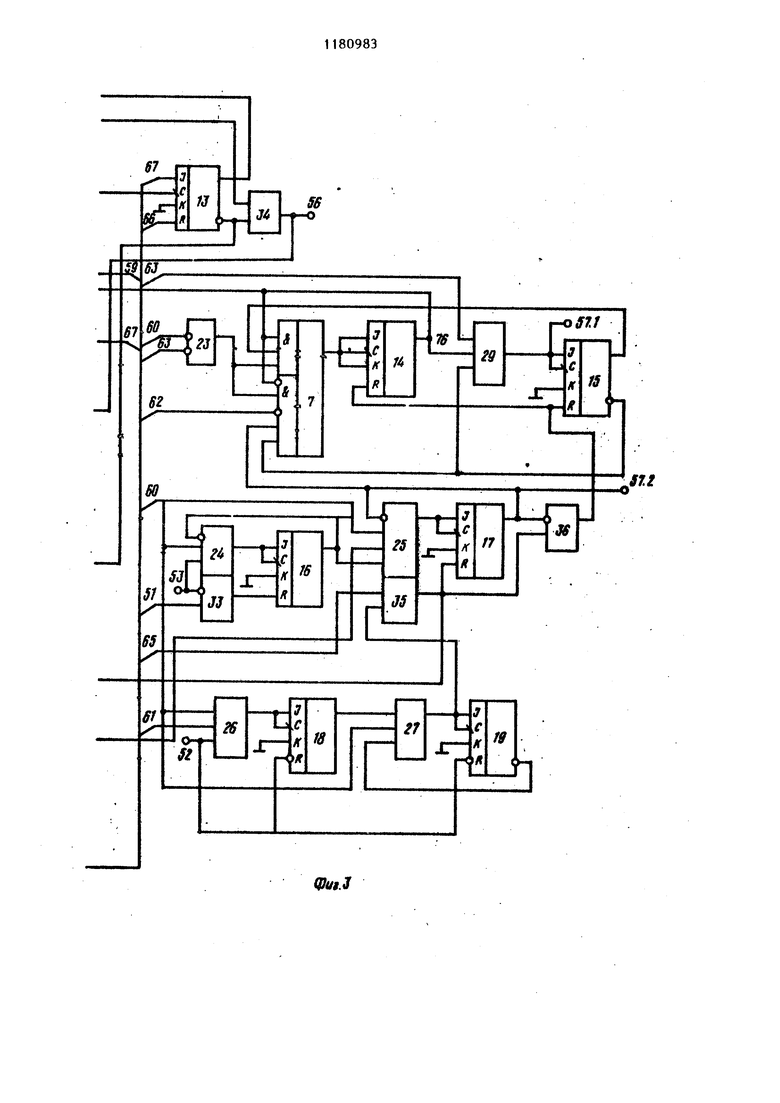

На фиг. 1-3 приведена функциональная схема устройстваJ на фиг. 4 .функциональная схема блока синхронизации; на фиг. 5 - функциональная ч:хема блока ввода данных, на фиг. фиг. 6 - функциональная схема блока вывода данных; на фиг. 7-9 временная диаграмма работы устройства; на фиг. 10 - функциональная схема (а) и временная диаграмма (б) работы блока сброса входящего в блок синхронизации.

Устройство содержит (фиг. 1-3) блок 1 памяти, блок 2 синхронизации, блок 3 местного управления, блок 4 ввода данных, блок 5 вьюода данньк, коммутатор 6 управпения считыванием, коммутатор 7 управления выводом, коммутатор 8 управления сбросном, элементы 2И-Ш1И ,, триггеры 10|-10п записи, триггеры 11,-llf, считьгоания, триггер 12 сброса, триггер 13 стирания, первый 14, второй 15 триггеры вывода, триггер 16 готовности, триггер 17 запроса, первый 18 и второй 19 триггеры регистрации, первую 20 и вторую 21 группы элементов И, первый 22, второй 23, третий 24, четвертьй 25, пятьй 26, шестой 27, седьмой 28, восьмой 29, девятый 30 и десятьй 31 элементы И, группу элементов ИЛИ 32, первый 33, второй 34, третий 35, четвертый 36, пятый 37, шестой 38, седьмсзй 39 и восьмой 40 элементы ИЛИ.

Кроме того, блок 3 местного управления содержит коммутатор 41 сигнала переполнения, первый 42 триггер переполнения, второй триггер 43 переполнения, триггер 44 сигнализации, одиннадцатый 45, двенадцатый 46 и тринадцатый 47 элементы И, светодиод 48 и кнопку 49 снятия переполненияi группу 50 информационных входов устройства, вход 51 сброса устройства, вход 52 запрещения регистрации, вход 53 разрешения регистрации, группу 54 информационных выходов, вькод 55 контроля, выход 56 обнуления, группу 57 управляющих выходов, состоящую из выхода 57( маркера данных и выхода 572 запроса, выходы 58-64 синхронизации блока 2 синхронизации, выходы 65 и 66 сброса блока 2 синхронизации, вькод 67 логической единицы блока синхронизации, выходы 68(-68п триггеров записи, выходы элементов И первой группы 20 элементов И, выходы 70j-70| элементов И второй группы 21, группу 71 i|-71 (IJ информационных выходов блока 4 ввода, выход 72.наличия данных блока 4 ввода, выходы 73 73 блока 1 памяти, первый информационный выход 74 блока 5 вывода, второй информационный выход 75 блока 5 вывода, выход 76 первого триггера 14 вьшода, выход 77 элемента

1809834

ИЛИ 39, вькод 78 регистрации переполнения .

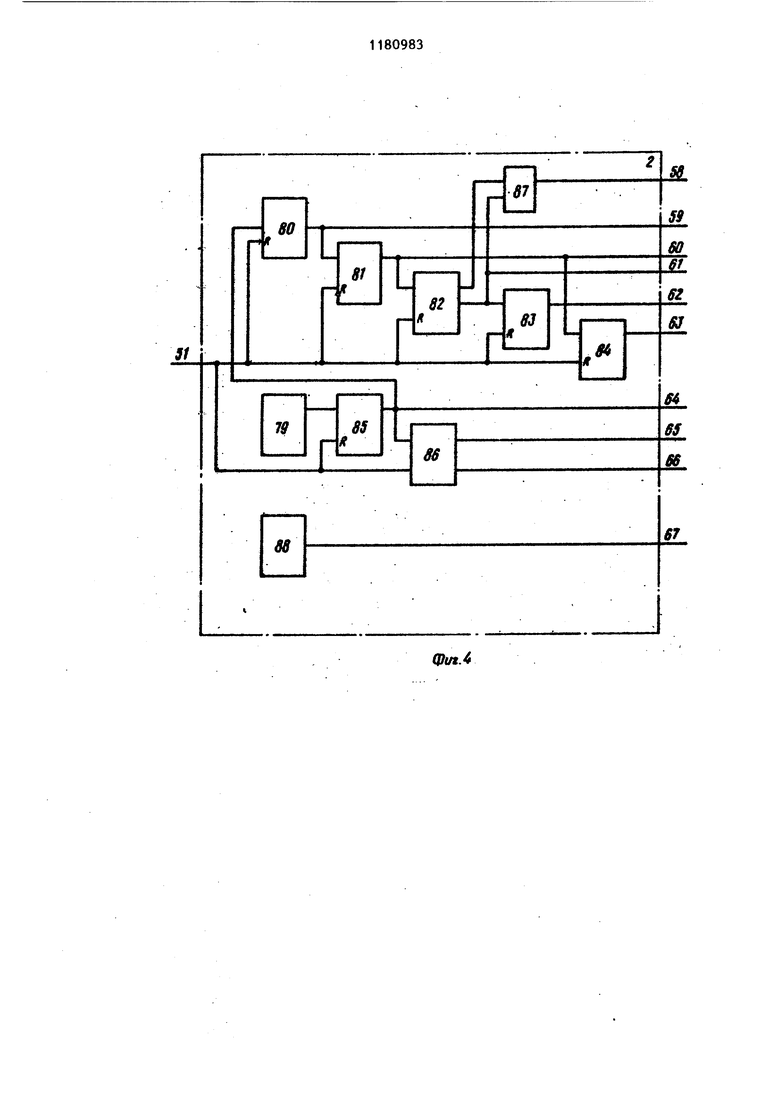

Блок 2 (фиг. 4) содержит генератора 79 тактовых импульсов, счетчики 80-85, блок 86 сброса, четырнадцатьй элемент И 87 и генератор 88 единицы.

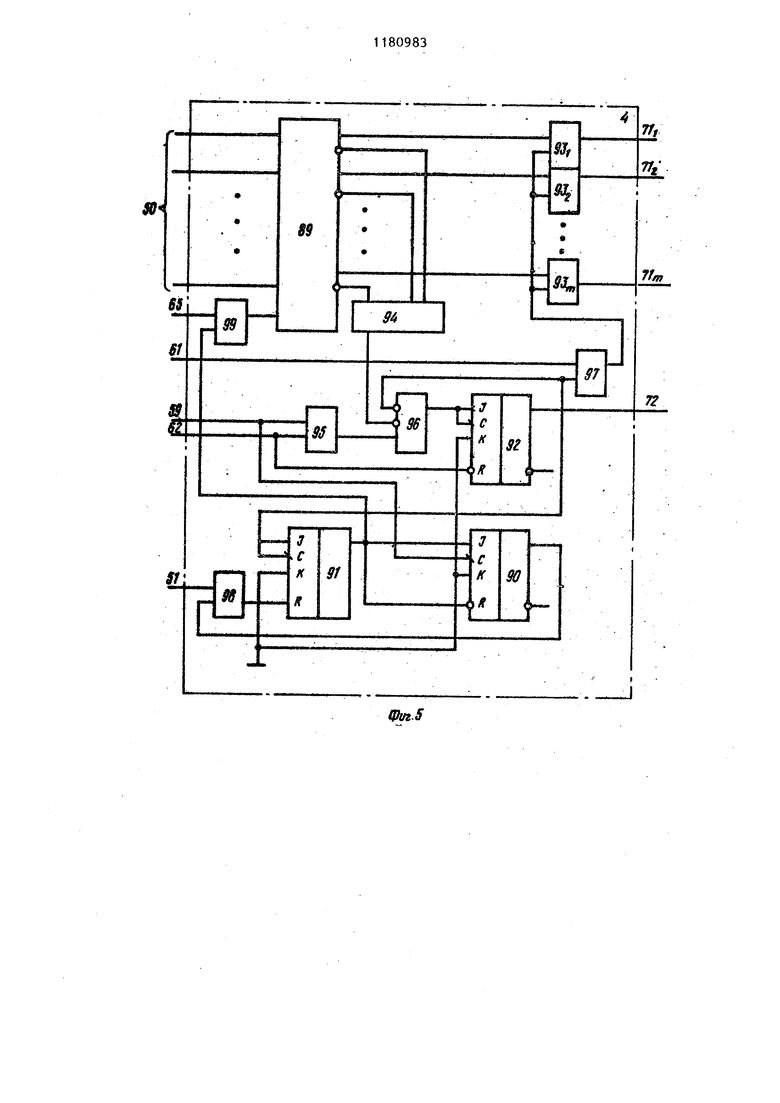

Блок 4 ввода данных (фиг. 5) содержит регистр 89, триггеры 9010 92, элементы И 93|-93 элементы И с пятнадцатого по восемнадцатый, девятый 98 и десятый 99 элементы ШШ.

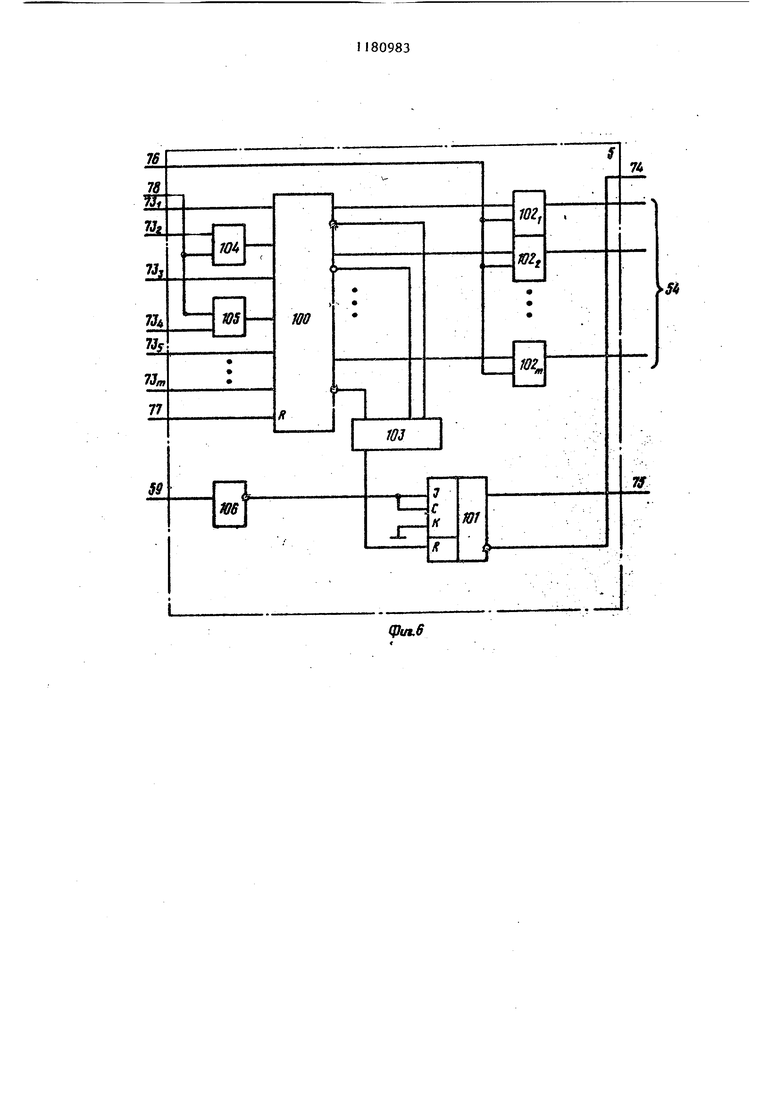

Блок 5 (фиг, 6) содержит регистр ts 100, триггер 101, группу элементов И 102, девятнадцатый элемент И 103, одиннадцатьй 104 и двенадцатьй 105 элементы ИЛИ и элемент НЕ 106

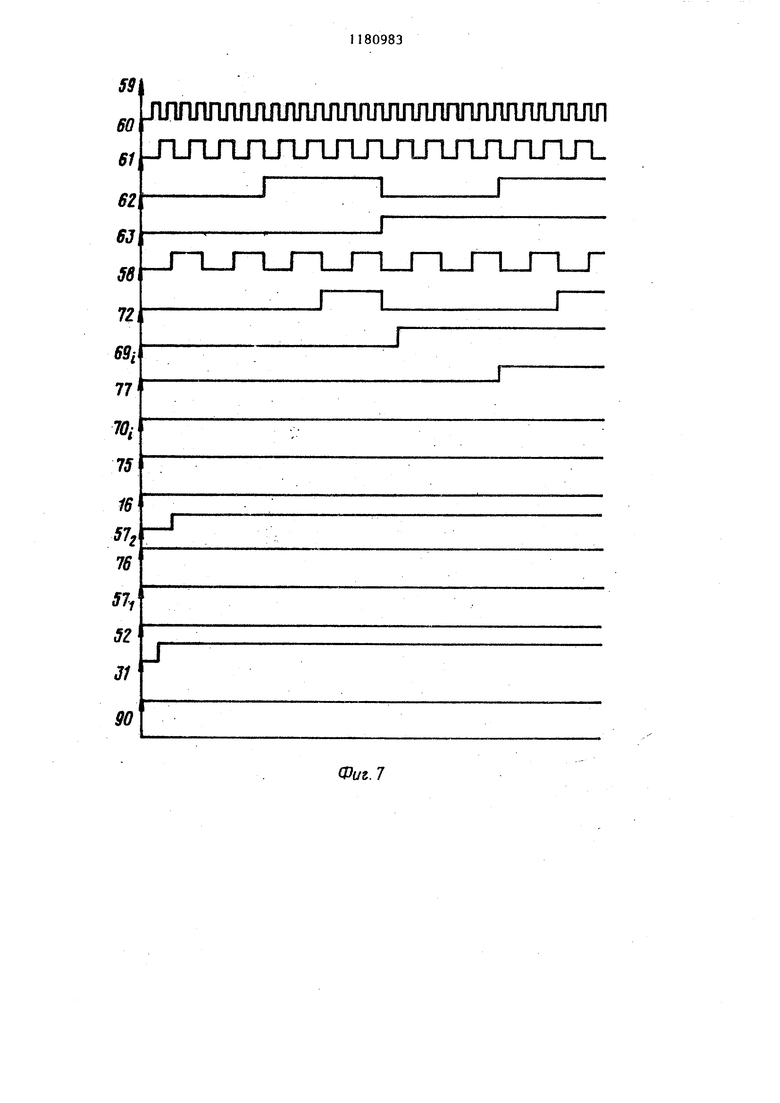

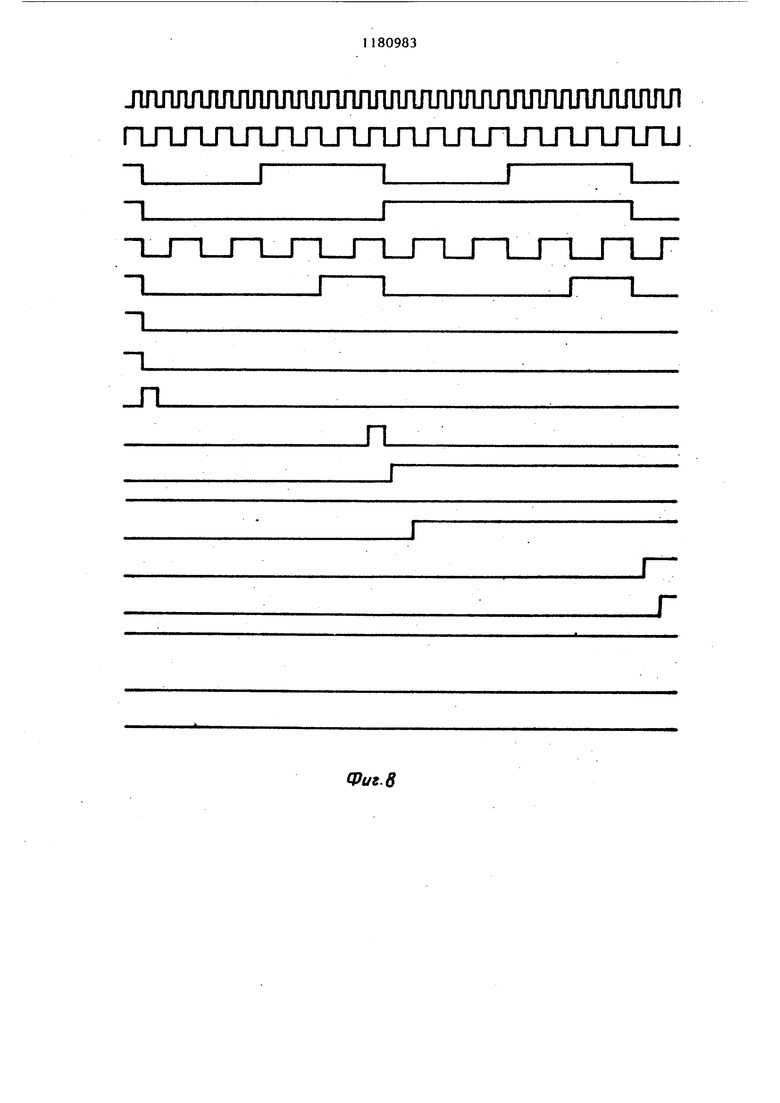

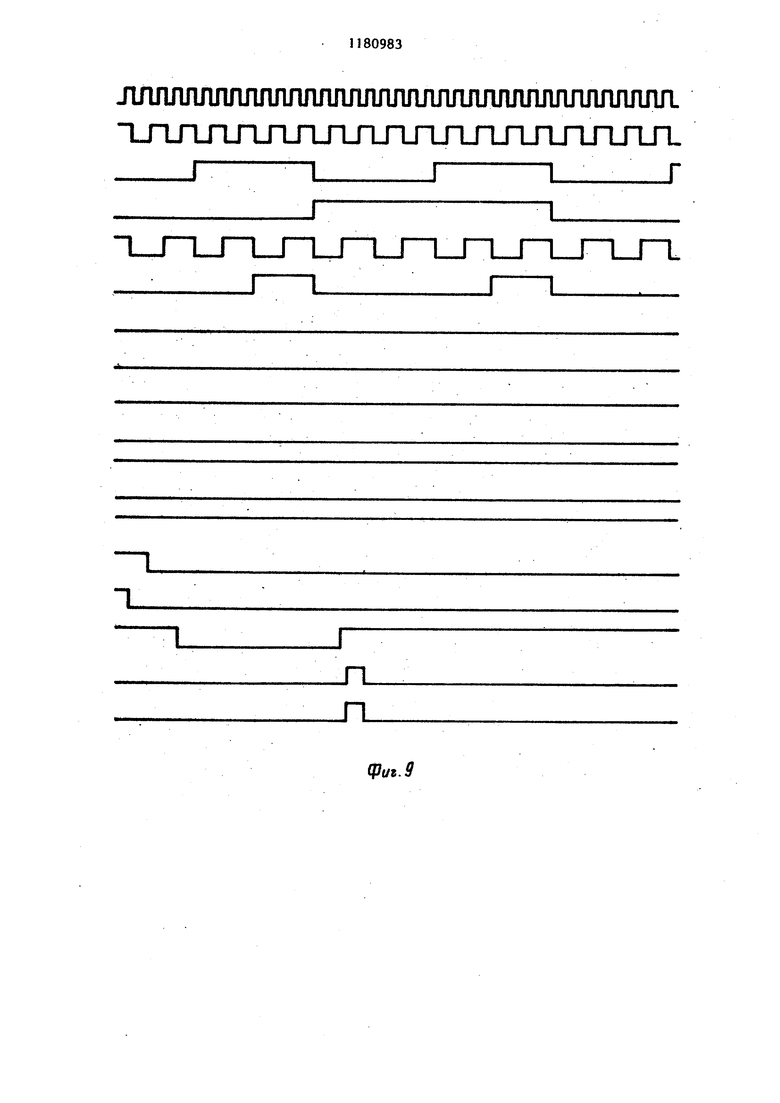

20 На временной диаграмме (фиг. 79), описывающей работу устройства, нумерация сигналов соответствует номерам выходов элементов, либо номерам элементов, с выходов которых они снимаются в соответствии с обозначениями, принятыми на функциональной схеме устройства (фиг. 1-3).

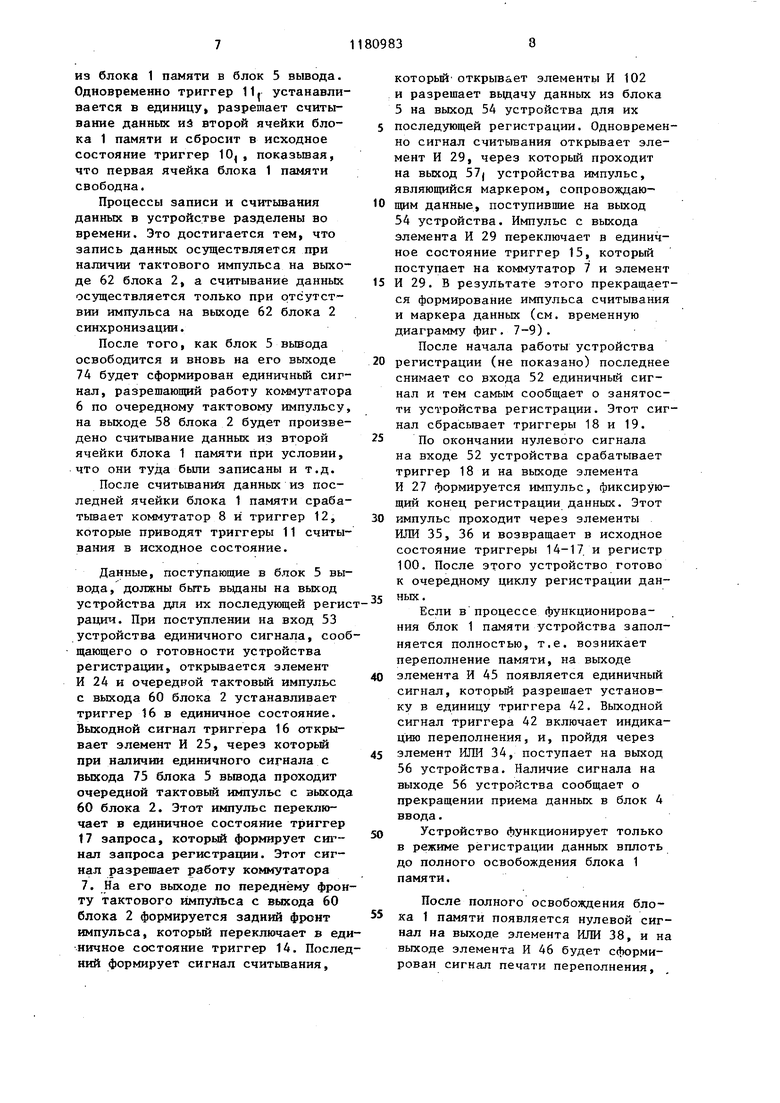

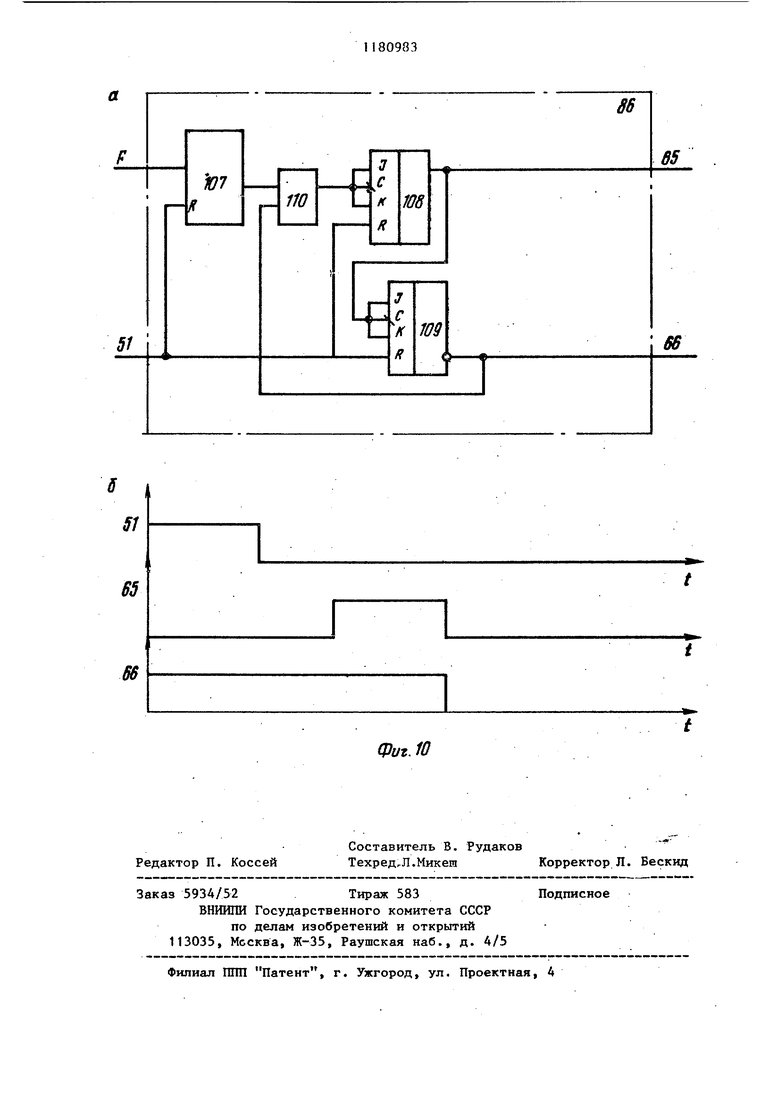

Блок 86 сброса (фиг. 10 а) содержит счетчик 107, триггеры 108 и 109, двадцатый элемент И 110. На фиг. 106 приведена временная диаграмма работы блока 86 сброса, обозначения на которой соответствуют

35 принятым на фиг. 10 а.

Рассмотрим функционирование устройства .

После подачи питания на устройство начинается процесс его установки в исходное состояние. Для этого на его вход 51 подается сигнал ,общего сброса, которьй приводит IB исходное состояние счетчики 80-85, блок 86 сброса, триггеры 11 считывания, триггер 12 сброса, первьй триггер 42 переполнения, триггер 16 готовности и триггер 91. После снятия сигнала сброса со входа 51 устройства начинается режим автоматического сброса устройства. Блок 86 сброса вырабатывает на выходах 65 и 66 блока 2 сигналы сброса (см. временную диаграмму на фиг. 106). Одновременно в блоке 2

55 начинают вырабатываться тактовые импульсы на выходах 58-64 в соответствии с временной диаграммой, приведенной на фиг. 7-9.

Сигнал сброса на выходе 65 блока 2 устанавливает в исходное состояние регистр 89, триггеры 14-17, регистр 100. Сигнал сброса на выходе 66 блока 2 устанавливает в ноль триггер 13 и разрешает работу коммутатора 6. Триггер 13 сигналом с инверсного выхода через элемент ИЛИ ЗА разрешает прохождение сигналов сброса через элементы 9 на триггеры 10 и открьшает коммутатор 6. Через последний проходят тактовые импульсы с выхода 58 блока 2, которые последовательно очищают блок 1 памяти, считывая информацию из всех его ячеек и приводят в исходное состояние триггеры 10. Пр этом триггеры 11 устанавливаются в единичное состояние. После срабатывания последнего триггера 11 сигнал с его выхода поступает на коммутатор 8, который, управляя триггером 12, приводит в исходное состояние все триггеры 11. Одновременно сигнал с единичного выхода последнего триггера 11 поступает на вход С триггера 13 и задним фротом переводит его в единичное состояние, которьй открывает элемент И 28 и коммутатор 6 переводит в рабочий режим. На этом режим установки исходного состояния заканчивается и устройство переходит в рабочий режим.

Устройство находится в режиме ожидания до момента поступления данных на группу 50 информационных входов, которые поступают на входы блока 4 ввода. Поступившие данные записываются в регистр 89. После этого триггер 92, контролирующий поступление данных в блок 4 ввода, переключается в единицу, разрешает вьщачу поступивших данных на выходы 71 блока 4 и выдает единичный сигнал на его выход 72.

Сигнал с выхода 72 блока 4 поступает на вход элемента И 28 и разрешает прохождение тактового импульса с выхода 61 блока 2 через элементы И 28 и И 20 на вход С триггера 10 и первый адресньй вхо блока 1 памяти. В результате этого данные, находящиеся в блоке 4 ввода, будут записаны в первую ячейку памяти блока 1. По заднему фронту актового импульса на выходе 62

блока 2 триггер 92 возвращается в исходное состояние и по заднему фронту импульса на его выходе переключится в единичное состояние триггер 91. Последний формирует сигнал сброса, который приводит в исходное состояние регистр 89 и тем самым подготовляет.его к очередному приему данных. После этого по очередному тактовому импульсу с выхода 59 блока 2 срабатывает триггер 90, который возвращает триггер 91 в исходное состояние, 5 после чего выходным сигналом триггера 91 он сам будет возвращен в исходное состояние. После этого блок 4 ввода готов к очередному приему данных.

0 Триггер lOj, сработав, зафиксирует факт записи данных в первую ячейку и разрешает запись данных во вторую ячейку. Одновременно на выходе элемента ИЛИ 38 появляется

5 единичный сигнал, информирующий о наличии данных в блоке 1 памяти устройства.

При очередном поступлении данных в блок 4 ввода на его выходе 72

0 появляется единичный сигнал, по которому будет сформирован сигнал на выходе элемента И 20 и осуществлена запись данных во вторую ячейку блока 1 памяти. Триггер 20,

5 сработав, разрешает запись очередной порции данных третью ячейку блока 1 памяти. Таким образом, в устройстве осуществляется приоритет записи данных в свободную ячейку

0 блока 1 памяти, имеющую меньший порядковый номер. После записи данных в ячейку с номером 12 выходным сигналом последнего триггера 10 через элемент ИЛИ 39 будет разрешена

j запись данных в первую ячейку при условии, что к этому моменту из нее произведены считывание и регистрация данных, записанных ранее.

Единичньй сигнал на выходе элемента ИЛИ 38 свидетельствует о наличии данных в памяти и разрешает работу коммутатора 6.

По тактовому импульсу с выхода 58 блока 2 происходит считывание данных из первой ячейки блока 1 па5

мяти.

Под воздействием указанных сигналов происходит считывание данных

из блока 1 памяти в блок 5 вывода. Одновременно триггер 11. устанавливается в единицу, разрешает считывание данных иЗ второй ячейки блока 1 памяти и сбросит в исходное состояние триггер 10, показывая, что первая ячейка блока 1 памяти свободна.

Процессы записи и считывания данных в устройстве разделены во времени. Это достигается тем, что запись данных осзпцествляется при наличии тактового импульса на выходе 62 блока 2, а считывание данных осуществляется только при отсутствии импульса на выходе 62 блока 2 синхронизации.

После того, как блок 5 вывода освободится и вновь на его выходе 74 будет сформирован единичный сигнал, разрешаю1Щ1й работу коммутатора 6 по очередному тактовому импульсу на выходе 58 блока 2 будет произведено считывание данных из второй ячейки блока 1 памяти при условии, что они туда были записаны и т.д.

После считьшанися данных из последней ячейки блока 1 памяти срабатьюает коммутатор 8 и триггер 12, которые приводят триггеры 11 считывания в исходное состояние.

Данные, поступающие в блок 5 вывода, должны быть выданы на выход устройства дпя их последующей регисрации. При поступлении на вход 53 устройства единичного сигнала, сообщающего о готовности устройства регистрации, открывается элемент И 24 и очередной тактовьй импульс с выхода 60 блока 2 устанавливает триггер 16 в единичное состояние. Выходной сигнал триггера 16 открывает элемент И 25, через который при наличии единичного сигнала с выхода 75 блока 5 вьшода проходит очередной тактовый импульс с выхода 60 блока 2. Этот импульс переключает в единичное состояние триггер 17 запроса, которьй формирует сигнал запроса регистрации. Этот сигнал разрешает работу коммутатора 7. На его выходе по переднему фронту тактового импульса с выхода 60 блока 2 формируется задний фронт импульса, который переключает в единичное состояние триггер 14. Последний формирует сигнал считьгоания.

которьй открывает элементы И 102 и разрешает вьщачу данных из блока 5 на выход 54 устройства для их последующей регистрации. Одновременно сигнал считывания открывает элемент И 29, через который проходит на выход 57) устройства импульс, являющийся маркером, сопровождающим данные, поступившие на выход 54 устройства. Импульс с выхода элемента И 29 переключает в единичное состояние триггер 15, которьй поступает на коммутатор 7 и элемент

И 29. В результате этого прекращается формирование импульса считывания и маркера данных (см. временную диаграмму фиг. 7-9).

После начала работы устройства

регистрации (не показано) последнее снимает со входа 52 единичньй сигнал и тем самым сообщает о занятости устройства регистрации. Этот сигнал сбрасьшает триггеры 18 и 19.

По окончании нулевого сигнала на входе 52 устройства срабатывает триггер 18 и на выходе элемента И 27 формируется импульс, фиксирующий конец регистрации данных. Этот

импульс проходит через элементы ИЛИ 35, 36 и возвращает в исходное состояние триггеры 14-17 и регистр 100. После этого устройство готово к очередному циклу регистрации данных.

Если в процессе функционирования блок 1 памяти устройства заполняется полностью, т.е. возникает переполнение памяти, на выходе

элемента И 45 появляется единичный сигнал, которьй разрешает установку в единицу триггера 42. Выходной сигнал триггера 42 включает индикацию переполнения, и, пройдя через

элемент ИЛИ 34, поступает на выход 56 устройства. Наличие сигнала на выходе 56 устройства сообщает о прекращении приема данных в блок 4 ввода.

Устройство функционирует только в режиме регистрации данных вплоть до полного освобождения блока 1 памяти.

После полного освобождения блока 1 памяти появляется нулевой сигнал на выходе элемента ИЛИ 38, и на выходе элемента И 46 будет сформирован сигнал печати переполнения.

который поступает на входы блока 5 вывода, триггеров 43 и 44. По очередному импульсу считьшания с выхода 76 триггера 14 триггер 44 установится в единичное состояние, и на выход 55 устройства поступает сигнал вызова оператора.

Сигнал регистрации переполнения поступает в блок 5 вывода на элементы ИЛИ 104 и 105, в результате чего в регистр 100 запишется код, специально присвоенный сигналу переполнения блока 1 памяти. Этот код фиксируется устройством регистрации, как и другие данные.

По заднему фронту сигнала регистрации переполнения с выхода эленента И 46 сработает триггер 43, который открывает элемент И 47. Блок

3 возвращается в исходное состояние только после нажатия оператором кнопки 49 снятия переполнения. 5 После снятия переполнения устройство возвращается в исходное состояние и готово к приему и регистрации данных.

Таким образом, предлагаемое

0 устройство отличается от известных повьщ1ением быстродействия и расширением области применения на основе организации параллельного выполнения процессов записи и считывания

5 данных.

Использование изобретения позволяет строить быстродействующие устройства контроля,, управления и буферации данных,.поступающих для

0 регистрации, для систем обработки информации.

ЛППЛПЛЛПЛЛЛЛШШТЛЛ

ГLrlЛJ JlЛJlJlллJ

62 63 Ив 721 69i 77

Щ 15

16 57, 76

57, 52 31

90

Фиг.

JШЛЛЛЛЛJlШlЛЛnJШЛЛJШЛЛnJШЛnn

rinJinjiJiJiJiJiri

1

п

J L

Фиг. 8

ЛПШ1ШШПЛЛЛЛЛЛЛЛЛЛЛШи1ЛЛЛЛ IJTJTJlJTJTJTnJlJ

г I I г

J L

JT

п

J 1

(Put. 9

Фиг. 10

| Устройство для управления печатью | 1981 |

|

SU985779A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964639A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-01-06—Подача