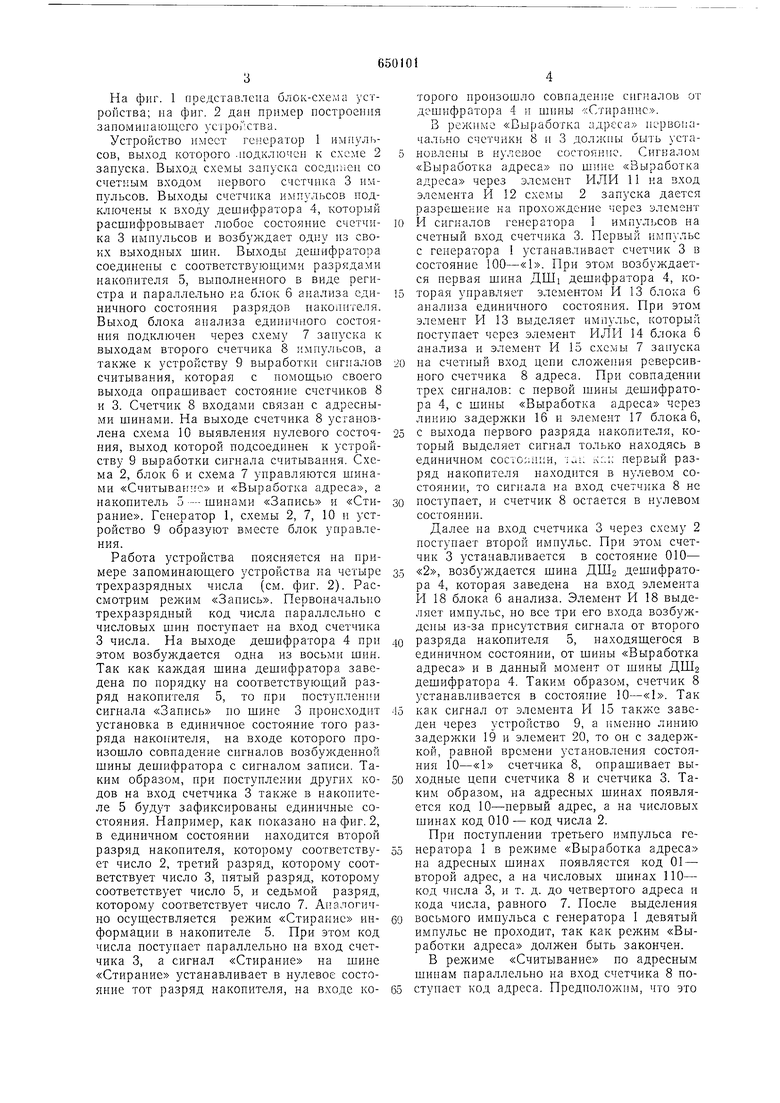

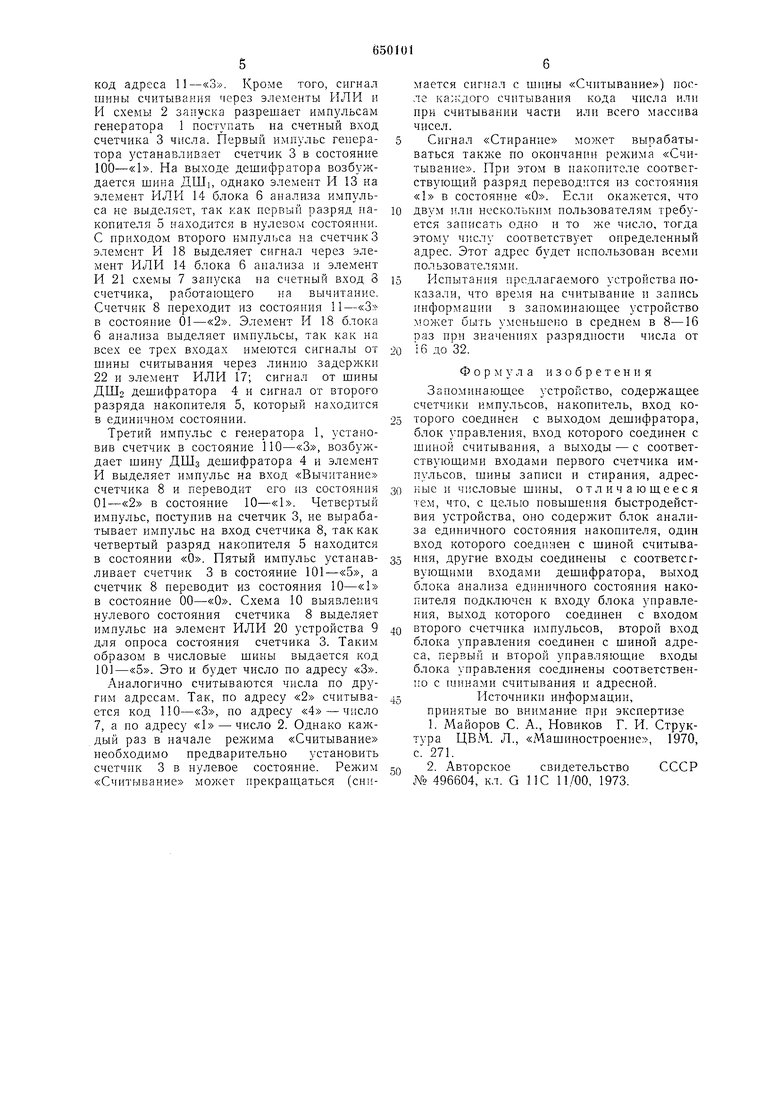

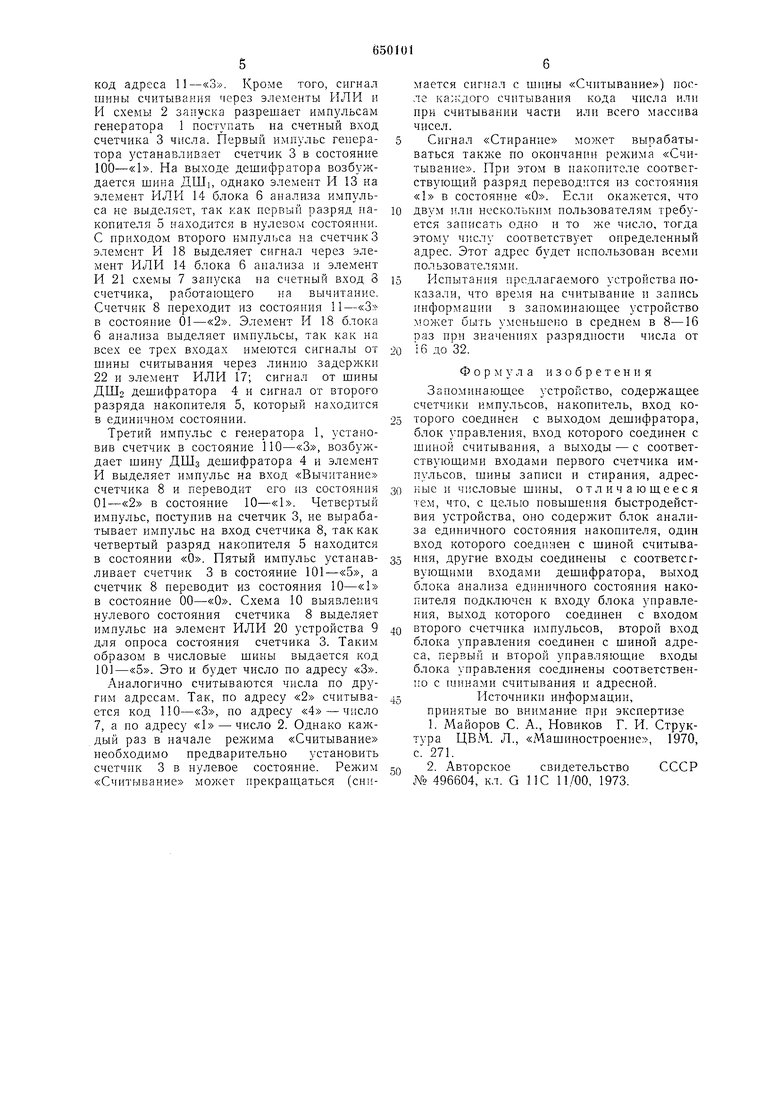

На фиг. 1 представлена блок-схема устройства; на фиг. 2 дан пример построения запомииаюпцего устройства.

Устройство имеет генератор 1 импульсов, выход которого людключен к схеме 2 запуска. Выход схемы запуска соединен со счетным входом первого счетчика 3 импульсов. Выходы счетчика импульсов подключены к входу дешифратора 4, который расшифровывает любое состояпие счетчика 3 импульсов и возбуждает одну из своих выходных шин. Выходы дешифратора соединены с соответствующими разрядами накопителя 5, выполненного в виде регистра и параллельно на блок 6 анализа единичного состояния разрядов накопителя. Выход блока анализа единичного состояния подключен через схему 7 запуска к выходам второго счетчика 8 импульсов, а к устройству 9 выработки сигналов считывания, которая с помош,ью своего выхода опрашивает состояние счетчиков 8 и 3. Счетчик 8 входами связан с адресными шинами. На выходе счетчика 8 усгано;злена схема 10 выявления нулевого состояния, выход которой подсоединен к устройству 9 выработки сигнала считывания. Схема 2, блок 6 и схема 7 управляются шинами «Считывашгс и «Выработка адреса, а накопитель 5 - шинами «Запись и «Стирание. Генератор 1, схемы 2, 7, 10 и устройство 9 образуют вместе блок управления.

Работа устройства поясняется на примере запоминаюш,его устройства на четыре трехразрядных числа (см. фиг. 2). Рассмотрим режим «Запись. Первоначаотыю трехразрядный код числа параллельно с числовых шин поступает на вход счетчика 3 числа. На выходе дешифратора 4 при этом возбуждается одна из восьми шин. Так как каждая шина дешифратора заведена по порядку на соответствуюш,ий разряд накопителя 5, то при поступлении сигнала «Запись по шине 3 происходит установка в единичное состояние того разряда накопителя, на входе которого произошло совпадение снгналов возбужденной шины дешифратора с сигналом записи. Таким образом, нри поступлении других кодов на вход счетчика 3 также в накопителе 5 будут зафиксированы единичные состояния. Например, как показано на фиг. 2, в единичном состоянии находится второй разряд накопителя, которому соответствует число 2, третий разряд, которому соответствует число 3, пятый разряд, которому соответствует число 5, и седьмой разряд, которому соответствует число 7. Аналогично осундествляется режим «Стирание информации в накопителе 5. При этом код числа поступает параллельно на вход счетчика 3, а сигнал «Стирание на шине «Стирание устанавливает в нулевое состояние тот разряд накопителя, на входе которого произошло совпадение сигналов от дешифратора 4 и шины -хСтиранне.

В режиме «Выработка адреса первоначально счетчики 8 и 3 должны быть установлены в нулевое состояние. Сигналом «Выработка адреса по шине «Выработка адреса через элемент ИЛИ 11 на вход элемента И 12 схемы 2 запуска дается разрешение ка прохождение через элемент

К) И сигналов генератора 1 импульсов на счетный вход счетчика 3. Первый имп}льс с генератора 1 устанавливает счетчик 3 в состояние 100-«1. При этом возбуждается нервая шина ДШ1 дешифратора 4, которая управляет элементом И 13 блока 6 аналнза единичного еостояния. При этом элемент PI 13 выделяет импульс, который поступает через элемент ИЛИ 14 блока 6 анализа и элемент И 15 схемы 7 запуска

0 на счетный вход цени сложения реверсивного счетчика 8 адреса. При совпадении трех сигналов: с первой шины дешифратора 4, с шины «Выработка адреса через линию задержки 16 и элемент 17 блока 6,

5 с выхода первого разряда накопителя, который выделяет сигнал только находясь в единичном состо;;и1;и, iuu K;.I; первый разряд накопителя находится в нулевом состоянии, то сигнала на вход счетчика 8 не

0 поступает, и счетчик 8 остается в нулевом состоянии.

Далее на вход счетчика 3 через схему 2 поступает второй импульс. При этом счетчик 3 устанавливается в состояние 010-

5 «2, возбуждается шина ДШ2 дешифратора 4, которая заведена на вход элемента И 18 блока 6 анализа. Элемент И 18 выделяет имнульс, но все три его входа возбуждены из-за присутствия сигнала от второго

0 разряда накопителя 5, иаходяшегося в единичном состоянии, от шины «Выработка адреса и в данный момент от шины ДШ2 дешифратора 4. Таким образом, счетчик 8 устанавливается в состояние 10-«1. Так

5 как сигнал от элемента И 15 также заведен через устройство 9, а именно линию задержки 19 и элемент 20, то он с задержкой, равной времени установления состояния 10-«1 счетчика 8, онрашивает вы0 ходные цепи счетчика 8 и счетчика 3. Таким образом, на адресных шинах появляется код 10-первый адрес, а на числовых шинах код 010 - код числа 2. При поступлении третьего импульса генератора 1 в режиме «Выработка адреса на адресных шинах появляется код 01 - второй адрес, а на числовых шинах 110- код числа 3, и т. д. до четвертого адреса и кода числа, равного 7. После выделения 0 восьмого импульса с генератора 1 девятый импульс не проходит, так как режим «Выработки адреса должен быть закончен.

В режиме «Считывание по адресным

шинам параллельно на вход счетчика 8 поступает код адреса. Предположим, что это 5 код адреса 11-«3. Кроме того, сигнал шины считывания через элементы ИЛИ и И СхХемы 2 запуска разрешает импульсам генератора 1 поступать на счетный вход счетчика 3 числа. Первый импульс генератора устанавливает счетчик 3 в состояние 100-«1. На выходе дешифратора возбуждается шина ДШь однако элемент И 13 на элемент ИЛИ 14 блока 6 анализа импульса не выделяет, так как первый разряд накопителя 5 находится в нулевом состоянии. С приходом второго импульса на счетчик 3 элемент И 18 выделяет сигнал через элемент ИЛИ 14 блока 6 анализа и элемент И 21 схемы 7 запуска на счетный вход 3 счетчика, работаюидего на вычитание. Счетчик 8 переходит из состояния 11-«3 в состояние 01-«2. Элемент И 18 блока 6 анализа выделяет импульсы, так как на всех ее трех входах имеются сигналы от шины считывания через линию задерл%;ки 22 и элемент ИЛИ 17; сигнал от шины ДШо дешифратора 4 и сигнал от второго разряда накопителя 5, который находится в единичном состоянии. Третий импульс с генератора 1, установив счетчик в состояние 110-«3, возбуждает шину ДШз дешифратора 4 и элемент И выделяет импульс на вход «Вычитание счетчика 8 и переводит его из состояния 01-«2 в состояние 10-«1. Четвертый импульс, поступив на счетчик 3, не вырабатывает импульс на вход счетчика 8, так как четвертый разряд накопителя 5 находится в состоянии «О. Пятый импульс устанавливает счетчик 3 в состояние 101-«5, а счетчик 8 переводит из состояния 10-«1 в состояние 00-«О. Схема 10 выявления нулевого состояния счетчика 8 выделяет импульс на элемент ИЛИ 20 устройства 9 для опроса состояния счетчика 3. Таким образом в числовые шины выдается код 101-«5. Это и будет число по адресу «3. Аналогично считываются числа по другим адресам. Так, по адресу «2 считывается код ПО-«3, по адресу «4 - число 7, а по адресу «1 - число 2. Однако каждый раз в начале режима «Считывание необходимо предварительно установить счетчик 3 в нулевое состояние. Режим «Считывание может прекращаться (снпмается сигнал с шины «Считывание) после ка;кдого считывания кода числа или при считывании части или всего массива чисел. Сигнал «Стирание может вырабатываться также по окончании «Считывание. При этом в накопителе соотвегствуюший разряд переводится из состояния «Ь в состояние «О. Есл1 , что двум или нескольким пользователям требуется записать одно и то же число, тогда этому числу соответствует определенный адрес. Этот адрес будет использован всеми пользователями. Испытания предлагаемого устройства показали, что время на считывание и заиись информации 3 запоминаюи,ее устройство может быть уменьшено в среднем в 8-16 раз при значениях разрядности числа от i6 до 32. Формула и 3 о б р е т е н н я Запоминаюш,ее устройство, содержащее счетчики имнульсов, накопитель, вход которого соединен с вы.ходом дешифратора, блок управления, вход которого соединен с шиной считывания, а выходы - с соответствующими входами первого счетчика импульсов, шины записи и стирания, адресные и числовые шины, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит блок анализа единичного состояния накоиителя, один вход которого соединен с щиной считывания, другие входы соединены с соответсгвующими входами дещифратора, выход блока анализа единичного состояния накопителя подключен к входу блока управления, выход которого соединен с входом второго счетчика импульсов, второй вход блока управления соединен с шиной адреса, первый и второй уиравляющие входы блока управления соединены соответственно с плииами считывания и адресной. Источники информации, принятые во внимание при экспертизе 1.Майоров С. А., Новиков Г. И. Структура ЦВМ. Л., «Машиностроение, 1970, с 271. 2.Авторское свидетельство СССР № 496604, кл. G ПС 11/00, 1973. Счи1Т1ы1он:.е

MUJj ДШг ПШз quit ДШ5 ДШ-/ fs

пш дшз aiis ДШ7

- дщ f niis l дч/g

цш

А/9v,К

ilucnaSbie шины

Э

,-1

AdpecMiiie шин

фиг. г Ы

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1973 |

|

SU496604A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

Авторы

Даты

1979-02-28—Публикация

1973-01-29—Подача