Изобретение относится к вычислительной технике, в частности к устройствам обмена данными и может быть использовано в качестве буфера данных для каналов ввода-вывода ЭВМ.

Целью изобретения является повышение быстродействия устройства.

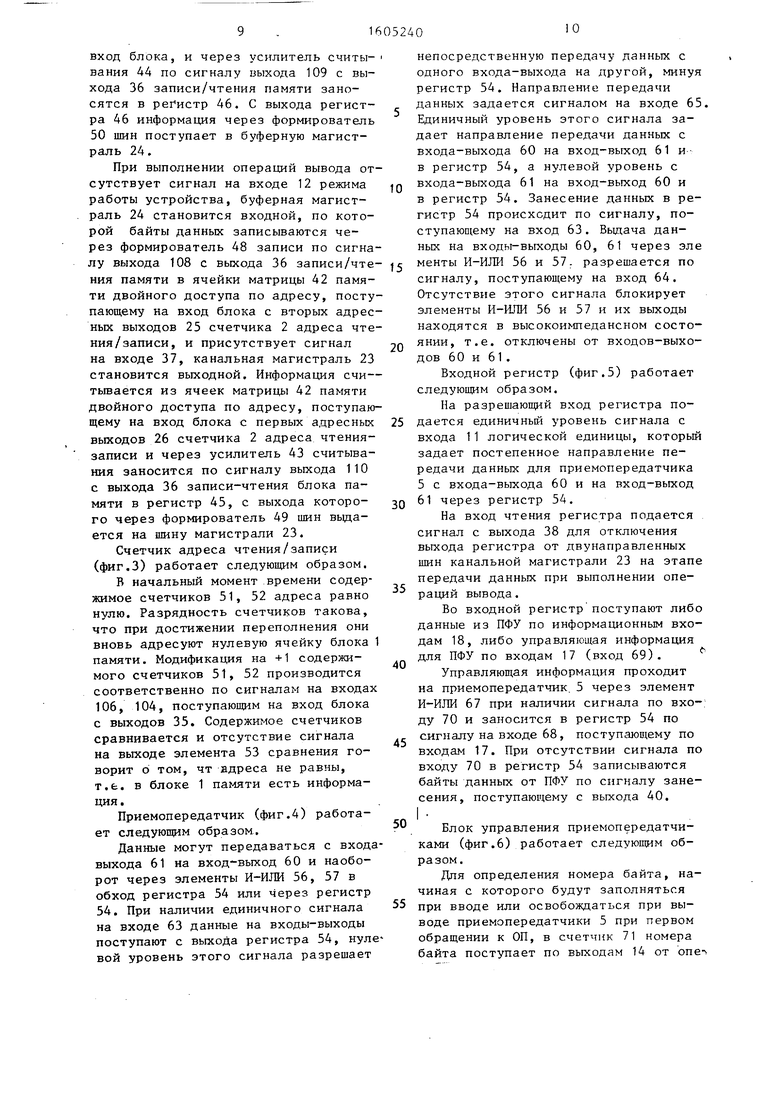

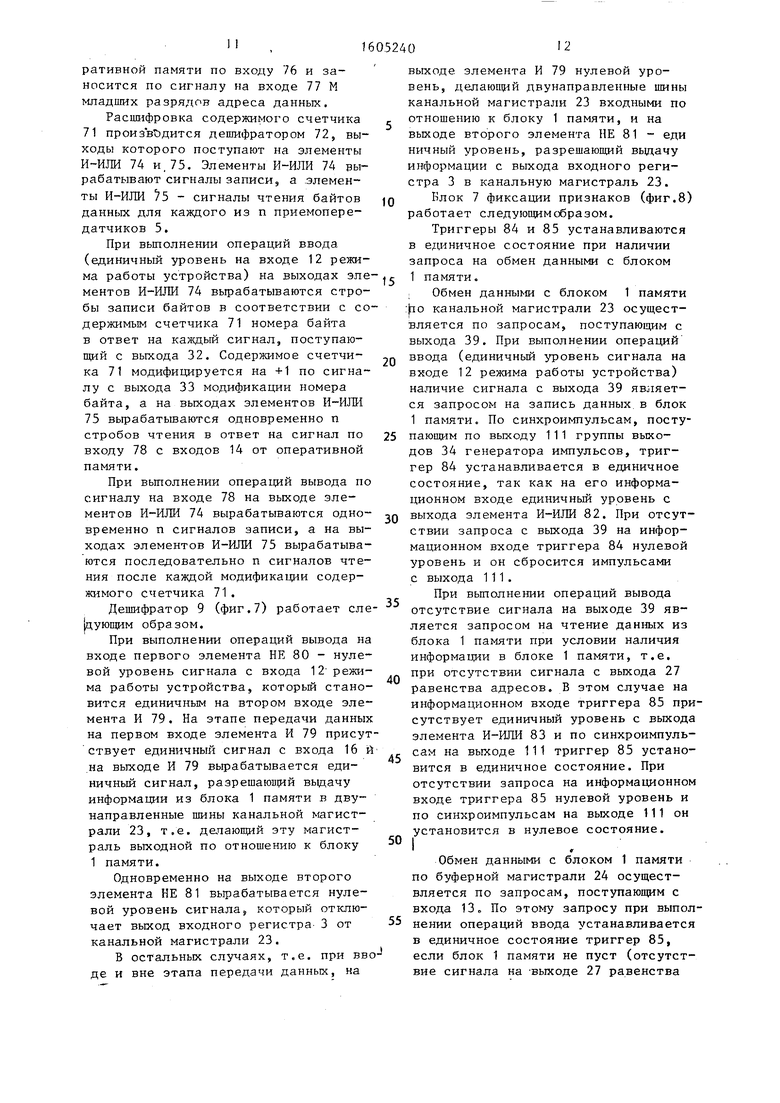

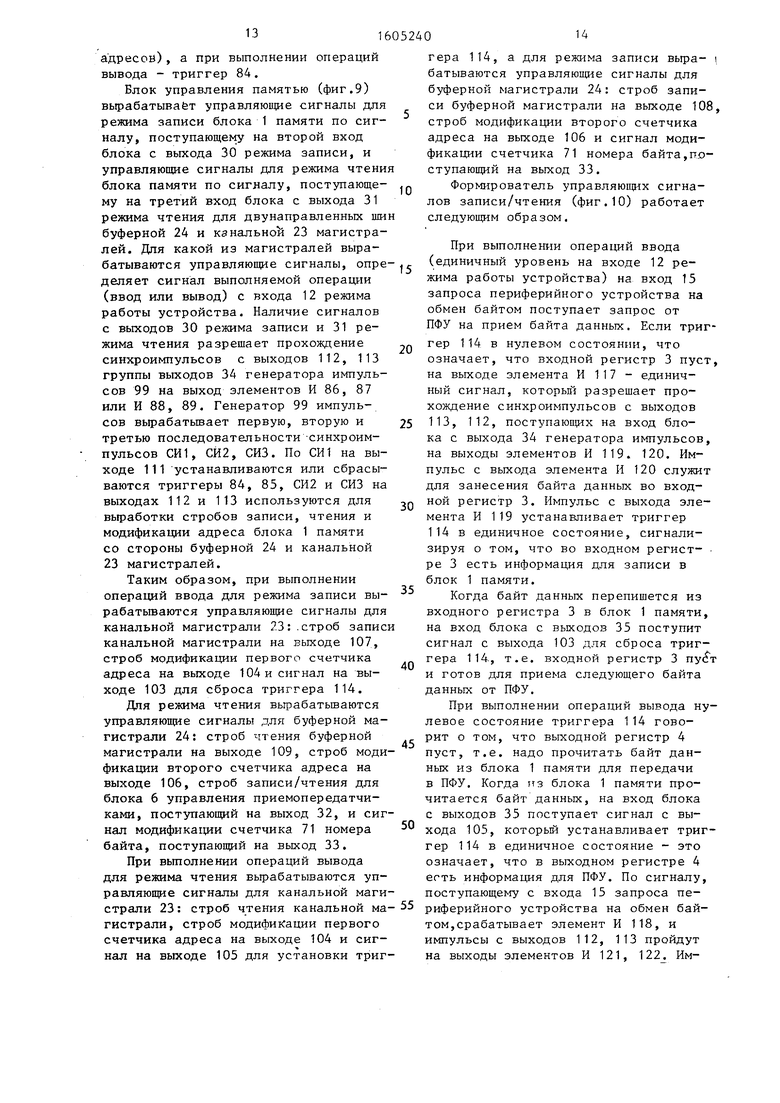

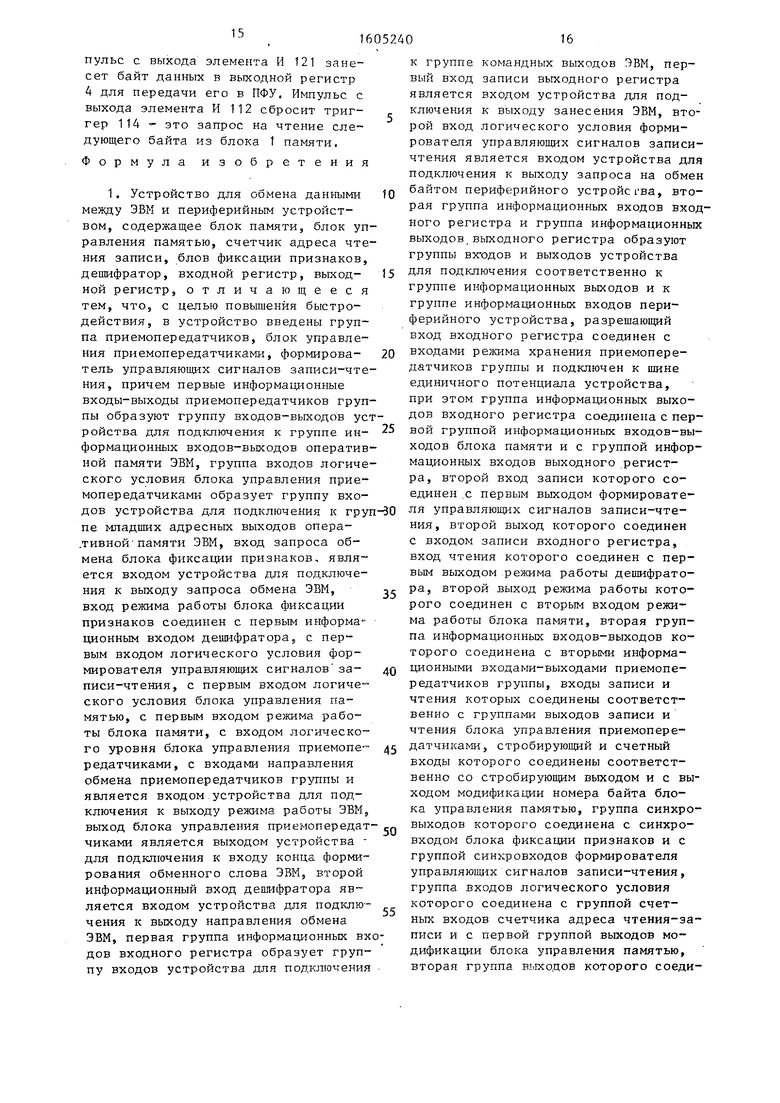

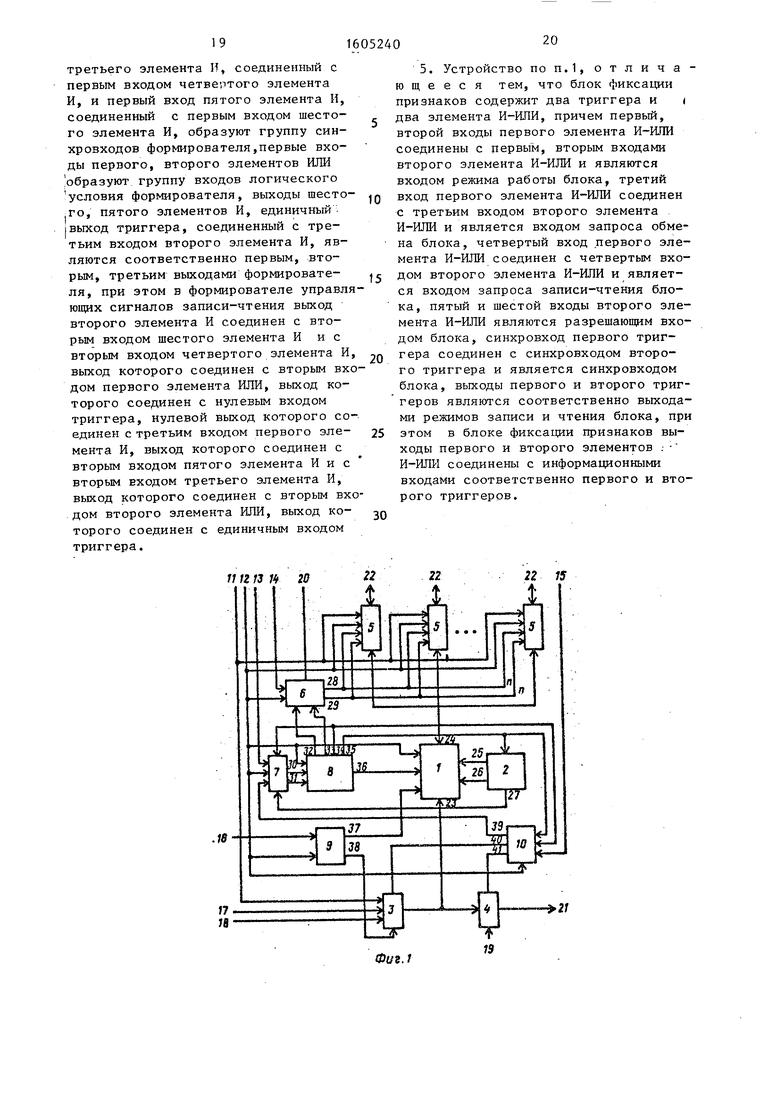

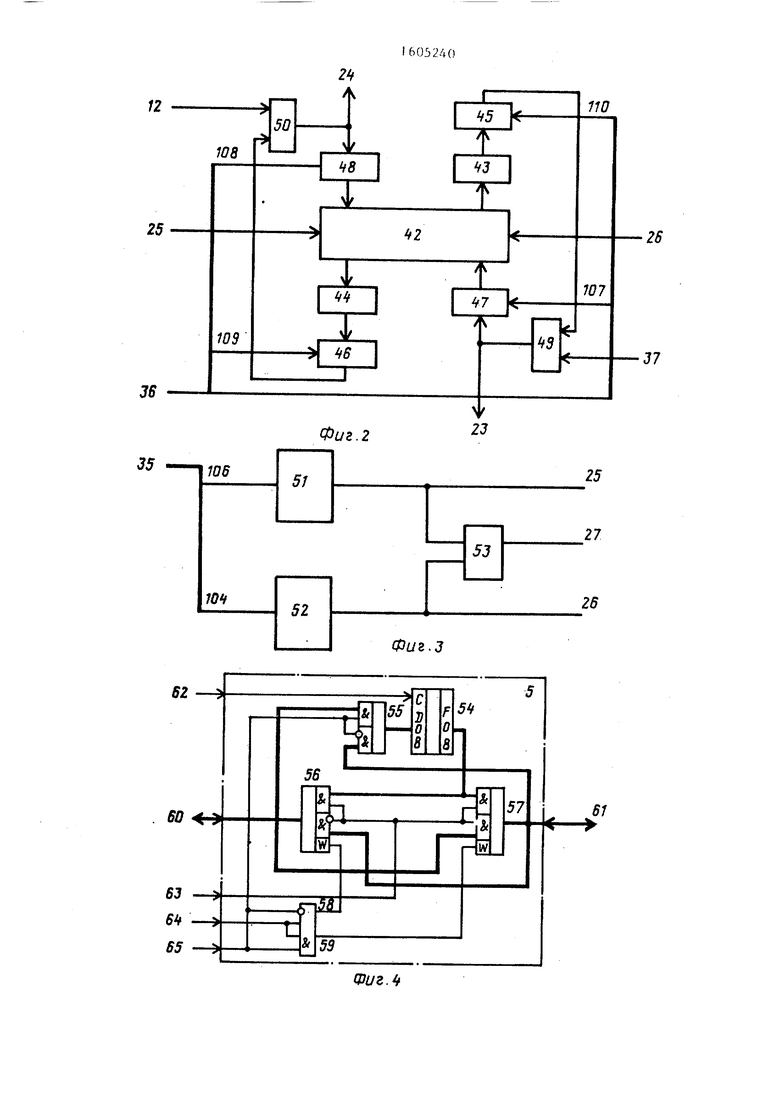

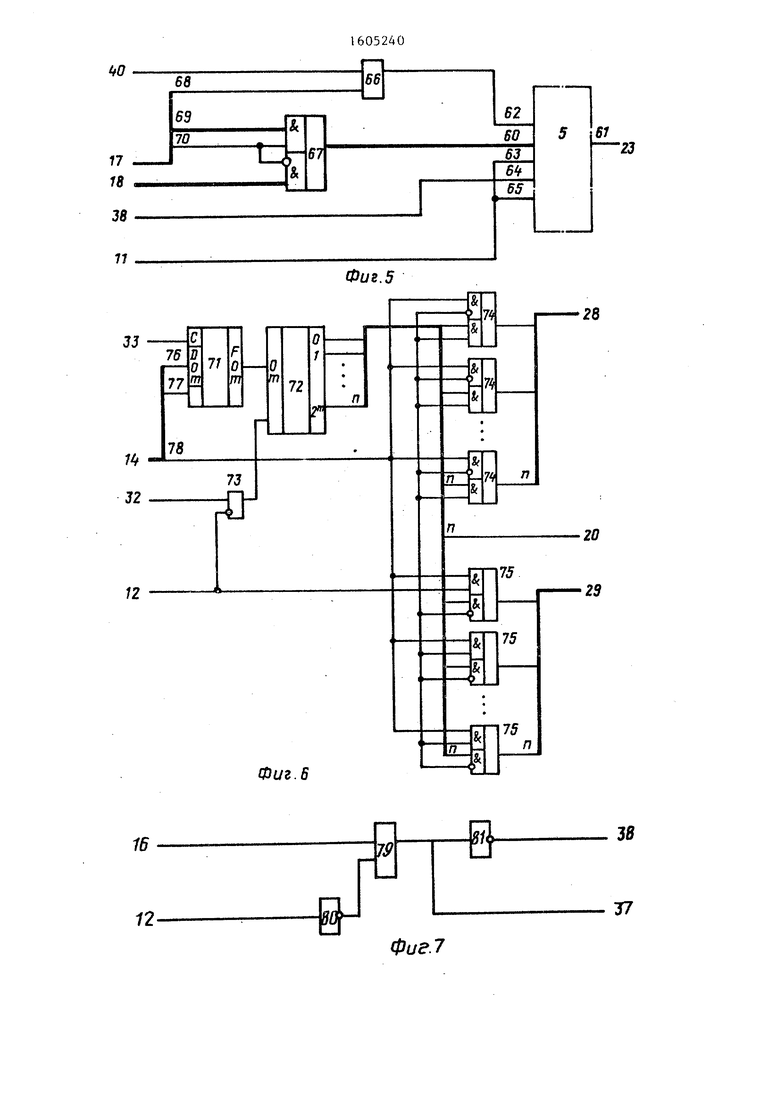

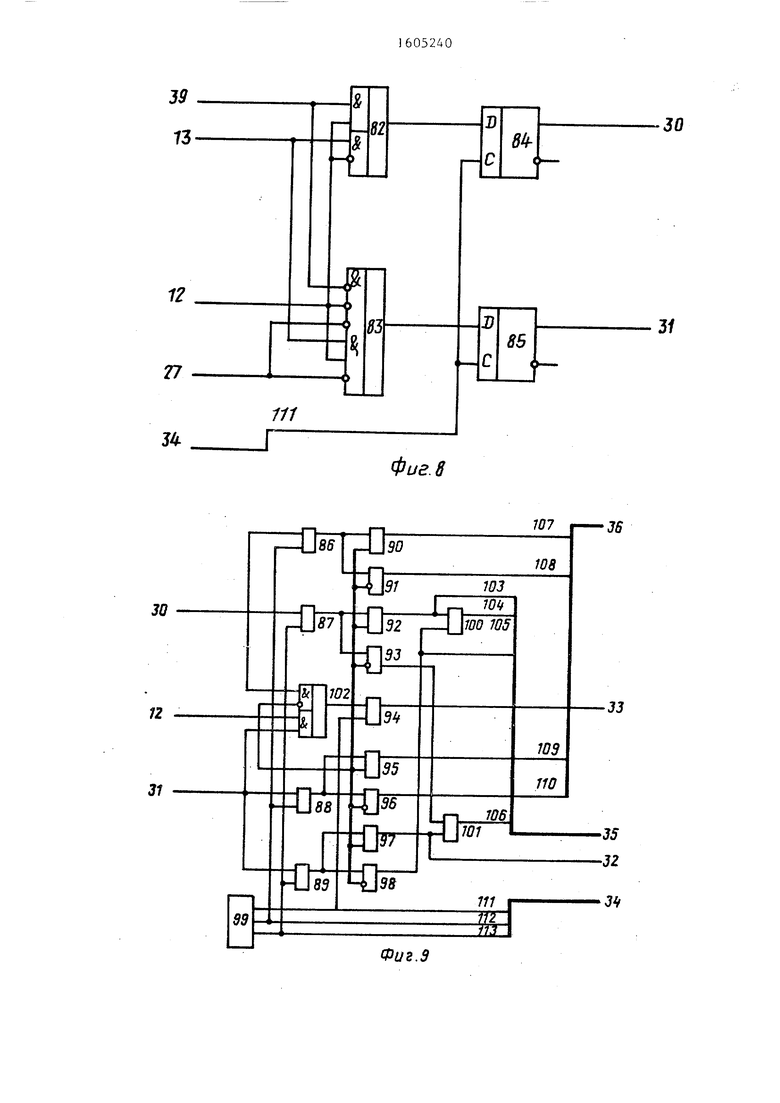

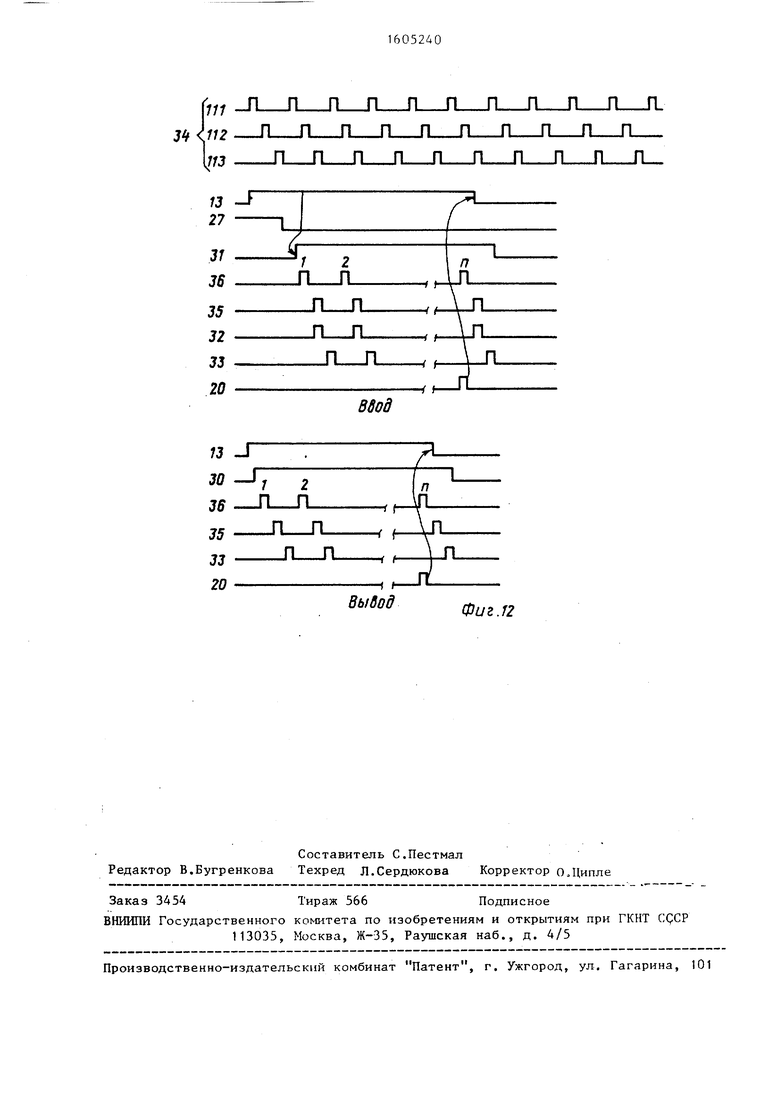

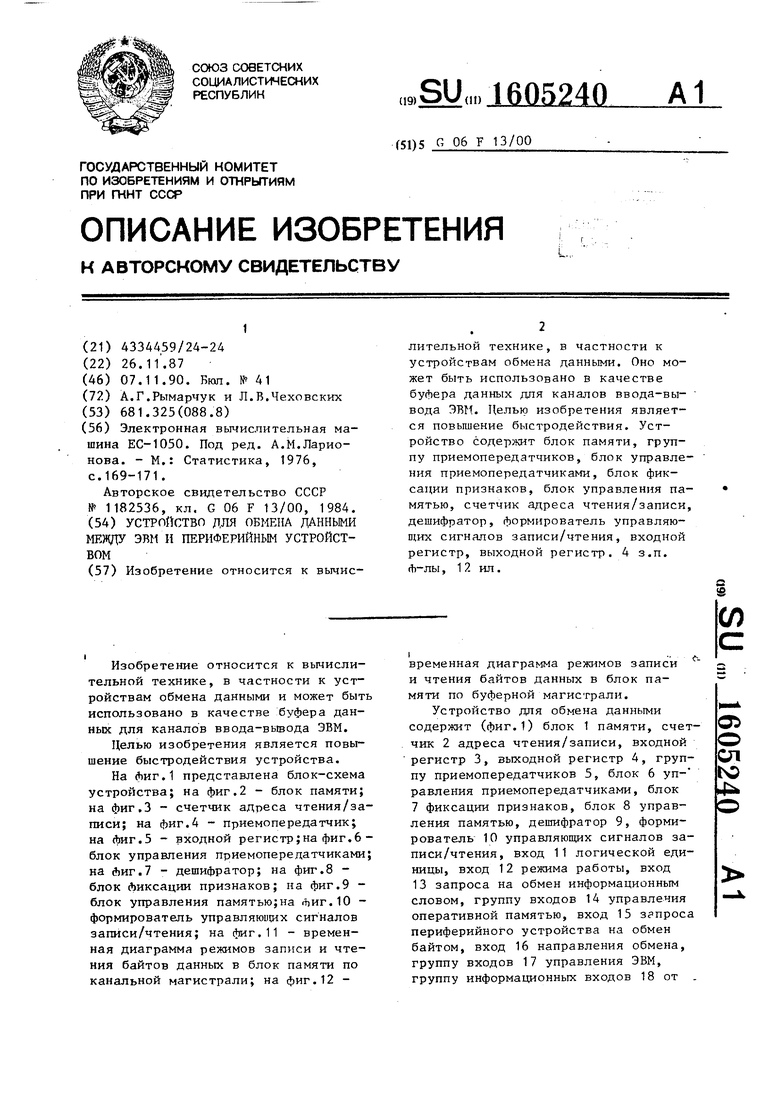

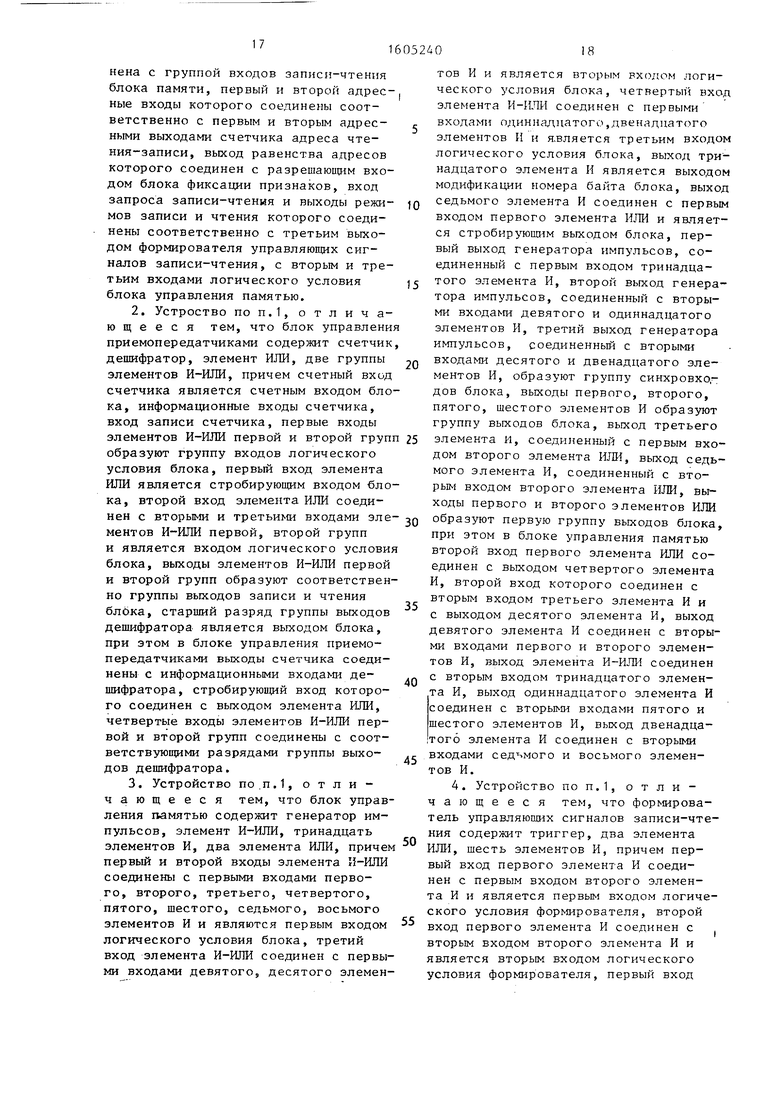

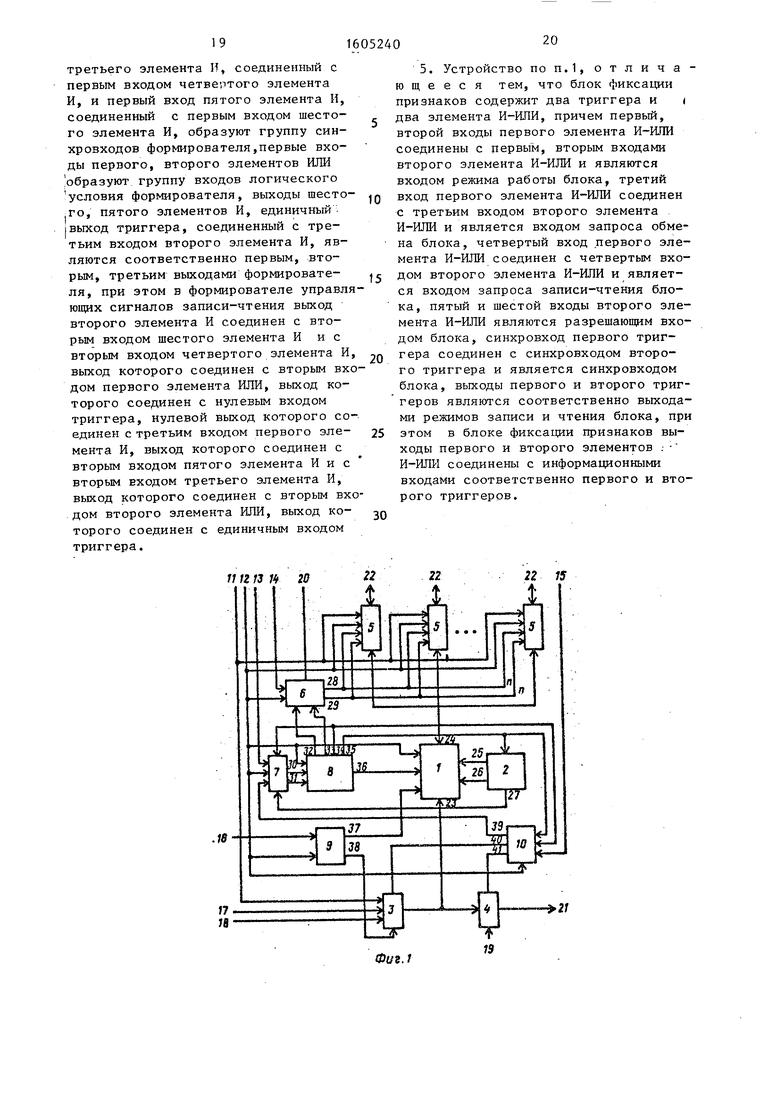

На фиг.1 представлена блок-схема устройства; на фиг.2 - блок памяти; на фиг.З - счетчик адреса чтения/записи; на фиг.4 - приемопередатчик; на фиг.5 - входной регистр;на фиг.6- блок управления приемопередатчиками; на Аиг.7 - дешифратор; на фиг.8 - блок фиксации признаков; на фиг.9 - блок управления памятью;на Фиг.10 - формирователь управляющих сигналов записи/чтения; на фиг.11 - временная диаграмма режимов записи и чтения байтов данных в блок памяти по канальной магистрали; на фиг.12 - .

временная диаграмма режимов записи

и чтения байтов данных в блок памяти по буферной магистрали.

Устройство для обмена данными содержит (фиг.1) блок 1 памяти, счетчик 2 адреса чтения/записи, входной регистр 3, выходной регистр 4, группу приемопередатчиков 5, блок 6 уп- равления приемопередатчиками, блок 7 фиксации признаков, блок 8 управления памятью, дешифратор 9, формирователь 10 управляющих сигналов записи/чтения, вход 11 логической единицы, вход 12 режима работы, вход 13 запроса на обмен информационным словом, группу входов 14 управления оперативной памятью, вход 15 запроса периферийного устройства на обмен байтом, вход 16 направления обмена, группу входов 17 управления ЭВМ, группу информационных входов 18 от .

периферийного устройства, вход 19 занесения, выход 20 конца формирования обменного слова, группу информационных выходов 21 в периферийное устройство, информационные входы-выходы 22, двунаправленные шины канальной магистрали 23, двунаправленные шины буферной магистрали 24.

На фиг.1 обозначены выходы 25 - 41 блоков устройства.

Блок 1 памяти (фиг.2) предназначен для временного хранения байтов данных, поступающих в него по двунаправленным шинам буферной 24 и канальной 23 магистралей. Он реализован на микросхеме К 1800 РП6 (зарубежный аналог НС 10806) и содержит матрицу 42 памяти двойного доступа, первый 43 и второй 44 усилители считывания, первый 45 и второй 46 регистры, первый 47 и второй 48 формирователи записи, первый 49 и второй 50 формирователи шин.

Счетчик 2 адреса чтения/записи (фиг.З) предназначен для адресации ячеек блока 1 памяти. Он содержит счетчики 51 и 52 адреса и элемент 53 сравнения.

Приемопередатчик 5 (фиг,4) предназначен для обеспечения двунаправленного обмена и временного хранения данных, он реализован на микросхеме К1800ВА7 (зарубежный аналог МС 10807 и содержит регистр 54, элементы И-ИЛИ 55-57, элементы И 58 и 59. На фиг,4 обозначены входы-выходы 60 и 61 , входы 62-65,

Входной регистр 3 (фиг.5) предназначен для приема и временного хранения байтов данных, поступающих от периферийных устройств, и управляющей информации для периферийных устройств, поступающей из ЭВМ, Он содержит приемопередатчик 5, элемент ИЛИ 66 и элемент И-ИЛИ 67. На фиг.5 обозначены входы 68-70 группы входов 17,

Блок 6 управления приемопередатчиками (фиг,6) предназначен для выработки сигналов записи и чтения байтов данных в/из приемопередатчиков 5. Он содержит счетчик 71, дешифратор 72, элемент ИЛИ 73, группу 74 элементов И-ИЛИ и группу 75 элементов И-ШШ, На фиг.6 обозначены входы 76-78 группы .входов 14.

Дешифратор 9 (фиг.7) предназначен для определения направления передачи

данных по двунаправленным шинам канальной магистрали 23, Он содержит элемент И 79, элементы НЕ 80 и 81.

Блок 7 фиксации признаков (фиг,8) предназначен для определения режима работы (записи или чтения) блока 1 памяти. Он содержит элементы И-ИЛИ 82 и 83, триггеры 84 и 85,

Блок 8 управления памятью (фиг,9) предназначен для выработки управля- сигналов режимов записи и чтения байтов данных в блок 1 памяти по двунаправленным шинам буферной 24 и

канальной 23 магистралям. Он содер жит элементы И 86-98, генератор 99 импульсов, элементы ИЛИ 100, 101, элемент И-ИЛИ 102. На фиг,9 обозначены выходы 103-106, группы выходов

35, выходы 107-110, группы выходов 36, выходы 111-113 группы выходов 34

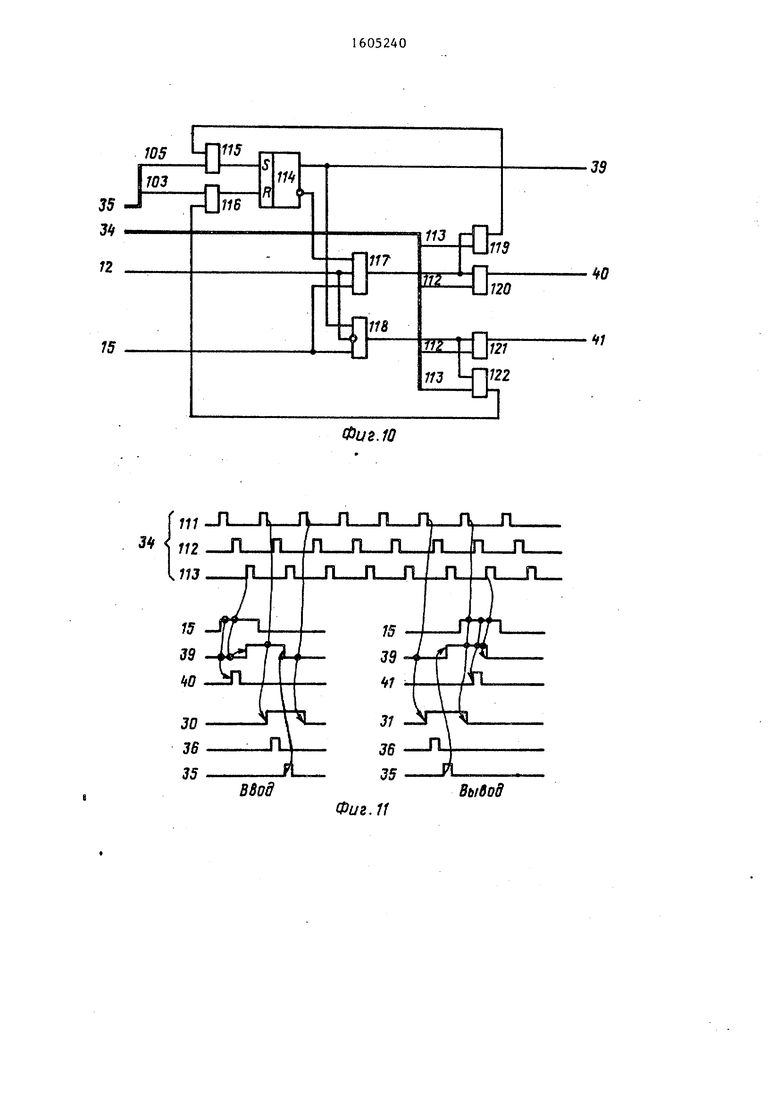

Формирователь 10 управляющих сигналов записи/чтения (фиг.10) предна- значен для выработки управляющих сиг налов занесения байтов данных во входной регистр 3 и в вькодной регистр 4, а также для выработки запроса на запись/чтение байта данных в блок 1 памяти по канальной магистрали 23. Он содержит триггер 114, элементы .ИЛИ 115 и 116, элементы И 117-122.

Устройство работает следующим образом,

Оперативная память (ОП) и периферийное устройство (ПФУ), обменивающиеся информа11;ией, используют для промежуточного хранения передаваемых данных блок 1 памяти.

Периферийное устройство обменивается данными с блоком 1 памяти через входной регистр 3 и выходной регистр

4по двунаправле.нным шинам канальной магистрали 23, используя первые адресные выходы 26 счетчика 2 адреса чтения/записи.

Оперативная память обменивается данными с блоком 1 памяти по входам- выходам 22 через приемопередатчик

5по двунаправленным шинам буферной магистрали 24, используя вторые адресные выходы 25 счетчика 2 адреса чтения/записи.

Количество приемопередатчиков 5 выбирается в зависимости от формата обмена с ОП и для общего случая равно п (т.е. за одно обращение к ОП передаются п байтов).

5

Таким образом, и ОП и ПФУ могут обмениваться данными с блоком 1 памяти одновременно по разным адресам и шинам с разными скоростями и форматами обмена независимо друг от друга.

Направление передачи данных и режим работы двунаправленных магистралей (запись или чтение) определяет сигнал, поступающий с входа 12 режима работы устройства. При выполнении операций ввода на этом входе присутствует единичный сигнал, задающий для приемопередатчиков 5 направление передачи данных с буферной магистрали 24 на входы-выходы 22, а для блока 1 памяти, поступая на первый его вход режима работы, разре шая вьздачу информации в буферную магистраль 24, а пройдя через дешифратор 9, сигналом с выхода 37 запрещает вьщачу данных в канальную магистраль 23, делая канальную магистраль 23 входной, а буфернзпо магистраль 24 выходной для блока 1 памяти

При вьшолнении операций вывода на входе 12 режима работы устройства нулевой уровень сигнала и направление передачи данных в приемопередатчиках 5 меняется на противоположное, буферная магистраль 24 становится входной для блока 1 памяти. Канальная магистраль 23 на время передачи управляющей информации (адрес, команда) для ПФУ, поступающей по входам 17 управления от ЭВМ, является входной для блока -1 памяти. После передачи управляющей информа- 1ДИИ через входной регистр 3 и выходной регистр 4, в который она заносится сигналом с входа 19 занесения, на вход 16 поступает сигнал начала этапа передачи данных, по которому на выходе 37 вырабатывается сигнал, разрешающий вьщачу данных из блока 1 памяти в канальную магистраль 23, а на.выходе 38 формируется сигнал, запрещающий вьщачу информации в канальную магистраль 23.

ПФУ обменивается байтами данных с блоком 1 памяти следующим образом.

При выполнении операций ввода байты данных из ПФУ поступают на вход входного регистра 3 по информационным входам 18, Вместе с байтом данных от ПФУ поступает на вход 15 запроса периферийного устройства на обмен байтом сигнал на прием это052406

го байта. В ответ формирователь 10 вырабатывает на выходе 40 строб занесения байта данных во входной регистр 3 и на выходе 39 - запрос на прием байта в блок 1 памяти.

По этому запросу блок 7 фиксации признаков вырабатывает единичнь1й уровень сигнала на выходе 30 режима заtO писи. Блок 8 управления памятью для режима записи вьщает на выходы 36 записи/чтения памяти строб записи байта для канальной магистрали по адресу, поступающему с первых 26 ад15 ресных выходов счетчика 2, а на выходы 35 - сигнал, которьй модифицирует этот адрес на +1 и сбрасывает запрос на выходе 39 на прием байта в блок 1 памяти.

20 При выполнении операций вывода отсутствие сигналов на выходе 39 и на выходе 27 равенства адресов (т.е. в блоке 1-памяти есть информация) вызывает формирование единичного сиг25 нала на выходе 31 режима чтения блока 7 фиксации признаков. Блок 8 управления памятью для режима чтения вьщает на выходы 36 записи/чтения памяти строб чтения для канальной

30 магистрали 23 по адресу, поступающему с первых адресных выходов 26 счетчика 2 адреса чтения/записи, а на выходы 35 - сигнал, который модифицирует на +1 этот адрес и уста5

навливает в единичное состояние выход 39, что означает наличие информации для передачи в ПФУ.

При поступлении сигнала на выход 15 запроса периферийного устройства

0 на обмен байтом формирователь 10 вы- рабатьюает на выходе 41 строб занесения прочитанного из блока 1 памяти байта в выходной регистр 4 для передачи его в ПФУ по информационе ньш выходам 21 и устанавливает в нулевое состояние выход 39. В ответ блок 7 фиксации признаков возбуждает выход 31 режима чтения для считывания следующего байта данных из

Q блока 1 памяти (временная диаграмма фиг.11). ОП обменивается байтами данных с блоком 1 гамяти через приемопередатчики 5. При выполнении операций ввода или вывода в блок 6 уп- . равления приемопередатчиками поступают по адресным входам 14 от оперативной памяти М младших разрядов адреса данных ОП для определения номера байта, начиная с которого будут

заполняться при вводе или освобождаться при выводе приемопередатчики 5, так как адрес данных может быть не кратен формату обмена при первом обращении к ОП,

При выполне}ши операций ввода на вход 13 поступает запрос на формирование обменного слова для ОП. По этому запросу блок 7 фиксации признаков возбуждает выход 31 режима - чтения при условии отсутствия сигнала на выходе 27 равенства адресов, означающего, что блок 1 памяти не пустой.

Блок 8 управления памятью для режима чтения выдает на выходы 36 записи/чтения памяти строб чтения байта в буферную магистраль 24 по адресу, поступающему по вторым адресным выходам 25 счетчика 2 адреса чте ния/записи, на выходы 35 - строб модификации на +1 этого адреса, на выходе 32 стробирования - строб записи для блока 6 управления приемопередатчиками.

Блок 6 управления приемопередатчиками вырабатывает на выходах 28 записи один из п стробов записи байта с буферной магистрали 24 в соответствующий приемопередатчик 5 в зависимости от номера записываемого байта. На выходе 33 модификации номера байта блока 8 управления памятью вырабатывается сигнал модификации на +1 номера записьшаемого байта. Таким же образом записываются байты в остальные приемопередатчики 5. При записи последнего байта на выход 20 конца формирования обменого слова выдается сигнал сброса зпроса на обмен информационным слово говорящий о том, что обменное слово для ОП сформировано. По адресным входам 14 от оперативной памяти поступает сигнал чтения обменного слова, по которому блок 6 управления приемопередатчиками вырабатывает на выходах 29 чтения приемопередатчи- ков одновременно п стробов считьша- ния байтов на входы-выходы 22.

При вьшолнении операций вывода по адресным входам 14 от оперативной памяти поступают М младших разрядов адреса данных и сигнал приема обменного слова из ОП, по которому блок 6 управления приемопередатчиками формирует на вьжодах 28 записи одновременно п сигналов записи ин 10

15

20

нам,

25

6052408

формации с входов-выходов 22 в приемопередатчики 5, а на выходах 29 чтения - один из п стробов чтения байта из соответствующего приемопередатчика 5, в зависимости от М младших разрядов адреса данных, в буфер- , ную магистраль 24.

При поступлении на вход 13 запроса на обмен информационным словом сигнала на считывание обменного слова блок 7 фиксации признаков возбуждает выход 30 режима записи, по которому блок 8 управления памятью формирует на выходах 36 записи-чтения строб записи байта с буферной магистрали 24 в блок 1 памяти по адресу, поступающему по вторым адресным выходам 25 счетчика 2 адреса чтения/записи, на выходах 35 - сигнал модификации на +1 этого адреса, на выходе 33 модификации номера байта - сигнал модификации на +1 М младших разрядов адреса, т.е. номера считываемого байта. На выходах 29 чтения вырабатывается следующий из п стробов чтения байта из следующего приемопередатчика 5 в буферную магистраль 24 для записи в блок 1 памяти. При считывании последнего п-го байта на выходе 20 конца формирования обмен- ного слова вырабатывается сигнал сброса запроса на считывание обменного слова (временная диаграмма на фиг.12).

Блок 1 памяти (фиг.2) работает следующим образом.

При вьшолнении операций ввода присутствует сигнал на входе 12 режима работы устройства, разрешающий выдачу данных через формирователь 50 шин в двунаправленные шины буферной магистрали 24, и отсутствует сигнал на входе 37, т.е. двунаправленные 1ЛИНЫ канальной магистрали 23 являются входными, по которым байты данных записываются через формирователь 47 записи по сигналу на выходе 107, поступающему по выходам 36 записи/чтения памяти, в матрицу 42 памяти двойного доступа по адресу, заданному на первых адресных выходах 26 счетчика 2 адреса чтения/записи. Буферная магистраль 24 является выходной. Байты данных считываются из ячеек матри1да 42 памяти.двойного доступа по адресу, заданному на вторых адресных выходах 25 счетчика 2 адреса чтения/записи, поступающих на

30

35

40

45

50

55

вход блока, и через усилитель считывания А4 по сигналу цыхода 109 с выхода 36 записи/чтения памяти заносятся в рег истр 46. С выхода регистра 46 информация через формирователь 50 шин поступает в буферную магистраль 24.

При выполнении операций вывода отсутствует сигнал на входе 12 режима работы устройства, буферная магистраль 24 становится входной, по которой байты данных записываются через формирователь 48 записи по сигналу выхода 108 с выхода 36 записи/чтения памяти в ячейки матрицы 42 памяти двойного доступа по адресу, поступающему на вход блока с вторых адресных выходов 25 счетчика 2 адреса чтения/записи, и присутствует сигнал на входе 37, канальная магистраль 23 становится выходной. Информация счи- тьшается из ячеек матрицы 42 памяти двойного доступа по адресу, поступающему на вход блока с первых адресных выходов 26 счетчика 2 адреса чтения- записи и через усилитель 43 считывания заносится по сигналу выхода 110 с выхода 36 записи-чтения блока памяти в регистр 45, с выхода которого через формирователь 49 шин выдается на шину магистрали 23.

Счетчик адреса чтения/записи (фиг.З) работает следующим образом. В начальный момент времени содержимое счетчиков 51, 52 адреса равно нулю. Разрядность счетчиков такова, что при достижении переполнения они вновь адресуют нулевую ячейку блока 1 памяти. Модификация на +1 содержимого счетчиков 51, 52 производится соответственно по сигналам на входах 106, 104, поступающим на вход блока с выходов 35. Содержимое счетчиков сравнивается и отсутствие сигнала на выходе элемента 53 сравнения говорит 6 том, чт адреса не равны, т.е. в блоке 1 памяти есть информация.

Приемопередатчик (фиг.4) работает следующим образом.

Данные могут передаваться с входа выхода 61 на вход-выход 60 и наоборот через элементы И-ИЛИ 56, 57 в обход регистра 54 или через регистр 54. При наличии единичного сигнала на входе 63 данные на входы-выходы поступают с выхода регистра 54, нуле вой уровень этого сигнала разрешает

0

5

0

5

0

5

0

5

непосредственную передачу данных с одного входа-выхода на другой, минуя регистр 54. Направление передачи данных задается сигналом на входе 65. Единичный уровень этого сигнала задает направление передачи данных с входа-выхода 60 на вход-выход 61 и- в регистр 54, а нулевой уровень с входа-выхода 61 на вход-выход 60 и в регистр 54. Занесение данных в регистр 54 происходит по сигналу, поступающему на вход 63. Выдача данных на входы-выходы 60, 61 через эле менты И-ИЛИ 56 и 57. разрешается по сигналу, поступающему на вход 64. Отсутствие этого сигнала блокирует элементы И-ИЛИ 56 и 57 и их выходы находятся в высокоимпедансном состоянии, т.е. отключены от входов-выходов 60 и 61.

Входной регистр (фиг.5) работает следуюшим образом.

На разрешающий вход регистра подается единичный уровень сигнала с входа 11 логической единицы, который задает постепенное направление передачи данных для приемопередатчика 5 с входа-выхода 60 и на вход-выход 61 через регистр 54.

На вход чтения регистра подается сигнал с выхода 38 для отключения выхода регистра от двунаправленных шин канальной магистрали 23 на этапе передачи данных при выполнении операций вывода.

Во входной регистр поступают либо данные из ПФУ по информационным входам 18, либо управляющая информация для ПФУ по входам 17 (вход 69).

Управляющая информация проходит на приемопередатчик. 5 через элемент И-ИЛИ 67 при наличии сигнала по входу 70 и заносится в регистр 54 по сигналу на входе 68, поступающему по входам 17. При отсутствии сигнала по входу 70 в регистр 54 записываются байты данных от ПФУ по сигналу занесения, поступающему с выхода 40.

I .

Блок управления приемопередатчиками (фиг.6) работает следующим образом.

Для определения номера байта, начиная с которого будут заполняться при вводе или освобождаться при выводе приемопередатчики 5 при первом обращении к СП, в счетчик 71 номера байта поступает по выходам 14 от опе-

ративной памяти по входу 76 и заносится по сигналу на входе 77 М младших разрядов адреса данных.

Расшифровка содержимо1 о счетчика 71 пpoизвt)дитcя дешифратором 72, выходы которого поступают на элементы И-ИЛИ 74 и,75. Элементы И-ИЛИ 74 вырабатывают сигналы записи, а элементы И-ИЛИ 75 - сигналы чтения байтов данных для каждого из п приемопередатчиков 5.

При вьшолнении операций ввода (единичный уровень на входе 12 режима работы устройства) на выходах 1 памяти, ментов И-ИЛИ 74 вьфабатываются стро-.. Обмен данными с блоком 1 памяти

бы записи байтов в соответствии с со- :ho канальной магистрали 23 осуществляется по запросам, поступаю1цим с выхода 39. При выполнении операций

20

держимым счетчика 71 номера байта в ответ на каяодый сигнал, поступающий с выхода 32. Содержимое счетчика 71 модифицируется на +1 по сигналу с выхода 33 модификации номера байта, а на выходах элементов И-ИЛИ 75 вырабатываются одновременно п стробов чтения в ответ на сигнал по входу 78 с входов 14 от оперативной памяти.

При выполнении операций вывода по сигналу на входе 78 на выходе элементов И-ИЛИ 74 вырабатываются одновременно п сигналов записи, а на выходах элементов И-ИЛИ 75 вырабатываются последовательно п сигналов чтения после каждой модификации содержимого счетчика 71.

ввода (единичный уровень сигнала на входе 12 режима работы устройства) наличие сигнала с выхода 39 является запросом на запись данных в блок 1 памяти. По синхроимпульсам, посту25 паюшим по выходу 111 группы выходов 34 генератора импульсов, триггер 84 устанавливается в единичное состояние, так как на его информационном входе единичный уровень с

JQ выхода элемента И-ИЛИ 82. При отсутствии запроса с вькода 39 на информационном входе триггера 84 нулевой уровень и он сбросится импульсами с выхода 111.

При вьшолнении операций вывода

Дешифратор 9 (фиг.7) работает еле- отсутствие сигнала на выходе 39 яв цующим образом,

При выполнении операций вывода на входе первого элемента НЕ 80 - нулевой уровень сигнала с входа 12 режима работы устройства, который становится единичным на втором входе элемента И 79. На этапе передачи данных на первом входе элемента И 79 присут- ствует единичный сигнал с входа 16 й- на выходе И 79 вьфабатывается единичный сигнал, разрешающий выдачу информации из блока 1 памяти в двунаправленные шины канальной магистрали 23, т.е. делающий эту магистраль выходной по отношению к блоку 1 памяти.

Одновременно на выходе второго элемента НЕ 81 вырабатывается нулевой уровень сигнала, который отключает выход входного регистра- 3 от канальной магистрали 23.

В остальных случаях, т.е. при вводе и вне этапа передачи данных, на

40

45

50

ляется запросом на чтение данных из блока 1 памяти при условии наличия информации в блоке 1 памяти, т.е. при отсутствии сигнала с выхода 27 равенства адресов. В этом случае на информационном входе триггера 85 при сутствует единичный уровень с выход элемента И-ИЛИ 83 и по синхроимпуль сам на выходе 111 триггер 85 устано вится в единичное состояние. При отсутствии запроса на информационно входе триггера 85 нулевой уровень и по синхроимпульсам на выходе 111 он установится в нулевое состояние.

Обмен данными с блоком 1 памяти по буферной магистрали 24 осуществляется по запросам, поступающим с входа 13„ По этому запросу при выпол 55 нении операций ввода устанавливается в единичное состояние триггер 85, если блок 1 памяти не пуст (отсутст вие сигнала на выходе 27 равенства

выходе элемента И 79 нулевой уровень, делаюа ий двунаправленные шины канальной магистрали 23 входными по отношению к блоку 1 памяти, и на выходе второго элемента НЕ 81 - еди ничный уровень, разрешающий выдачу информации с выхода входного регистра 3 в канальную магистраль 23.

Блок 7 фиксации признаков (фиг.8) работает следующимобразом.

Триггеры 84 и 85 устанавливаются в единичное состояние при наличии запроса на обмен данными с блоком

ввода (единичный уровень сигнала на входе 12 режима работы устройства) наличие сигнала с выхода 39 является запросом на запись данных в блок 1 памяти. По синхроимпульсам, поступаюшим по выходу 111 группы выходов 34 генератора импульсов, триггер 84 устанавливается в единичное состояние, так как на его информационном входе единичный уровень с

выхода элемента И-ИЛИ 82. При отсутствии запроса с вькода 39 на информационном входе триггера 84 нулевой уровень и он сбросится импульсами с выхода 111.

При вьшолнении операций вывода

ляется запросом на чтение данных из блока 1 памяти при условии наличия информации в блоке 1 памяти, т.е. при отсутствии сигнала с выхода 27 равенства адресов. В этом случае на информационном входе триггера 85 присутствует единичный уровень с выхода элемента И-ИЛИ 83 и по синхроимпульсам на выходе 111 триггер 85 установится в единичное состояние. При отсутствии запроса на информационном входе триггера 85 нулевой уровень и по синхроимпульсам на выходе 111 он установится в нулевое состояние.

Обмен данными с блоком 1 памяти по буферной магистрали 24 осуществляется по запросам, поступающим с входа 13„ По этому запросу при выпол- нении операций ввода устанавливается в единичное состояние триггер 85, если блок 1 памяти не пуст (отсутствие сигнала на выходе 27 равенства

адресов), а при выполнении операций вывода - триггер 84.

Блок управления памятью (фиг.9) вьфабатываёт управляющие сигналы для режима записи блока 1 памяти по сигналу, поступающему на второй вход блока с выхода 30 режима записи, и управляющие сигналы для режима чтени блока памяти по сигналу, поступающему на третий вход блока с выхода 31 режима чтения для двунаправленных ши буферной 24 и канальной 23 магистралей. Для какой из магистралей вырабатываются управляющие сигналы, опре деляет сигнал выполняемой операции (ввод или вывод) с входа 12 режима работы устройства. Наличие сигналов с выходов 30 режима записи и 31 режима чтения разрешает прохождение синхроимпульсов с выходов 112, 113 группы выходов 34 генератора импульсов 99 на выход элементов И 86, 87 или И 88, 89. Генератор 99 импульсов вьфабатьшает первую, вторую и третью последовательности -синхроимпульсов СИ1, СЙ2, СИЗ. По СИ1 на выходе 111 устанавливаются или сбрасываются триггеры 84, 85, СИ2 и СИЗ на выходах 112 и 113 используются для выработки стробов записи, чтения и модификации адреса блока 1 памяти со стороны буферной 24 и канальной 23 магистралей.

Таким образом, при выполнении операций ввода для режима записи вы- рабатьгоаются управляющие сигналы для канальной магистрали 23:.строб запис канальной магистрали на выходе 107, строб модификации первого счетчика адреса на выходе 104 и сигнал на выходе 103 для сброса триггера 114.

Для режима чтения вырабатьшаются управляющие сигналы для буферной магистрали 24: строб чтения буферной магистрали на выходе 109, строб модификации второго счетчика адреса на выходе 106, строб записи/чтения для блока 6 управления приемопередатчиками, поступающий на выход 32, и сиг

нал модификагщи счетчика 71 номера байта, поступающий на вькод 33.

При вьтолнении операций вывода для режима чтения вырабатываются управляющие сигналы для канальной маги50

При выполнении операций вывода нулевое состояние триггера 114 говорит о том, что выходной регистр 4 пуст, т.е. надо прочитать байт данных из блока 1 памяти для передачи в ПФУ. Когда из блока 1 памяти про- читается байт данных, на вход блока с выходов 35 поступает сигнал с выхода 105, которьш устанавливает триггер 114 в единичное состояние - это означает, что в выходном регистре 4 егть информация для ПФУ. По сигналу, поступающему с входа 15 запроса пестрали 23: строб чтения канальной ма- 55 риферийного устройства на обмен бай0

0

5

г

0

5

0

5

0

гера 114, а для режима записи вьфа- i батываются управляющие сигналы для буферной магистрали 24: строб записи буферной магистрали на выходе 108, строб модификации второго счетчика адреса на выходе 106 и сигнал модификации счетчика 71 номера байта,поступающий на выход 33.

Формирователь управляющих сигналов записи/чтения (фиг.10) работает следующим образом.

При выполнении операций ввода (единичный уровень на входе 12 режима работы устройства) на вход 15 запроса периферийного устройства на обмен байтом поступает запрос от ПФУ на прием байта данных. Если триггер 114 в нулевом состоянии, что означает, что входной регистр 3 пуст, на выходе элемента И 117 - единичный сигнал, которьй разрешает прохождение синхроимпульсов с выходов 113, 112, поступающих на вход блока с выхода 34 генератора импульсов, на выходы элементов И 119. 120. Импульс с выхода элемента И 120 служит для занесения байта данных во входной регистр 3. Импульс с выхода элемента И 119 устанавливает триггер 114 в единичное состояние, сигнализируя о том, что во входном регист- ре 3 есть информация для записи в блок 1 памяти.

Когда байт данных перепишется из входного регистра 3 в блок 1 памяти, на вход блока с выходов 35 поступит сигнал с выхода 103 для сброса триггера 114, т.е. входной регистр 3 и готов для приема следующего байта данных от ПФУ.

При выполнении операций вывода нулевое состояние триггера 114 говорит о том, что выходной регистр 4 пуст, т.е. надо прочитать байт данных из блока 1 памяти для передачи в ПФУ. Когда из блока 1 памяти про- читается байт данных, на вход блока с выходов 35 поступает сигнал с выхода 105, которьш устанавливает триггер 114 в единичное состояние - это означает, что в выходном регистре 4 егть информация для ПФУ. По сигналу, поступающему с входа 15 запроса пе

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

Изобретение относится к вычислительной технике, в частности к устройствам обмена данными. Оно может быть использовано в качестве буфера данных для каналов ввода-вывода ЭВМ. Целью изобретения является повышение быстродействия. Устройство содержит блок памяти, группу приемопередатчиков, блок управления приемопередатчиками, блок фиксации признаков, блок управления памятью, счетчик адреса чтения/записи, дешифратор, формирователь управляющих сигналов записи/чтения, входной регистр, выходной регистр. 4 з.п. ф-лы, 12 ил.

гистрали, строб модификации первого счетчика адреса на выходе 104 и сигнал на выходе 105 для установки тригтом,срабатывает элемент И 118, и импульсы с выходов 112, 113 пройдут на выходы элементов И 121, 122. Импульс с выхода элемента И 121 занесет байт данных в выходной регистр 4 для передачи его в ПФУ, Импульс с выхода элемента И 112 сбросит триггер 114 - это запрос на чтение следующего байта из блока 1 памяти.

Формула изобретения

к группе командных выходов ЭВМ, первый вход записи выходного регистра является входом устройства для подключения к выходу занесения ЭВМ, второй вход логического условия формирователя управляюшлх сигналов записи- чтения является входом устройства для подключения к выходу запроса на обмен байтом периферийного устройства, вторая группа информационных входов входного регистра и группа информационных выходов,выходного регистра образуют группы вх-одов и выходов устройства для подключения соответственно к группе информационных выходов и к группе информационных входов периферийного устройства, разрешающий вход входного регистра соединен с входами режима хранения приемопередатчиков группы и подключен к шине единичного потенциала устройства, при этом группа информационных выходов входного регистра соединена с первой группой информационных входов-выходов блока памяти и с группой информационных входов выходного регистра, второй вход записи которого соединен .с первым выходом формирователя управляющих сигналов записи-чтения, второй выход которого соединен с входом записи входного регистра, вход чтения которого соединен с первым выходом режима работы дешифратора, второй выход режима работы которого соединен с вторым входом режима работы блока памяти, вторая группа информационных входов-выходов которого соединена с вторыми информационными входами-выходами приемопередатчиков группы, входы записи и чтения которых соединены соответственно с группами выходов записи и чтения блока управления приемопередатчиками, стробирующий и счетный входы которого соединены соответственно со стробирующим выходом и с выходом модификации номера байта блока управления памятью, группа синхро- выходов которого соединена с синхро- входом блока фиксации признаков и с группой синхровходов формирователя управляюших сигналов записи-чтения, группа входов логического условия которого соединена с группой счетных входов счетчика адреса чтения-записи и с первой группой выходов модификации блока управления памятью, вторая группа выходов которого соединена с группой входов записи-чтения блока памяти, первый и второй адресные входы которого соединены соответственно с первым и вторым адресными выходами счетчика адреса чтения-записи, выход равенства адресов которого соединен с разрешаюищм входом блока фиксации признаков, вход запроса записи-чтения и выходы режи- мов записи и чтения которого соединены соответственно с третьим выходом формирователя управляющих сигналов записи-чтения, с вторым и третьим входами логического условия блока управления памятью.

и является входом логического услови блока, выходы элементов И-ИЛИ первой и второй групп образуют соответственно группы выходов записи и чтения блока, старший разряд группы выходов дешифратора является выходом блока, при этом в блоке управления приемопередатчиками выходы счетчика соединены с информационными вxoдa ш дешифратора, стробирующий вход которого соединен с выходом элемента ИЛИ, четвертые входы элементов И-ИЛИ первой и второй групп соединены с соответствующими разрядами группы выходов дешифратора.

вход элемента И-ИЛИ соединен с первыми входами девятого, десятого элемен

5

п 5 п

0

тов и и является вторым входом логического условия блока, четвертый вход элемента И-ЯЛИ соединен с первыми входами одиннадцатого,двенадцатого элементов И и является третьим входом логического условия блока, выход тринадцатого элемента И является выходом модификации номера байта блока, выход седьмого элемента И соединен с первым входом первого элемента ИЛИ и яапяет- ся стробирующим выходом блока, первый выход генератора импульсов, соединенный с первым входом тринадцатого элемента И, второй выход генератора импульсов, соединенный с вторыми входами девятого и одиннадцатого элементов И, третий выход генератора импульсов, соединенный с вторыми входами десятого и двенадцатого элементов И, образуют группу синхровхо- дов блока, выходы первого, второго, пятого, шестого элементов И образуют группу выходов блока, выход третьего элемента и, соединенный с первым входом второго элемента ИЛИ, выход седьмого элемента И, соединенный с вторым входом второго элемента ИЛИ, выходы первого и второго элементов ИЛИ образуют первую группу выходов блока, при этом в блоке управления памятью второй вход первого элемента ИЛИ соединен с выходом четвертого элемента И, второй вход которого соединен с вторым входом третьего элемента И и с выходом десятого элемента И, выход девятого элемента И соединен с вторыми входами первого и второго элементов И, выход элемента И-ИЛР1 соединен с вторым входом тринадцатого элемента И, выход одиннадцатого элемента И соединен с вторыми входами пятого и шестого элементов И, выход двенадцатого элемента И соединен с вторыми входами седьмого и восьмого элементов И.

третьего элемента И, соединенный с первым входом четвеу1того элемента И, и первый вход пятого элемента И, соединенный с первым входом шестого элемента И, образуют группу син- хровходов формирователя,первые входы первого, второго элементов ИЛИ образуют группу входов логического условия формирователя, выходы шестого, пятого элементов И, единичный Iвыход триггера, соединенный с третьим входом второго элемента И, являются соответственно первым, вторым, третьим выходами формирователя, при этом в формирователе управляющих сигналов записи-чтения выход второго элемента И соединен с вторым входом шестого элемента И и с вторым входом четвертого элемента И выход которого соединен с вторым вхдом первого элемента ИЛИ, выход которого соединен с нулевым входом триггера, нулевой выход которого соединен с третьим входом первого элемента И, выход которого соединен с вторьм входом пятого элемента И и с вторым входом третьего элемента И, выход которого соединен с вторым вхдом второго элемента ИЛИ, выход которого соединен с единичным входом триггера.

5

0

5

5, Устройство ПОП.1, отличающееся тем, что блок фиксации признаков содержит два триггера и два элемента И-ИЛИ, причем первый, второй входы первого элемента И-ШШ соединены с первым, вторым входами второго элемента И-ИЛИ и являются входом режима работы блока, третий вход первого элемента И-ИЛИ соединен с третьим входом второго элемента И-ИЛИ и является входом запроса обмена блока, четвертый вход первого элемента И-ИЛИ соединен с четвертым входом второго элемента И-ИЛИ и является входом запроса записи-чтения блока, пятый и шестой входы второго элемента И-ИЛИ являются разрешаю1щм входом блока, синхровход первого триггера соединен с синхровходом второго триггера и является синхровходом блока, выходы первого и второго триг- геров являются соответственно выходами режимов записи и чтения блока, при этом в блоке фиксации признаков выходы первого и второго элементов . И-ИЛИ соединены с информационными входами соответственно первого и второго триггеров.

25

26

Щиг.

Фие.7

39 ТЗ

12

31

JO

Фиг. 8

107

36

33

7W

-35 -32

J

Фиг.9

35 J«

72

75

Физ. 10

J

W

f1

Выбод

rj -F 27

Лn

лп

лn

Вь/вод

Лru.

BSod

Фиг.гг

| РЕЛЕ | 1924 |

|

SU1050A1 |

| Под ред | |||

| А.М.Ларионова | |||

| - М.: Статистика, 1976, с.169-171 | |||

| Авторское свидетельство СССР № 1182536, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1987-11-26—Подача