элемента ИЛИ, выход которого через последовательно соединенные шестой элемент И II второй элемент ИЛИ, к другому вход} которого подключен выход первого элемента Р через седьмой элемент И, подключен к одному из входов двух последовательно соединенных триггеров, к другому входу первого из которых подключены выходы восьмого и девятого элементов И через третий элемент ИЛИ, а другой выход второго триггера непосредственно и через третий триггер подключен к входам десятого элемента И, выход которого через счетчик подключен к входу второго дешифратора, первый выход которого подключен к одному из входов третьего элемента И. Второй выход второго дешифратора подключен к одному из входов пятого, седьмого, восьмого и девятого элементов И непосредственно и через второй инвертор к соответствующему входу четвертого элемента И. Кроме того, выход первого счетчика подключен к одному из входов регистра сдвига и к соответствующему входу первого счетчика и через третий 1нвертор к одному из входов третьего элемента И. Другой выход первого дешифратора через четвертый инвертор подключен к одному из входов одиннадцатого элемента И, выход которого через последовательно соединенные иятый инвертор, четвертый триггер и второй счетчик подключен к входу третьего дешифратора, выход которого подключен к перному входу двенадцатого элемента И, к двум другим входам которого подключены соответственно третий выход второго дешифратора и соответствуюш,ий выход первого счетчика, а выход двенадцатого элемента И подключен к соответствуюшему входу четвертого и пятого триггеров, к друТОЩ входу которого подключен выход четвертого инвертора, а выход пятого триггера подключен к соответствуюш ему одиннадцатого элемента PI, причем управляюндий вход четвертого и пятого триггеров соединен с выходом десятого элемента И, управляющий вход второго счетчика - с четвертым выходом второго дешифратора.

Блок синхронизации речевых каналов. содержит первый и второй запоминающий блоки, к выходам которых подключены соответствующие блоки записи - считывания, к .управляющим входам которым подключены соответствующие выходы формирователей временных .интервалов и блок вынесения решения, состоящий из счетчика, выход которого подключен к входу дешифратора, выходы которого подключены к соответствующим входам первого и второго триггера, к другим входам которых подключены соответствующие выходы выходного триггера, а выходы этих триггеров подключены к соответствующим входам счетчика и двух элементов И, выходы которых соединены с соответствующими входами выходного триггера.

Блок синхронизации информации сигнализации содержит две цепи, каждая из которых состоит из последовательно соединенных приемного блока, матрицы перекодирования и передающего блока, к управляющим входам которых подключены выходы блока управления.

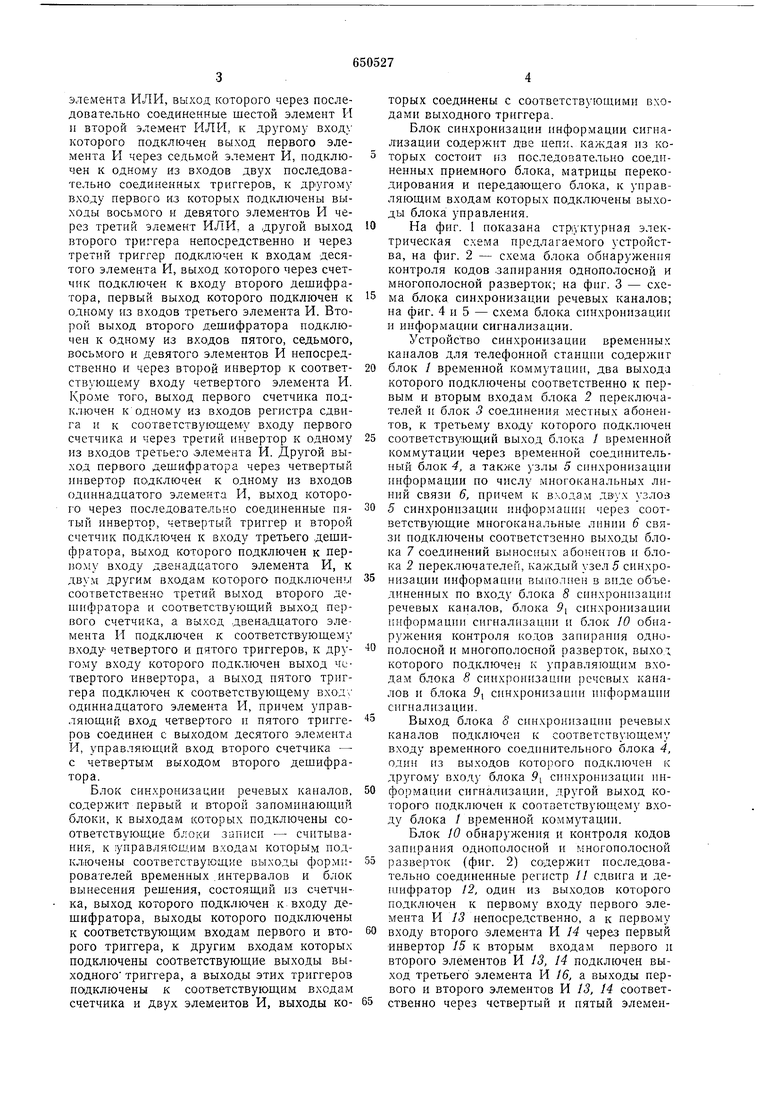

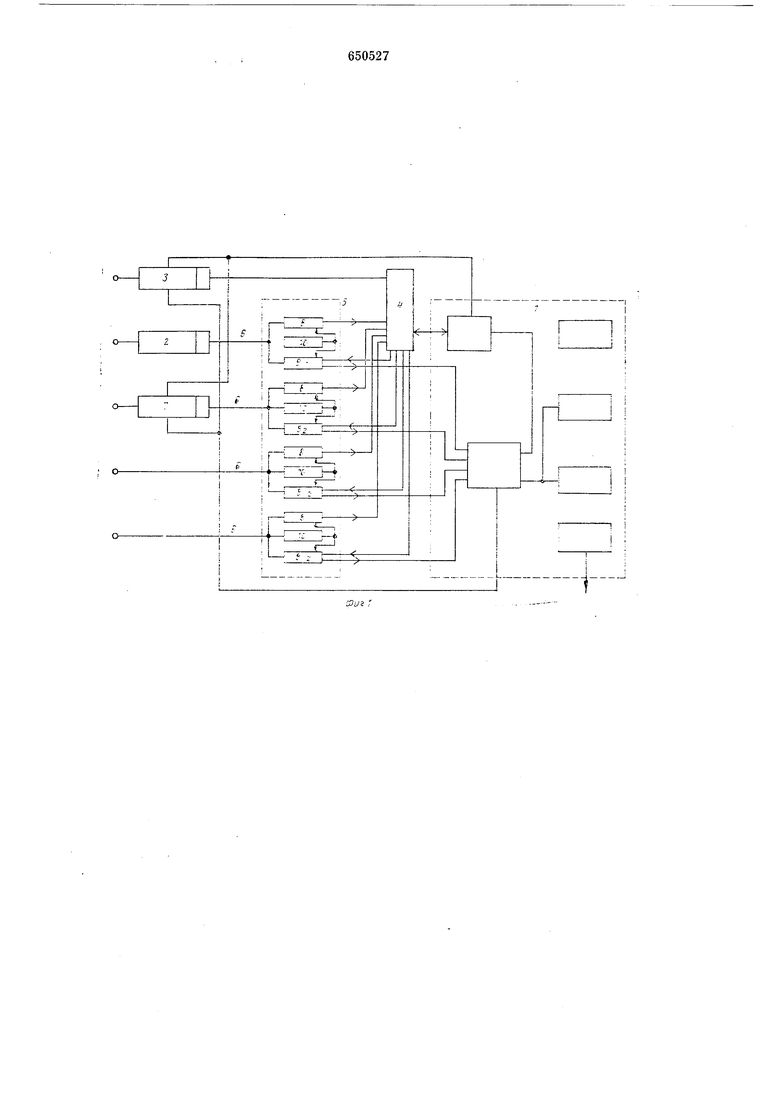

На фиг. 1 показана стр|уктурная электрическая с.чема предлагаемого устройства, на фиг. 2 - схема блока обнаружен 1я контроля кодов .запирания однополосной и многополосной разверток; на фиг. 3 - схема блока синхронизации речевых каналов; на фиг. 4 и 5 - схе.ма блока синхронизации и информации сигнализации.

Устройство синхронизации временны. каналов для телефонной станции содержит блок / временной коммутаци 1, два выхода которого подключены соответственно к первым и вторым входам блока 2 переключателей и блок 3 соединения местных абонентов, к третьему входу которого подключен соответствующий выход блока 1 временной коммутации через временной соединительный блок 4, а также узлы 5 синхронизации информации по числу .многоканальных линий связи 6, причем к входам узлоз 5 синхронизации информации через соответствующие многоканальные линии 6 связи подключены соответстзенно вы.ходы блока 7 соединений выносных абонентов и блока 2 переключателей, каждый узел 5 синхронизации информации выполнен в виде объединенных по входу блока 8 синхронизации речевых каналов, блока 9 синхронизации информации сигнализации и блок W обнаружения контроля кодов запираиия однополосной и многополосной разверток, выход которого подключен к управляющим входам блока 8 сиихронизац 1и речевых каналов и блока 9 синхронизации информации сигнализации.

Выход блока 8 синхронизации речевых каналов подключен к соответствующему входу временного соединнтельного блока 4, один из выходов которого подключен к другому входу блока 9i синхронизации информации сигнализации, другой выход которого подключен к соответствующему входу блока / временной коммутации.

Блок 10 обнаружения и контроля кодов запирания однополосной и многополосной разверток (фиг. 2) содержит последовательно соединенные регистр // сдвига и декшфратор 12, один из выходов которого подключен к первому входу первого элемента И 13 непосредственно, а к первому входу второго элемента И 14 через первый инвертор 15 к вторым входам первого и второго элементов И 13, 14 подключен выход третьего элемента И 16, а выходы первого и второго элементов И 13, 14 соответственно через четвертый и иятый элементы И П, 8 подключены к входам первого элемента ИЛИ 19, выход которого через последовательно соединенные шестой элемент И 20 и второй элемент ИЛИ 21, к другому входу которого подключен выход первого элемента И 13, через седьмой элемент И 22 подключен к одному из входов двух последовательно соединенных триггеров 23, 24, к другому входу первого из которых подключены выходы восьмого и девятого элементов И 25, 26 через третий элемент ИЛИ 27.

Другой выход второго триггера 24 непосредственно через последовательно соединенные третий триггер 28 подключен к входам десятого элемента И 29, выход которого через первый счетчик 30 подключен к входу второго дешифратора 31, первый выход которого иодключен к одному из входов третьего элемента И 16, а второй выход второго дешифратора 31 иодключен к одному из входов пятого (18), седьмого (22), восьмого (25) и девятого (26) элементов И неиосредствеино н через второй инвертор 32 к соответствующему входу четвертого элемента И 17.

Кроме того, выход первого счетчика 30 подключен к одному из входов регистра // сдвига, к соответствующему входу первого счетчика 30 и через третий инвертор 33 к одному из входов третьего элемента И 16. Другой выход иервого дешифратора 12 через четвертый инвертор 34 подключен к одному из входов одиннадцатого элемента И 35, выход которого через последовательно соединенные пятый инвертор 36, четвертый триггер 37, к другому входу которого иодключен выход двенадцатого элемента И 38, и второй счетчик 39 подключеи к входу третьего дешифратора 40, выход которого подключен к иервому входу двенадцатого элемента И 38, к двум другим входам которого подключенЕ) соответственно третпй выход второго дешифратора 31 и соответствующий ВЫХО.Д первого счетчика 30. Выход двенадцатого элемента И 38 подключеи к соответствующему входу четвертого и пятого триггеров 37, 41, к другому входу которого подключен выход четвертого инвертора 34, а выход пятого триггера 41 подключен к соответствующему входу один);адцатого элемента И 35, причем уиравляющий вход четвертого и пятого триггеров 37, 41 соединен с выходом десятого элемента И 29, а управля О(Щий вход второго счетчика 39 - с четвертым выходом второго дещифратора 31.

Блок 8 синхронизации речевых каналоз (фиг. 3) содержит иервый и второй запоминающий блоки 42, 43, к входам которых подключены соответствующ.ие блоки 44, 45 записи - считывания, к уиравляющим входам которых подключены соответствующие формирователи 46, 47 временных интервалов и блок 48 вынесения рещения, состоящий из

счетчика 49, выход которого подключен к входу дешифратора 5Q, выходы которого иодключеиы к соответствующим входам иервого и второго триггеров 51, 52, к другим входам которых подключены соответствующие выходы вь ходного триггера 55. Выходы триггеров 51, 52 подключены к соответствующим входам счетчика 49 и двух элементов И 54, 55, выходы которых соедцйены с соответствующими входами выходного триггера 55.

Блок 9 синхоонизации информации сигнализации содер;«ит две цепи, каждая из которых состоит из последовательно соединенных приемного блока 56, матрицы 57 иерекодирования и передаюшего блоки 58, к .управляющим входам которых подключены выходы блока 55 /управления. . Предложенное устройство работает следующим образом.

Блок 3 соединения позволяет установить, наирпмер, шестьдесят коммуникаций между 512 пocтa iи абонентов, с которыми он соединен. Блок 2 переключателей ириспосабливает сш-нзлизацию конечных цифровых станций к сигнализации, исиользуелюй в межкаскадных иепях. Блок 1 временной коммутации предназначен для обработки тестогз новых вызовов или тестов

сгстояиия постов абонентов, когда блок сосдиисиия или блок переключателей регисгрпрует HOBbifi вызов или отбой. Эта информация иередается по «семафорному каналу в случае нэл)1чия выносного обор дования.

Информация, поступающая с многоканальной лииии 60. использующей связь кодированной имиульскоЛ модуляцией, поступает последовательно в рег)1стр //, Дешифратор 12 позволяет распознать кодовые комбпиации. Сигнал, проходящий с дешифратора 12. контполи;5уется с помощью элемеита И 16 н инвертора 15. Элемент И 14 выдает сигнал ,тизации

развертки, когда Зчсд заии;зания распознан, а элемент I-I 13 выдает сигнал, когда этот код синхронизлцля не распознан.

Триггеры 23, 2, 23 позволяют кодировать шесть возможных состояни)1 устройства.

Узел иа двух триггерах 37 и 41 обеспечивает кодирование трех возможных состояний.

Предположим, то в начальный момент

времени все С1и-1хсо -изировано, тр1 ггеры 37, 41 находятся н состоянии «1,0, На многоиолосной разБе: тке имеют место два случая: триггер 4 переходит в положение «1, триггер 37 остается в положении

« выход элемента И 3S находится на «О, что после прохо ; ;ден 1я ;1нвертора 36 подает на вход :нформации триггера 37 единицу.

Потеря запирания многополосной развертки приводит к тому, что система переходит в состояние «1,1 из состояния «1,0. Если система находится в состоянии «1,1, мопут иметь место два случая на многополосной развертке: при нарастании переднего восходящего фронта импульса триггер 37 переходит в положение «О, а триггер 41 - в положение «1, что соответствует состоянию поиска кода запирания. Сигнал с выхода триггера 37 постоянно подается на счетчик 39. Осуществляется поиск кода запирания развертки.

Отпирание счетчика 39 происходит лишь при прохождении сигнала с дешифратора 2 на выход дешифратора 40, триггеры 37 к 41 переходят тогда из состояния «0,1 в состояние «1,0.

При нарастании переднего фронта импульса система возвраш,ается в состояние синхронизации «1, О.

Потеря кодовой комбинации запирания однонолосной развертки влечет за собой потерю кодовой комбинации запирания многополосной развертки, так как сигнал устанавливает триггер 37 в положение «О, а триггер 41 в положение «1. Блок синхронизации 8 принимает речевые каналы, регистр 61 иринимает информацию, поступаюшую последовательно с многоканальных линий; передает ее в параллельном коде через вентиль 62 в регистр 63 параллельного действия.

Регистр 63 соединяется с двумя запоминающими блоками 42, 43. Информация из запоминающих блоков 42, 43 и инфор.мация о состоянии счетчика 49 подаются к соединительной сети (выход 64). Вентили 65 и 66 обеспечивают запись информации в запоминающие блоки 42, 43.

При опознавании наличия сигналов выходной триггер 53 изменяет свое состояние, перебрасывая запись в запоминающий блок 42 и считывание из запоминающего блока 43, затем триггер 51 возвращается в состояние покоя, освобождая счетчик 49, 1 оторый вновь устанавливаетсоя на «О, после срабатывания триггера 52.

В этот момент запоминающий блок 43 считывается, а появление сигнала, извещающего о конце зациси в запоминающий блок 42, 1про,веряется в моменты coi и ШБ.

Как только пО(Дтверждается наличие сигнала, извещающего о конце записи, триггер 53 изменяет свое состояние, перебросив запись в запоминающий бло1К 43 и считывание из запоминающего блока 42, затем триггер 52 возвращается в состояние покоя, отпирая счетчик 49, который установится в полол ение 16 после срабатывания триггера 51. Матрица 57 преобразует информацию о виде групп двух бинарных элементов, называемых (е, d). Эти элементы (е, d) передаются к многократным самописцам осциллограмм по многоканальной линии 67 с помощью передающего блока 58.

В обратном направлении информации сигнализации, иоступающая с соединительных цепей по многоканальной линии 67 в виде групп двух бинарных элементов, принимается приемным блоком 56. Матрица 57 преобразует сигнал в группы четырех бинарных элементов, которые затем чере: передающий блок 58 попадают к оконечным цифровым станциям по многокана.аьным линиям 68.

На фиг. 5 изобрал ена структурная электрическая схема блока синхронизации 9 информации сигнализации. Приемный блок 69 принимает информацию «семафорного канала, а передающий блок 70 передает эту информацию к выносным соединительным блокам. Приемный и передающий блоки 69, 70 соединены с блоком 71 управления. По многоканальным линиям

72 информация сигнализации тракт за трактом поступает в передающий блок 70 и затем иередается к многократным самонисцам.

При использовании иредложенного устройства уменьшаются потери информации при передаче по каналам связи.

Формула изобретения

1. Устройство синхронизации временных каналов для телефонной станции, содержащее блок временной коммутации, два выхода которого подключены соответствепно к первым и вторым входам блока

переключателей и блока соединения местных абонентов, к третьему входу которого подключен соответствующий выход блока временной коммутации через временной соединительный блок, а также узлы синхронизании информации по числу многоканальных иЧиний связи, причем к входам двух узлов синхронизации информации через соответствующие многоканальные линии связи подключены соответственно выходы блока соединения выносных абонентов и блока переключателей, отличающееся тем, что, с целью уменьшения потерь информации ири передаче по каналам связи, каждый узел сиихронизации

информации выполнен в виде объединенных по входу блока синхронизации и речевых каналов, блока синхронизации информации сигнализации и блока обнаружения и контроля кодов запирания одиополосной и многополосной разверток, выхот которого подключен к управляющим входам блока синхронизации речевых каналов и блока синхронизации информации сигнализации, при этом выход блока синхронизации речевых каналов подключен к соответствующему входу временного соединительного блока, один из выходов которого подключен к другому входу блока синхронизации информации сигнализации, другой выход которого подключен к соответствующему входу блока временной коммутации.

2. Устройство по п. 1, отличающееся тем, что блок обнаружения и контроля кодов запирания однополосной и многополосной разверток содержит последовательно соединенные регистр сдвига и дешифратор, один из выходов которого подключен к первому входу первого элемента И непосредственно, а к первому входу второго элемента И через первый инвертор, к вторым входам первого и второго элементов И подкючен выход третьего элемента И, а выходы первого и второго элементов И соответственно через четвертый и пятый элементы И подключены к входам первого элемента ИЛИ, выход которого через последовательно соединенные шестой элемент И и второй элемент ИЛИ, к другому входу которого подключен выход первого элемента И через седьмой элемент И, подключен к одному из входов двух последовательно соединенных триггеров, к другому входу первого из которых подключены выходы восьмого и девятого элементов И через третий элемент ИЛИ, а другой выход второго триггера непосредственно и через третий триггер подключен к входам десятого элемента И, выход которого чере.з счетчик подключен к входу второго дешифратора, первый выход которого подключен к одному из входов третьего элемента И, а второй выход второго дешифратора подключен к одному из входов пятого, седьмого, восьмого и девятого элементов И непосредственно и через второй инвертор к соответствующему входу четвертного элемента И, кроме того, выход первого счетчика подключен к одному из входов регистра сдвига, к соответствующему входу первого счетчика и через третий инвертор к одному из входов третьего элемента И, другой выход первого дешифратора через четвертый инвертор подключен к одному из входов одиннадцатого элемента И, выход которого через последовательно соединенные пятый инвертор, четвертый триггер и второй счетчик подключен к входу третьего дешифратора, выход котороГО подключен к первому входу двенадцатого элемента И, к двум другим входам которого подключены соответственно третий выход второго дешифратора и соответствующий выход первого счетчика, а выход двенадцатого элемента И подключен к соответствующему входу четвертого и пятого триггеров, к другому входу которого подключен 1ВЫХОД четвертого пнвертора, а выход пятого триггера подключен к соответствующему

0 входу одиннадцатого элемента И, причем управляющий вход четвертого и пятого тр.иггеров соединен с выходом десятого элемента И, и управляющий вход второго

5 счетчика - с четвертым выходом второго дешифратора.

3.Устройство по п. 1, отличающееся, тем, что блок синхронизации речевых каналов содержит первый и второй запоминающие блоки, к входам которых подклю0чены соответствующие блоки записи - считывания, к управляющим входам которых подключены соответствующие выходы формирователей временных интервалов, блок вынесения решения, состоящий из счетчика,

5 выход которого подключен к входу дешифратора, выходы которого подключены к соответствующим входам.иервого и второго триггеров, к другим входам которых подключены соответствующие выходы выходного триггера, а выходы этих триггеров подключены к соответствующим входам счетчика и двух элементов И, выходы которых соединены с соответствующими входа5ми выходного триггера.

4.Устройство по п. 1, отличающееся тем, что блок синхронизации информации сигнализации содержит две цепи, каждая из которых состоит из последовательно соединенных приемного блока, мат0рицы перекодирования и передающего блока, к управляющим входам которых подключены выходы блока управления.

Источник информации, принятый во

5 внимание при экспертизе;

1. Синхронизирующее оборудование в узле временной коммутации (система Платан). Commutation et Electronique, 1970, № 28, с. 21-39.

,1i .

-- j iП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой коммутации | 1982 |

|

SU1308209A3 |

| Устройство временной ступенчатой коммутации | 1971 |

|

SU522835A3 |

| Устройство для проверки линии | 1970 |

|

SU485611A3 |

| Устройство для перемещения и установки рабочего органа машины в заданном положении | 1973 |

|

SU506316A3 |

| Молекулярный вакуумный насос | 1974 |

|

SU580850A3 |

| Временной коммутатор для многоканальных систем связи с временным разделением каналов | 1971 |

|

SU608493A3 |

| Полосно-пропускающий сверхвысокочастотный фильтр | 1975 |

|

SU560541A3 |

| Неблокирующая система связи,например телефонной | 1970 |

|

SU510179A3 |

| Молекулярный вакуумный насос | 1974 |

|

SU667162A3 |

| Устройство для отображения телетекста на экране телевизионного приемника | 1980 |

|

SU1181568A3 |

0 Э

.-:1-

VS

Авторы

Даты

1979-02-28—Публикация

1972-06-29—Подача