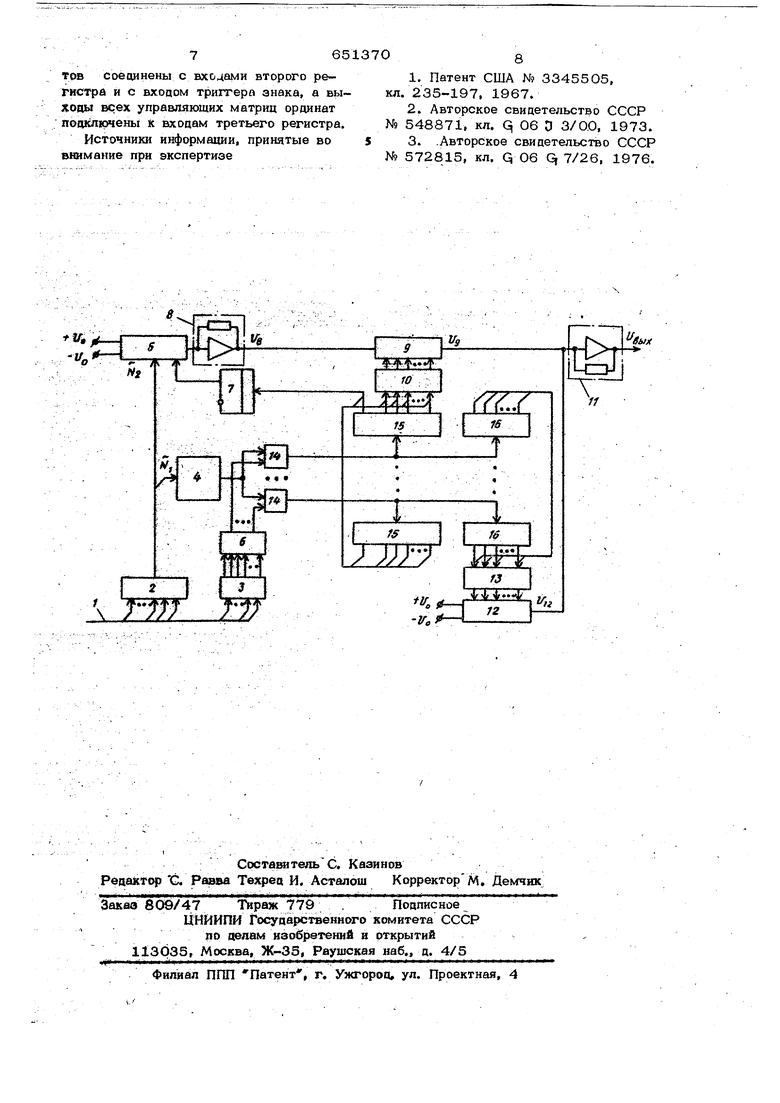

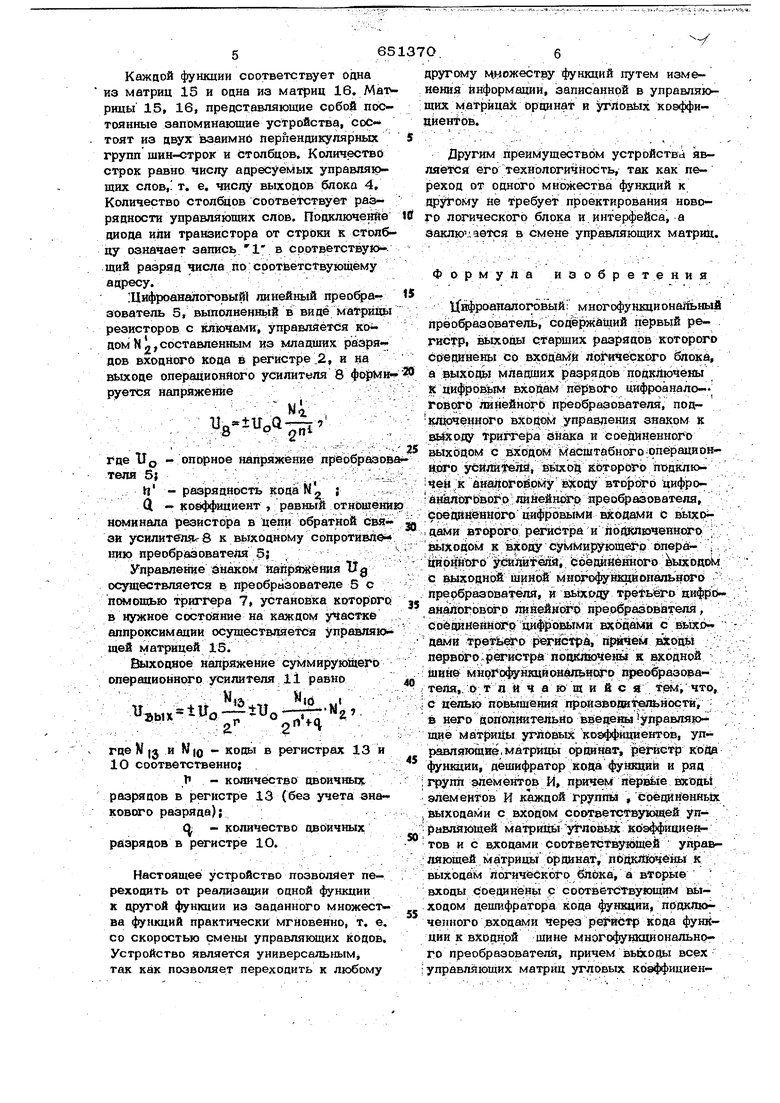

(54) ВДФРОАНАЛОГШЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ аналоговому входу второго цифроаналбгавого линейного преобразователя, соецинен кого цифровыми входами с выходам } второго регистра и подклкяенного вькЬдом к входу суммирующего операционного усилителя, соединенного вЫхойом с выходной шиной многофункционального преобразователя и Bbixoay третьего аи(| аиалоговр-. го линейного преобр ователя, соединенного цифровыми вхоШмй с выходами третьего регистра, nfJHjeM biioaM йёрвого peTHCtpa подключены к входной шине многофункцйбз альнйгь йреобразователя СЗ). НедЬст( ttpoi oin«na является низкая вроиэводи ельмость при работе с различными ви дами функций чго опредейется необходим остью {учиойёамёйь лозтаческЬго и интерфейсноего ёйоков при переходе с одной ШО) опальной аабиси- «бсти на другую Кроме этсхго, интерфейсный блок не йшшется изделием микро ёктрЬйккн и Шначитеш able габарнт онае ;Ьшд пойаё ате йи, . {{эобретёния яв:пяется повыш©йив йройзввдйтельйост. Подставленная ОЕё/ш йостигбе с:я тем, что в Ш1фроа 1шяргр&1Е 1й лшогофутскдйЬндльшй вре6бразо1)Е11геяь дойрЛШтёдЕьно 6йеШе яь -у|5$ ай я;1сЙй€ Ш рШ УШсШ - ке аффйкмбнтоа, увравля1ощие мвтршы орШгШт, регистр кода функции дешифратор кода функции и рйд групя Ш1ёментов И, причем пёцмэыё KkoOfci элементов И каждой ripytiirebi, сЬёф неЙ1е 1х шходами с входами серТЕ 1Ест уюи1ей у1Ц аё/{яюшей матрицы угловых коэффйая нтов и с входами соотоё1ч;та.у1сва управл гющей матрицы ордииат, почдасякйевд к вШодам л{)Гйческого блоха, в вжвды соединены с :ойтве ЪтвуюШм вькодом дешифратора кода 4 iaq«{«, дойкйюченнйго вхбйшй регистр кода функши к Шодной шине ми Я 1ЖЦйо1{ального преобр ов/а ёШ, аы1Хбш г всех Уйравлйюших матриц угловых коэффиЦи ентов соедин нь с вхЬ-i дамн йторсйо регистра и ахьдЬм TpKit«рв ёнакр, а аьосоды всех уйры1ваякяййх матри1Х брдйнат пбдклйчены к входам третьего регистра. , На чертеже изображена блок-схема устройства,; Устройство содержит входную шину 1, соединенную с 1вХбДоМ liepeta o р истра 2 и ретисТра .йода функции 3, Выходы старших разрядов регистра 2 подключены к-вхЬйам йогичеСкого блока 4, а выходы младших разрядов - к цифровым входам первого цифроаналогового линейного преобразователя 5, выходы регистра 3 соединены с входами дешифратора кода функции 6, Выходы преобразователя 5, пошшюченного входом управления знаком к выходу триггера знака 7, через масштабный операционный усилитель 8 соединен с аналоговым входом второго цифроанвлоговдг 6 линейного преобразоваТеля 9, подключенного Цифровыми входами к выходам второгр рерйс;тра 10. Выход преобразователя 9 соединен с входом суммирующего операционного усилитедя 11 и с/вьцсодом третьего цнфроанаяого-. всяго линеЙйЬго преобразователи 12, цифрйбйе входи которо го подключены к выХодш третьего регистра 13. Первые входь1 .элементо) И ряда групп 14 соединены с вьцсодами блока 4, а их вторые входы подключены к боотве тстёуюишм вькодам дешифратора 6. Выходы элементов И каждой группы И соеданёнь с входам соответст1 ующ0й управляющей матрицы угДовУх коэф нцдаентрв 15 и с входами со0тветс1Р:йующеЙ управляющей матрицы ординат 16. Ёьковеь матриц 15 подключены к входам peJ ecTpa Ю и входу триггера 7, а йыходы матриц 16 - k вхоцакл perHdfpa 13. : Работает многофушадаональный преобразователь следующим образом. По входной шийе 1 поступает ин| ормационное слово, coctoiiBiee ид кода аргумента N , который записывается в регистр 2, и ко да функции , который записывается в .регистр 3. , , -. ,;,-:-И-.- /; Логический бярк 4 по значениям старших разрядов JMj крда Н рпрег1еляёт номер текушегР поаинтервала задания аргумента при 1Ч сочно- войной аппроксимаций. Крйичестйо подынтервалов равно ЧйСЛу два в ус епейи, срртветствуюшей чйёлу сТЕраих разрядрв двоичнсго кода flj . &)1хоаы бяока 4 coeiwfteHbi спервыми вХРДаУй ёйемёктов И ряда групп 14. Число групп 14 равно числу воспройэводимьк фуййцйй, а число элементов .И в каждой грутте равнр чэйСЛ5г выходов блои 4. :;::- ..::.. :Г; - ,. Лешифратрр 6 ttP з1№ачеш1Ю кода Р Рсуществляет йодачу отпирающего сигнала на сЬоТ1звтствуюшую грушу элементов И 14, BbtxcfaHbie бнгналь с (Злока 4 через Группу. элёмен Роа И 14 поступают на входы соответствующих матриц 15 и 16, в которьос храйятся коды подьштервальных значений угловьгх коэффициентов и ординат i -ой функции. Каждой функции соответствует одна из матриц 15 и одна из матриц i6. Мат рицы 15, 16, представляющие собой постоянные запоминающие устройства, состоят из двух взаимно перпендикулярных групп шин-строк и столбцов. Количество строк равно числу адресуемых управляющих слов, т. е. числу выходов блока 4, Количество столбцов Соответствует paiaрядности управляющих слов. Подключение диода или транзистора от строки к столб цу означает запись 1 в срртветствук щий разряд числа по;сротьетствующёму адресу. ;Цифроаналоговый1 линейный преофазователь 5, выполненный в виде матрицы резисторов с ключами, управляется N я,составленным из младщих разрядов входного кода в регистре,2, и на выходе операционного усилит« ля 8 форми руетря напряжение Где и о - опорное напряжение преобразов теля 5; Н - разрядность кодаМ ; Q - коэффициент 1 равный отношени номинала резистора в цепи обратной связи усилитеп51гв к выходному сопротивлеНИК) преобразователя 5; Управление знаком напряжения Ug осуществляется в преобразователе Б с помощью триггера 7, установка которого в нужное состояние на каждом участке аппроксимации осуществляется управляющей матрицей 15. Выходное напряжение суммирующего операционного усилителя 11 равно ,«tU где N и и NIQ - коды в регистрах 13 и 10 соответственно; f - КОЛИЧ6СТ6О двоичных разрядов в регистре 13 (без учета знакового разряда); ( - количество двоичных разрядов в регистре 10. Настоящее устройство позволяет переходить от реалязацци одной функции к другой функции из заданного множества функций практически мгновенно, т. е. со скоростью смены управлякмцих кодов. Устройство является универсальным так как позволяет переходить к любому другому множеству функций путем изменения информации, записанной в управляющих матрица ординат и угловых К08ФФИциен1ОВ. Другим преимуществом устройства являёч-Ся его технологичность, так как переход от одного множества функций к другому не требует проектирования нового логического блока и.интерфейса, а йаклю 1ав1№я в смене управляющих матриц. Фор м у л а изобретения ХЙгфроапалоговый многофункционайькый преофазователь, содержащий первый регистр, выходы старших разрядов которсяго соединены со входши логического блоки, а выходы младших разрядов подключены к цифровым входам первого цифроанало- Гового линейного преобразователя, подключенного входом управления знаком к выходу триггера знака и соединенного ш хобом с входом масщтабнмго операционного усйлителй, въиоа которого подключен к аналогобому BTofjofo цифроаналогового линейнсжч преобразователя, соедкненногч) цифровыми входами с выходами второго регистра и подаслюченного выходом к входу суммирующего опера- . ииоянЪго усйлнтё)1й, Ьоедайенного выходом с выходной шиной МНОГо4 уШС 1ИОНалЫ10ГО преобразователя, и выходу третьего днфроаналогового линейного преобразователя, соединенного цифровьтми входами с выхо- дамй третьего регистр, причем ксоды первого.регистра пош(Яючены к входной ШИН& мнр1 о«|унщнональйс о преобразователя, отпйчающийся feM, что, с целью повышения тфоизвооитальности, в него дополнительно вве{{ешл управляющие матрицы угповых коэффициентов, управляющие, матрицы с оияат, регистр кода функции, дешифратор нова фушщии и ряд групп элементов Н, причем первые входы элементов И каждой группы , соещ1ненных выходами с входом соответствукяцей управляющей матрицы угловых коэффициес тов и с входами Соответствуяйцей управляющей матрицы ординат, подкякяены к выходам логического блока, а вторые входы соединены с соответствующим вь1ходом дещифратора кода функции, подключенного входами рез регистр кода функции к входной шине многофункционального преобразователя, причем вькоды всех управляющих матриц угловых коаффициенTOB соецинены с входами второго регистра и с вхоцом триггера знака, а выХооы всех управляющих матриц ординат поцкяк)чены к вхоцам третьего регистра.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3345505, кл. 235-197, 1967.

2.Авторское свидетельство СССР № 548871, кл. q 06 О З/ОО, 1973.

3..Авторское свидетельство СССР № 572815, кл. Q 06 Q 7/26, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый функциональный преобразователь | 1980 |

|

SU895973A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для отображения дугОКРужНОСТЕй и эллипСОВ HA эКРАНЕэлЕКТРОННО-лучЕВОй ТРубКи | 1978 |

|

SU807264A1 |

| Цифро-аналоговый функциональный преобразователь | 1978 |

|

SU734728A1 |

| Цифро-аналоговый функциональный преобразователь | 1976 |

|

SU572815A1 |

Авторы

Даты

1979-03-05—Публикация

1977-03-14—Подача