(5) ЦИФРО-АНАЛОГОВЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Гибридный функциональный преобразователь | 1980 |

|

SU879610A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Гибридный функциональный преобразователь | 1984 |

|

SU1203546A2 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

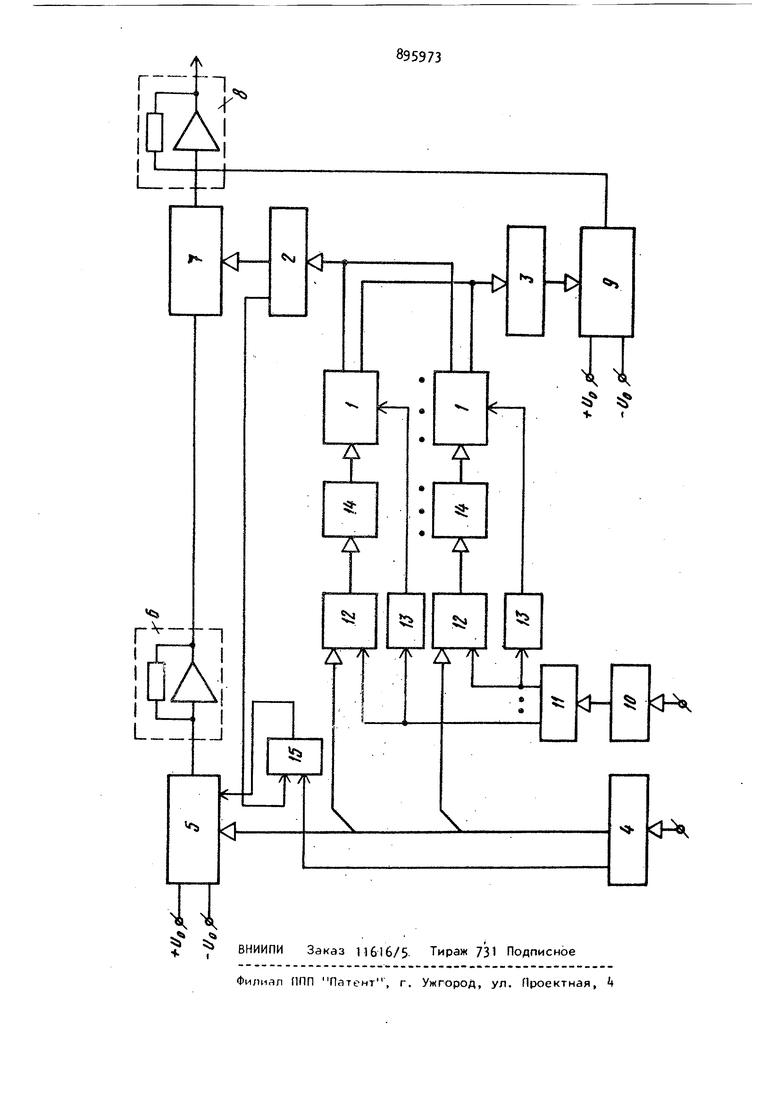

Изобретение относится к автомати ке и вычислительной технике и может быть использовано для функционально го преобразования цифровых сигналов в аналоговый выходной сигнал. Известен цифро-аналоговый многофункциональный преобразователь, содержащий регистр кода аргумента, регистр кода функции, счетчики, блок совпадения кодов, генератор импульсов, дешифраторы, блок памяти преобразователь код-частота, триггер знака, элемент И, реверсивный счетчик, регистр функции и выходной цифро-аналоговый множительный блок Недостатком данного многофункцио нального преобразователя является ограниченное быстродействие. Наиболее близким к изобретению является цифро-аналоговый многофунк циональный преобразователь, содер.жащий п (где п - количество воспроизводимых функций) блоков памяти первые и вторые выходы каждого из которых подключены к входам первого и второго регистров соответственно, первый дешифратор адреса, п групп элементов И, третий регистр, соединенный входом с шиной ввода кода аргумента, а выходами разрядов -с циф ровыми входами первого цифро-аналогового линейного преобразователя, подключенного аналоговыми входами к шинам разнополярных опорных напряжений, а выходом - к входу масштабного операционного усилителя, выход которого соединен с аналоговым входом второго .цифро-аналогового линейного преобразователя, подключенного цифровыми входами к выходам разрядов первого регистра, а выходом - к входу выходного суммирующего операционного усилителя и к выходу третьего цифроаналогового линейного преобразователя, соединенного аналоговыми входами с шинами разнополярных опорных напряжений, а цифровыми входами - с выходами разрядов второго регистра, и четвертый регистр, подключенный входом к шине ввода кода функции, а вых дами разрядов - к входам дешифратора кода функции, каждый i-ый () выход которого соединен с первыми входами элементов И 1-ой группы, под ключенных выходами к адресным входам 1-го блока памяти, а вторыми вхо дами - к выходам первого дешифратора адреса, соединенного входами с выходами старших разрядов третьего регистра 2. Однако конструктивная сложность преобразователя обусловленная нали|чием аппаратурной избыточности форми рования подинтервалов аппроксимации воспроизводимых функций. Цель изобретения - упрощение цифр аналогового многофункционального пре образователя. ,Цель достигается тем, что цифроаналоговый многофункциональный преоб разоаатель, содержащий п (где п количество воспроизведенных функций) блоков памяти, первые и вторые выходы каждого из которых подключены к входам первого и второго регистров соответственно, первый дешифратор адреса, п групп элементов И, третий регистр, соединенный входом с шиной ввода кода аргумента, а выходами разрядов с цифровыми входами перво го цифро-аналогового линейного преоб разователя, подключенного аналоговыми входами к шинам разнополярных опо ных напряжений, а выходом - к входу масштабного операционного усилителя, выход которого соединен с аналоговым входом второго цифро-аналогового линейного преобразователя, подключенно го цифровыми входами к выходам разрядов первого регистра, а выходом к входу выходного суммирующего операционного усилителя и к выходу третьего цифро-аналогового линейного преобразователя, соединенного аналоговыми входами с шинами разнополярны опорных напряжений, а цифровыми входами - с выходами разрядов второго регистра, и четвертый регистр, подключенный входом, к шине ввода кода функции, а выходами разрядов - к входам дешифратора кода функции, каждый -ый. () выход которого соединен с первыми входами элементов И 1-ой группы, содержит п элементов задержки сумматор по модулю два и дополнительные дешифраторы адреса со второго по п-ый, причем каждый 1-ый () элемент Задержки подключен входом к i-му выходу дешифратора кода функции, а выходом к входу управления считыванием i-го блока памяти, соединенного адресными входами через i-ый дешифратор адреса с выходами элементов И i-ой группы, подключенных вторыми входами к выходам старших разрядов третьего регистра,выход знакового разряда которого соединен с первым входом сумматора по модулю два,подключенного вторым входом к выходу знакового разряда первого регистра,а выходом - к входу управления знаком первого цифро-аналогового линейного преобразователя. На чертеже изоЬражена блох-схема цифро-аналогового многофункционального преобразователя. Схема содержит п (где п - количество воспроизводимых функций) блоков 1 памяти, первые и вторые выходы каждого из которых подключены к входам первого и второго регистров 2 и 3 соответственно. Третий рег- стр соединен входом, с шиной ввода аргумента, а выходами разрядов - .: цифровыми входами первого цифро-аналогового линейного преобразователя 5Последний подключен аналоговыми входами к шинам разнополярных опорных напряжений ±Lt) , а выходом - к входу масштабного операционного усилителя 6 Выход усилителя 6 соединен с аналоговым входом второго цифро ана-гогпйо го линейного преобразователя 1, подключенного цифровыми входами к выходам разрядов регистра 2, а выходом к входу выходного суммирующего операционного усилителя 8 и к выходу третьего цифро-аналогового линейного преобразователя 9. Последний соединен аналоговыми входами с шинами разнополярных опорных напряжений ±Uc,, а цифровыми входами - с выходами разрядов регистра 3. Четвертый регистр 10 подключен входом к шине ввода кода функции, а выходами разрядов - к входам дешифратора 11 кода функции. Каждый i-ый () выход дешифратора 11 соединен с первыми входами элементов И 5-ой группы 12 и с входом i-го элемента 13 задержки, выход которого подключен к входу управления считыванием i-го блока 1 памяти, адресные входы которого через I-ый дешифратор 1 адреса соединен с выходами элементов И i-ой группы 12, подключенных вторыми входами и выходом старших разрядов регистра k. Выход знакового разряда регистра Ц соединен с первым входом сумматора 15 по модулю два, подключенного вторым входом к выходу знакового разряда регистра 2, а выходом - к входу уп равления знаком преобразователя 5. Цифро-аналоговый многофункционал ный преобразователь работает следую щим образом. Перед началом работы преобразова тель программируется, т.е. в каждый из блоксзв 1 памяти записываются кодовые значения параметров аппроксим ции одной из воспроизводимых функци При этом количество подинтервалов ап проксимации для каждой иа воспроизводимых функций выбирается индивидуально в зависимости от особенностей данной функции и требований к точности ее воспроизведения. Различн му количеству подинтервалов аппроксимации для каждой из воспроизводимы функций соответствует различное коли чество старших разрядов кода аргумента , используемых для дешифрации кода номера подинтервала и различные по сложности реализации (т.е. по количеству используемых элементов блоки 1 памяти, дешифраторы 14 адреса и группы 12 элементов И. При работе многофункционального преобразователя на входы регистров k и 10 подаются соответственно прямой код аргумента, который записывается в регистр k, и код функции, записыва емый в регистр 10. После дешифрации кода функции дешифратором 11, сигнал возбуждения с соответствующего выхода дешифратора 11 воздействует на первые входы выбранной группы 12 элементов И. В результате этого необходимое число старших разрядов регистра Ц подключается к входам соответствующего дешифратора адреса. Одновременно сигнал возбуждения задерживается на некоторое время элементом 13 задержки, после чего воздействует на вход управления считывания соответствующего блока 1 памяти, на адресных входах которого к этому времени сформирован сигнал адресации к выбранной ячейке блока п мяти. В результате прямой код началь ной ординаты записывается в регистр а прямой код углового коэффициента в регистр 2. Все разряды кода аргумента с регистра за исключением знакового разряда воздействуют на цифровые входы первого преобразователя 5, поэтому на выходе усилителя 6 формируется напряжение, пропорциональное этому коду аргумента. Знак этого напряжения определяется управляющим сигналом на выходе сумматора 15 по модулю два, зависящим от состояния знаковых разрядов регйст- ров 2 и 4. Напряжение с выхода усилителя 6 умножается на коэффициент передачи второго преобразователя 7, выходной ток которого с помощью аыходного суммирующего усилителя 8 суммируется с выходным током третьего преобразователя 9. Так как преобразователи 7 и 9 управляются кодами , записанными в регистры 2 и 3 соответственно, то на выходе суммирующего усилителя 8 формируется напряжение, соответствующее кусочно-линей ной функции, аппроксимирующей данную воспроизводимую функцию из общего множества п воспроизводимых функций. При смене кода функции на регистре tO воспроизводится другая функция из множества воспроизводимых функций. Предлагаемый цифро-аналоговый многофункциональный преобразователь по сравнению с известным обладает более простой реализацией, так как в нем объем каждого из блоков 1 памяти задается индивидуально для каждой из воспроизводимых функций. 8 известном преобразователе, содержащем общи.й дешифратор адреса для всех воспроизводимых функций, объемы блоков памяти одинаковы и задаются исходя из разрядности входного кода общего дешифратора адреса, причем эта разрядность выбирается по разбиению одной из воспроизводимых функций на наибольшее количество интервалов аппрокЪимации. Формула изобретения Цифро-аналоговый многофункциоальный преобразователь, содержащий ( где п -количество воспроизводимых ункций) блоков памяти, первые и вторые выходы каждого из которых подключены к входам первого и второго регистров соответственно, первый ешифратор адреса, п групп элеменов И, третий регистр, соединенный входом с шиной ввода кода аргумен та, а выходами разрядов - с цифровыми входами первого цифро-аналогового линейного преобразователя,подключенного аналоговыми входами к шинам раэнополярных опорных напряжений, а выходом - к входу масштабного операционного усилителя, выход которого соединен с аналоговым входом второго цифро-аналогового линейного преобразователя подключенного цифровыми входами к выходам разрядов первого регистра, а выходом - к входу выходного суммирующего операционного усилителя и к выходу третьего цифроаналогового линейного преобразователя, соединенного аналоговыми входами с шинами разнополярных опорных напряжений, а цифровыми входами - с выходаг 1 разрядов второго регистра, и четвертый регистр, подключенный вхог дом к шине ввода кода функции., а выхдами разрядов - к входам дешифратора кода функции, каждый i-ый () выход которого соединен с первыми входами элементов И i-ой группы, )этличающ. ийся тем, что, с целью упрощения цифро-аналогового многофункционаяьнюго преобразователя, он содержит п элементов задержки сумматор по модулю два и дополнительные дешифраторы адреса со второго по п-ый, причем каждый i-ый (l:fij n) элемент задержки подключен входом к i-му выходу дешифратора кода функции, а выходом - к входу управления считыванием 1-го блока памяти, соединенного адресными входами через i-ый дешифратор адреса с выходами элементов И {-ой группы, подключенных вторыми входами к выходам старших разрядов третьего регистра, выход знакового разряда которого соединен с первым входом сумматора по модулю два, подключенного вторым входом к выходу знакового разряда первого регистра, а выходом - к входу управления знаком первого цифро-аналогового линейного преобразователя.

Источники информации, принятые во внимание при экспертизе

кл. G Об G 7/2б,0.04.80.

г

««

V

Г

895973

Авторы

Даты

1982-01-07—Публикация

1980-04-17—Подача