1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах адресования подвижных объектов установок непрерывного транспорта.

Известно устройство для проверки кода на четность, содержащее регистр, схемы И, ИЛИ 1.

В данном устройстве имеется промежуточный запоминающий регистр на статических триггерах с вентилями на входе. Причем при наличии внещнего запоминающего устройства для запоминания кода в этом регистре нет необходимости; более того, его наличие, кроме дополнительных аппаратурных затрат, приводит к увеличению времени контроля.

При реализации устройства на ферриттранзисторных элементах требуются значительные затраты обрудования.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство, описанное в 2.

Это устройство содержит в каждом разряде, кроме первого, четыре феррит-транзисторных элемента и два феррит-транзисторных элемента в первом разряде, причем информационные входы феррит- транзисторных элементов соединены с соответствующими информационными входами устройства, а первые входы считывания подключены к тактовому входу устройства.

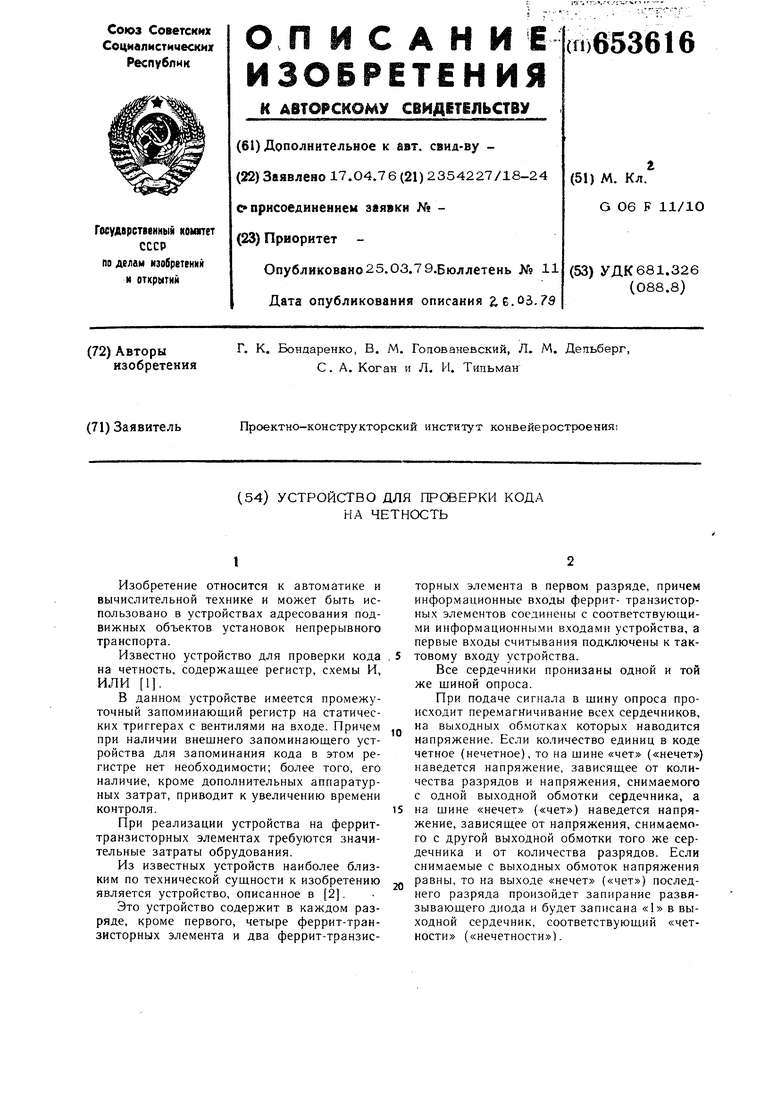

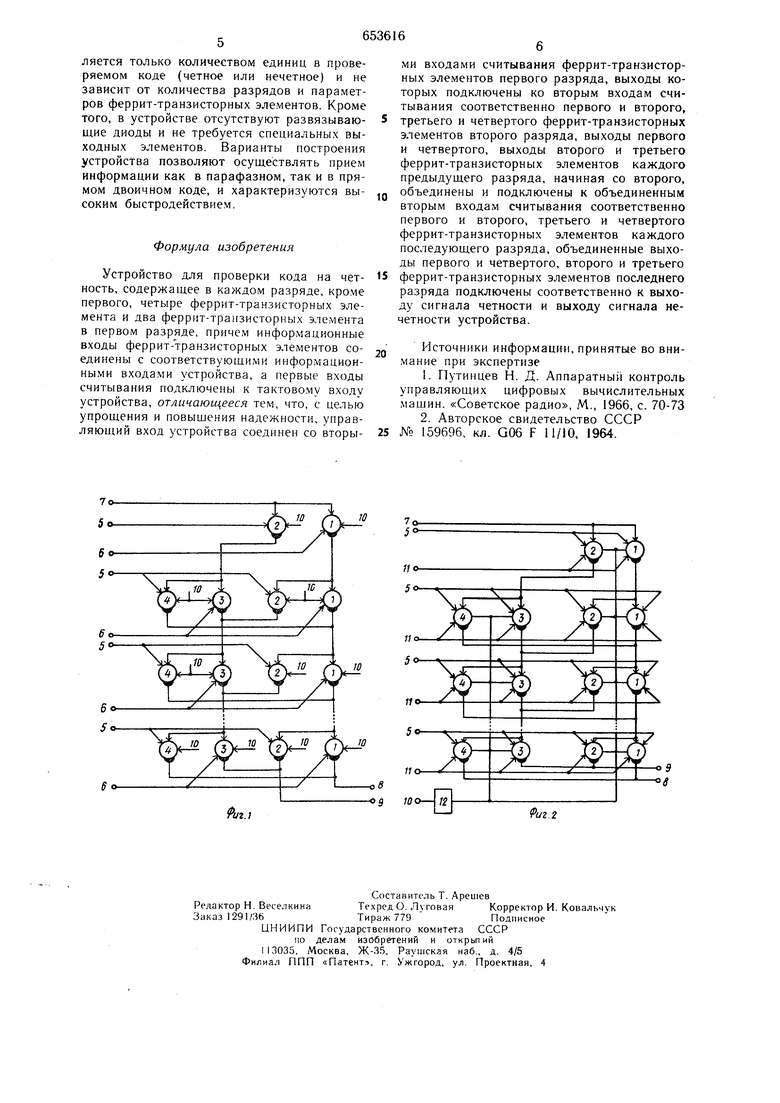

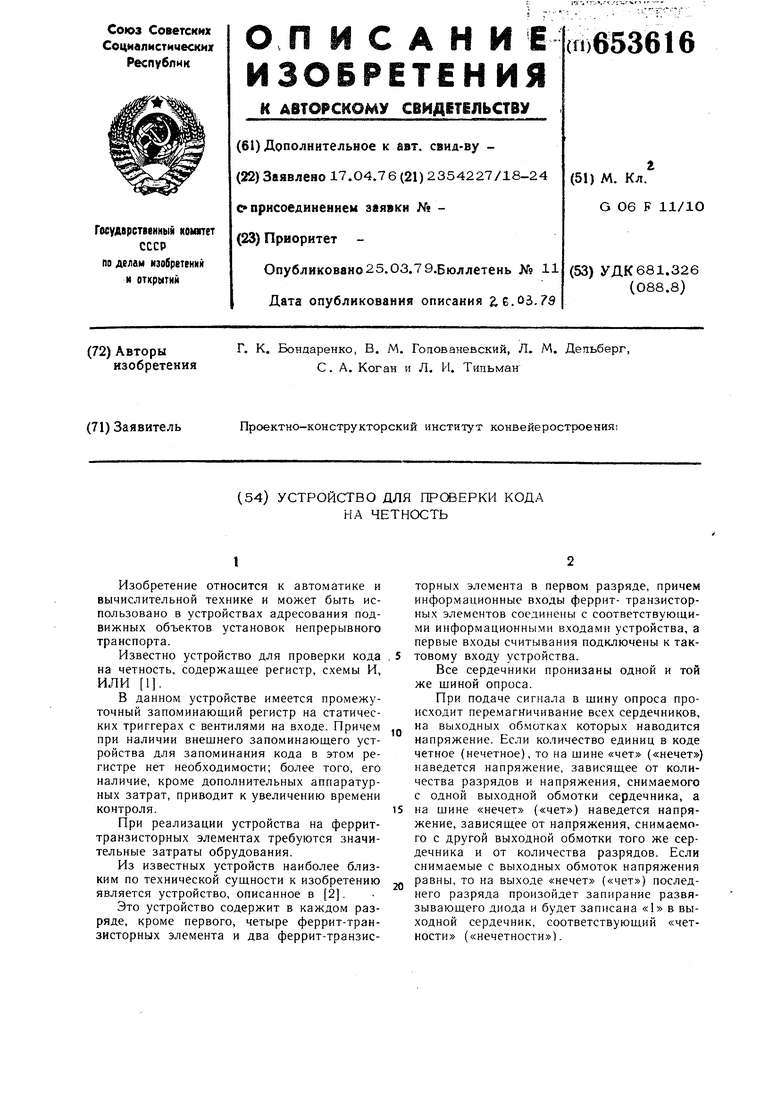

Все сердечники пронизаны одной и той же шиной опроса.

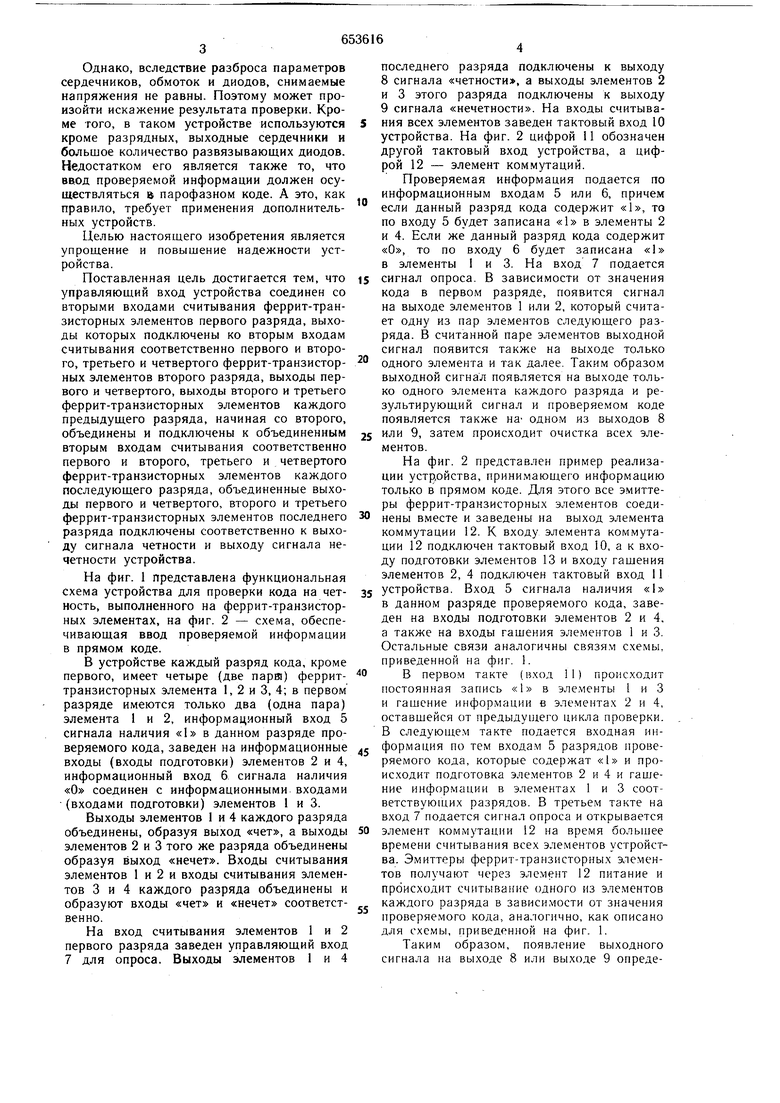

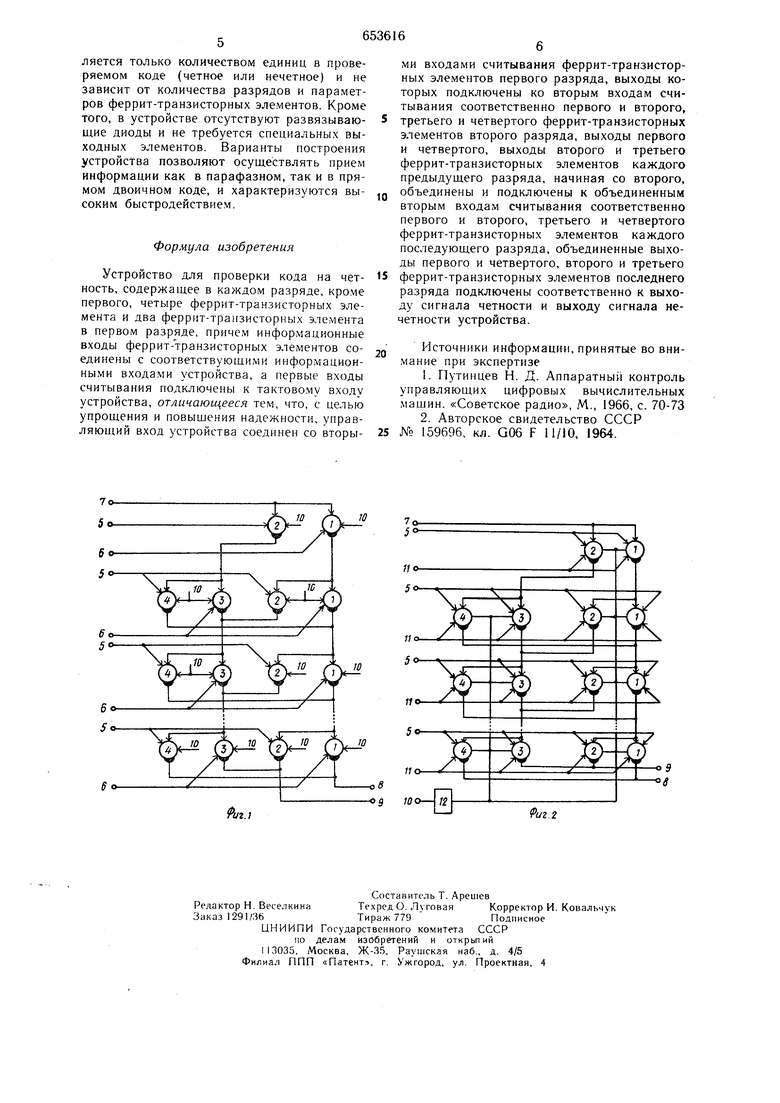

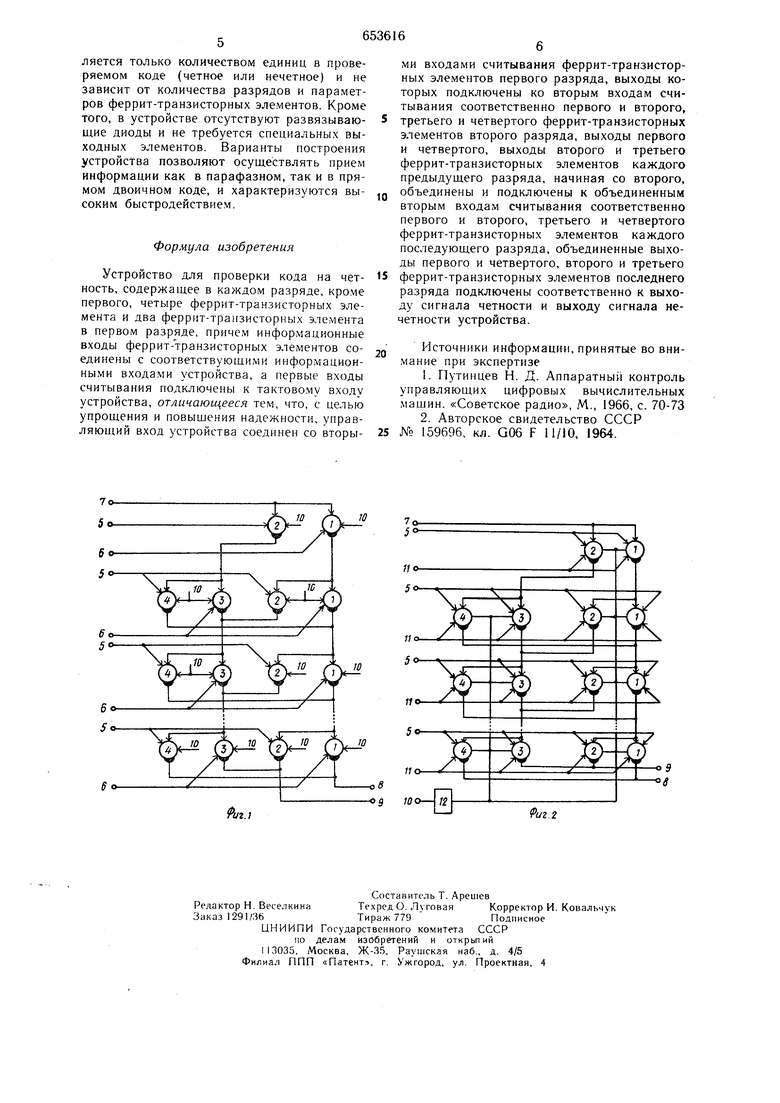

При подаче сигнала в шину опроса происходит перемагничивание всех сердечников, на выходных обмотках которых наводится напряжение. Если количество единиц в коде четное (нечетное), то на щине «чет («нечет) наведется напряжение, зависящее от количества разрядов и напряжения, снимаемого с одной выходной обмотки сердечника, а на шине «нечет («чет) наведется напряжение, зависящее от напряжения, снимаемого с другой выходной обмотки того же сердечника и от количества разрядов. Если снимаемые с выходных обмоток напряжения равны, то на выходе «нечет («чет) последнего разряда произойдет запирание развязывающего диода и будет записана «Ь в выходной сердечник, соответствующий «четности («нечетности). Однако, вследствие разброса параметров сердечников, обмоток и диодов, снимаемые напряжения не равны. Поэтому может произойти искажение результата проверки. Кроме того, в таком устройстве используются кроме разрядных, выходные сердечники и большое количество развязывающих диодов. Недостатком его является также то, что ВВ.ОД проверяемой информации должен осуществляться 1 парофазном коде. А это, как правило, требует применения дополнительных устройств. Целью настоящего изобретения является упрощение и повышение надежности устройства. Поставленная цель достигается тем, что управляющий вход устройства соединен со вторыми входами считывания феррит-транзисторных элементов первого разряда, выходы которых подключены ко вторым входам считывания соответственно первого и второго, третьего и четвертого феррит-транзисторных элементов второго разряда, выходы первого и четвертого, выходы второго и третьего феррит-транзисторных элементов каждого предыдущего разряда, начиная со второго, объединены и подключены к объединенным вторым входам считывания соответственно первого и второго, третьего и четвертого феррит-транзисторных элементов каждого последующего разряда, объединенные выходы первого и четвертого, второго и третьего феррит-транзисторных элементов последнего разряда подключены соответственно к выходу сигнала четности и выходу сигнала нечетности устройства. На фиг. 1 представлена функциональная схема устройства для проверки кода на четность, выполненного на феррит-транзисторных элементах, на фиг. 2 - схема, обеспечивающая ввод проверяемой информации в прямом коде. В устройстве каждый разряд кода, кроме первого, имеет четыре (две паря) ферриттранзисторных элемента 1, 2 и 3, 4; в первом разряде имеются только два (одна пара) элемента 1 и 2, информационный вход 5 сигнала наличия «1 в данном разряде проверяемого кода, заведен на информационные входы (входы подготовки) элементов 2 и 4, информационный вход 6 сигнала наличия «О соединен с информационными входами (входами подготовки) элементов 1 и 3. Выходы элементов 1 и 4 каждого разряда объединены, образуя выход «чет, а выходы элементов 2 и 3 того же разряда объединены образуя выход «нечет. Входы считывания элементов 1 и 2 и входы считывания элементов 3 и 4 каждого разряда объединены и образуют входы «чет и «нечет соответственно. На вход считывания элементов 1 и 2 первого разряда заведен управляющий вход 7 для опроса. Выходы элементов 1 и 4 последнего разряда подключены к выходу 8сигнала «четности, а выходы элементов 2 и 3 этого разряда подключены к выходу 9сигнала «нечетности. На входы считывания всех элементов заведен тактовый вход 10 устройства. На фиг. 2 цифрой 11 обозначен другой тактовый вход устройства, а цифрой 12 - элемент коммутаций. Проверяемая информация подается по информационным входам 5 или 6, причем если данный разряд кода содержит «1, то по входу 5 будет записана «1 в элементы 2 и 4. Если же данный разряд кода содержит «О, то по входу 6 будет записана «1 в элементы 1 и 3. На вход 7 подается сигнал опроса. В зависимости от значения кода в первом разряде, появится сигнал на выходе элементов 1 или 2, который считает одну из пар эле.ментов следующего разряда. В считанной паре элементов выходной сигнал появится также на выходе только одного элемента и так далее. Таким образом выходной сигнал появляется на выходе только одного элемента каждого разряда и результирующий сигнал и проверяемом коде появляется также на одном из выходов 8 или 9, затем происходит очистка всех элементов. На фиг. 2 представлен пример реализации устройства, принимающего информацию только в прямом коде. Для этого все эмиттеры феррит-транзисторных эле.ментов соединены вместе и заведены на выход элемента коммутации 12. К входу элемента коммутации 12 подключен тактовый вход 10, а к входу подготовки элементов 13 и входу гашения элементов 2, 4 подключен тактовый вход 11 устройства. Вход 5 сигнала наличия «1 в данном разряде проверяемого кода, заведен на входы подготовки элементов 2 и 4, а также на входы гащения элементов 1 и 3. Остальные связи аналогичны связям схемы, приведенной на фиг. 1. В первом такте (вход 11) происходит постоянная запись «1 в элементы 1 и 3 и гашение инфор.мации в элементах 2 и 4, оставшейся от предыдущего цикла проверки. В следующем такте подается входная ннформация по тем входам 5 разрядов проверяемого кода, которые содержат «I и происходит подготовка эле.ментов 2 и 4 и гашение информации в элементах 1 и 3 соответствующих разрядов. В третьем такте на вход 7 подается сигнал опроса и открывается элемент коммутации 12 на время большее времени считывания всех элементов устройства. Эмиттеры феррит-транзисторных элементов получают через элем« нт 12 питание и происходит считывание одного из элементов каждого разряда в зависимости от значения проверяемого кода, аналогично, как описано для схемы, приведенной на фиг. 1. Таким образом, появление выходного сигнала на выходе 8 или выходе 9 определяется только количеством единиц в проверяемом коде (четное или нечетное) и не зависит от количества разрядов и параметров феррит-транзисторных элементов. Кроме того, в устройстве отсутствуют развязывающие диоды и не требуется специальных выходных элементов. Варианты построения устройства позволяют осуществлять прием информации как в парафазном, так и в прямом двоичном коде, и характеризуются высоким быстродействием.

Формула изобретения

Устройство для проверки кода на четность, содержащее в каждом разряде, кроме первого, четыре феррит-транзисторных элемента и два феррит-транзисторных элемента в первом разряде, причем информационные входы феррит-транзисторных элементов соединены с соответствующими информационными входами устройства, а первые входы считывания подключены к тактовому входу устройства, отличающееся тем, что, с целью упрощения и повыщения надежности, управляющий вход устройства соединен со вторыми входами считывания феррит-транзисторных элементов первого разряда, выходы которых подключены ко вторым входам считывания соответственно первого и второго, третьего и четвертого феррит-транзисторных элементов второго разряда, выходы первого и четвертого, выходы второго и третьего феррит-транзисторных элементов каждого предыдущего разряда, начиная со второго, объединены и подключены к объединенным вторым входам считывания соответственно первого и второго, третьего и четвертого феррит-транзисторных элементов каждого последующего разряда, объединенные выходы первого и четвертого, второго и третьего феррит-транзисторных элементов последнего разряда подключены соответственно к выходу сигнала четности и выходу сигнала нечетности устройства.

Источники информации, принятые во внимание при экспертизе

1.Путинцев Н. Д. Аппаратный контроль управляющих цифровых вычислительных мащин. «Советское радио, М., 1966, с. 70-73

2.Авторское свидетельство СССР № 159696, кл. G06 F 11/10, 1964.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ввода-вывода | 1980 |

|

SU896626A1 |

| Устройство для контроля информации | 1972 |

|

SU474824A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| Устройство для индикации | 1972 |

|

SU448467A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО КОДА В ОБРАТНЫЙ И ДОПОЛНИТЕЛЬНЫЙ | 1969 |

|

SU249044A1 |

| Устройство для адресования грузов установок непрерывного транспорта | 1978 |

|

SU716934A1 |

| Устройство для адресования подвижных объектов | 1977 |

|

SU676987A2 |

Авторы

Даты

1979-03-25—Публикация

1976-04-17—Подача