СП

NP

СО

Шиг.

31501043

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении универсальных и специализирован- 5 ньк-вычислительных устройств.

Целью изобретения является повышение быстродействия устройства.

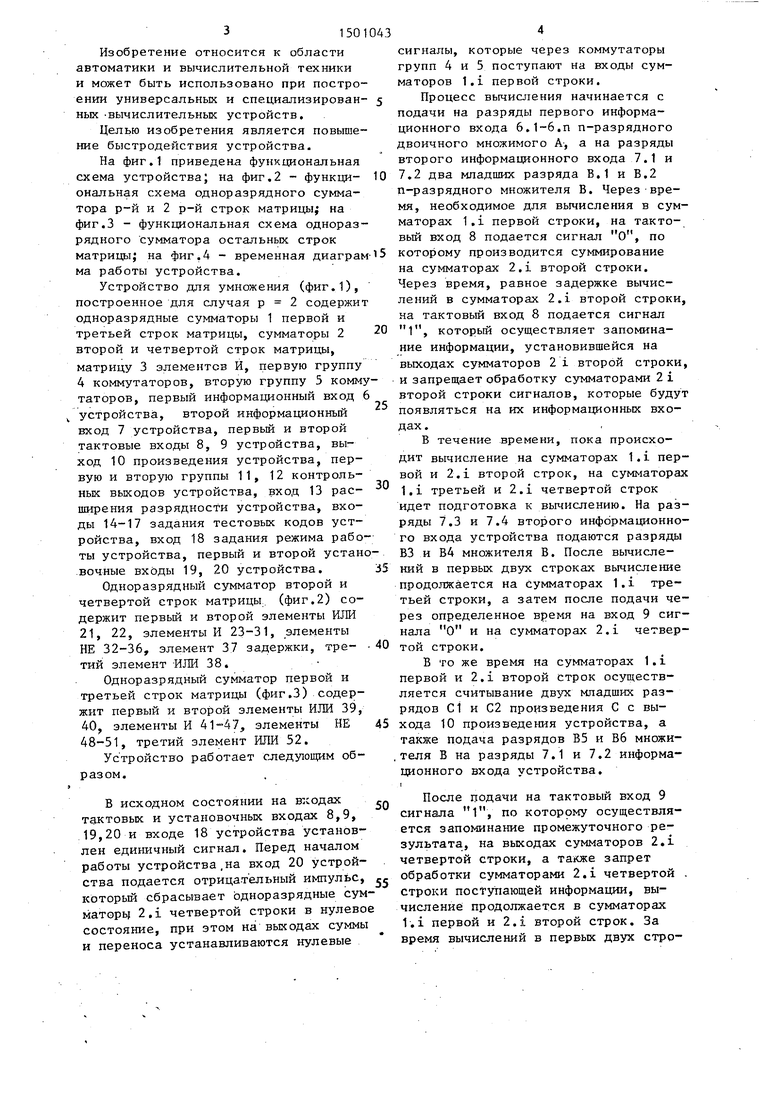

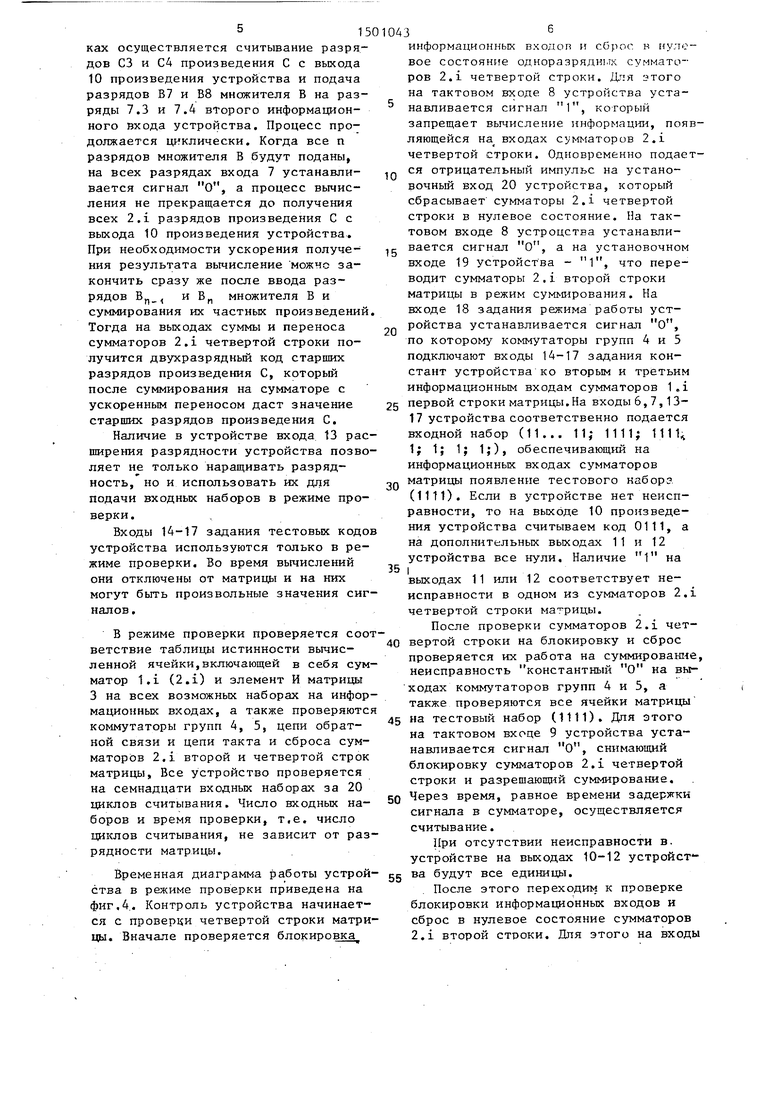

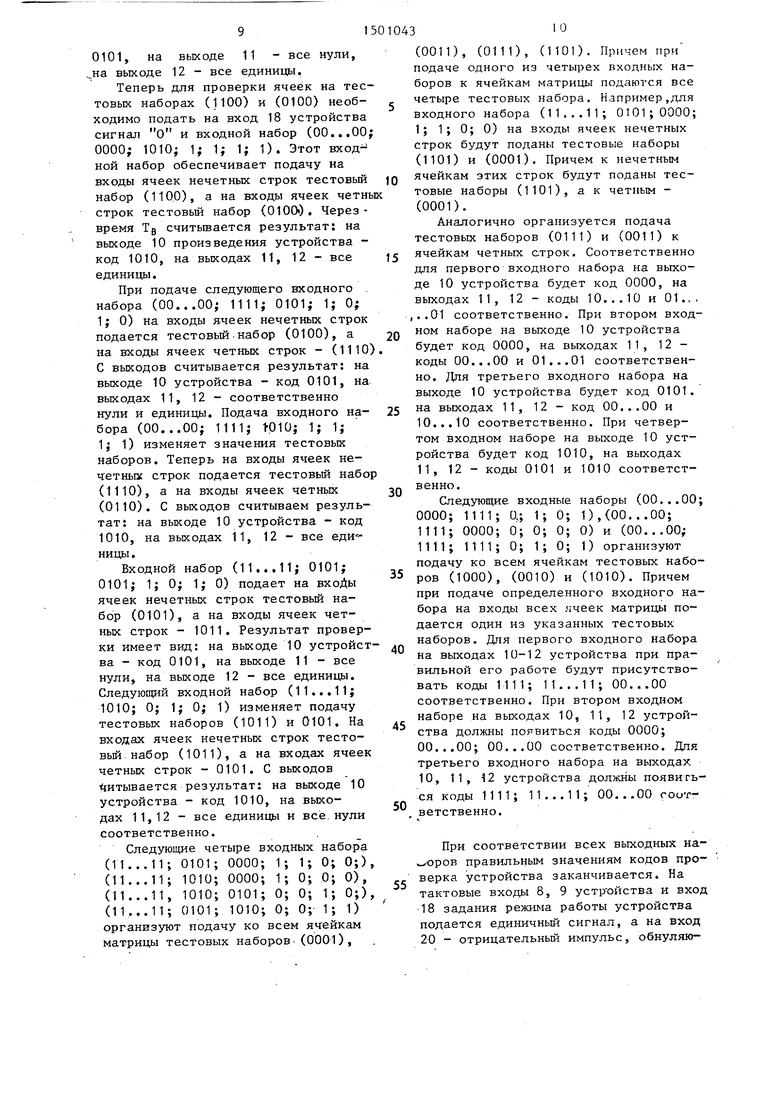

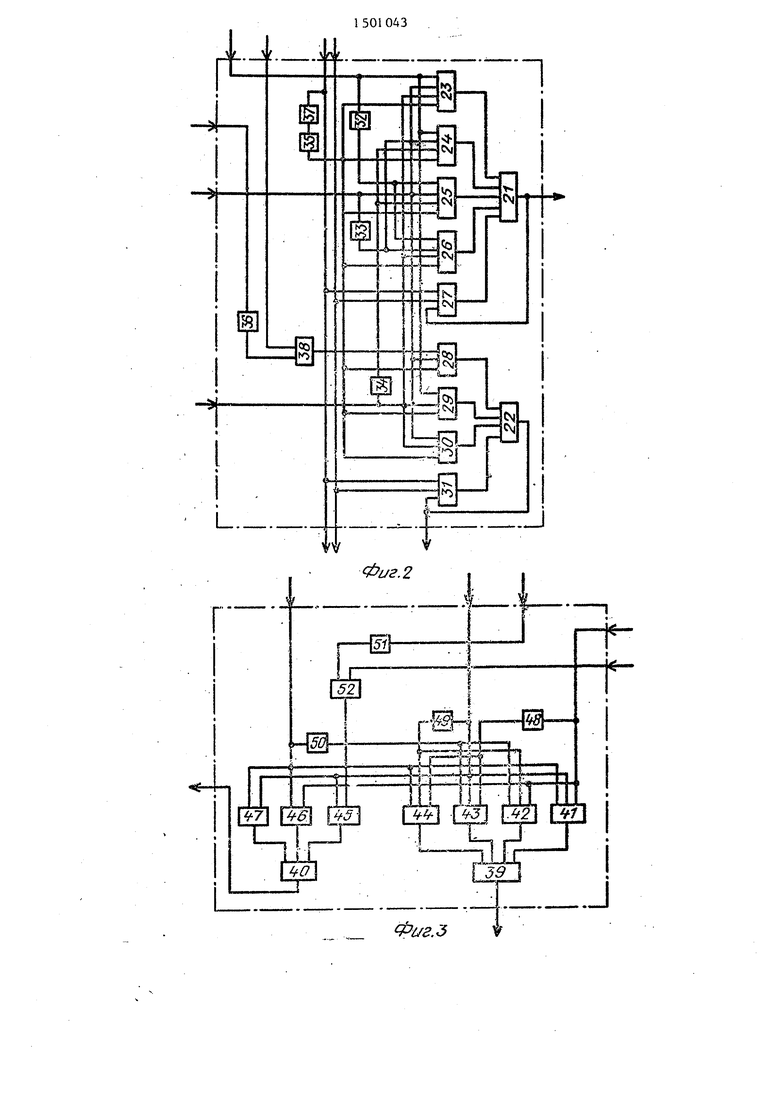

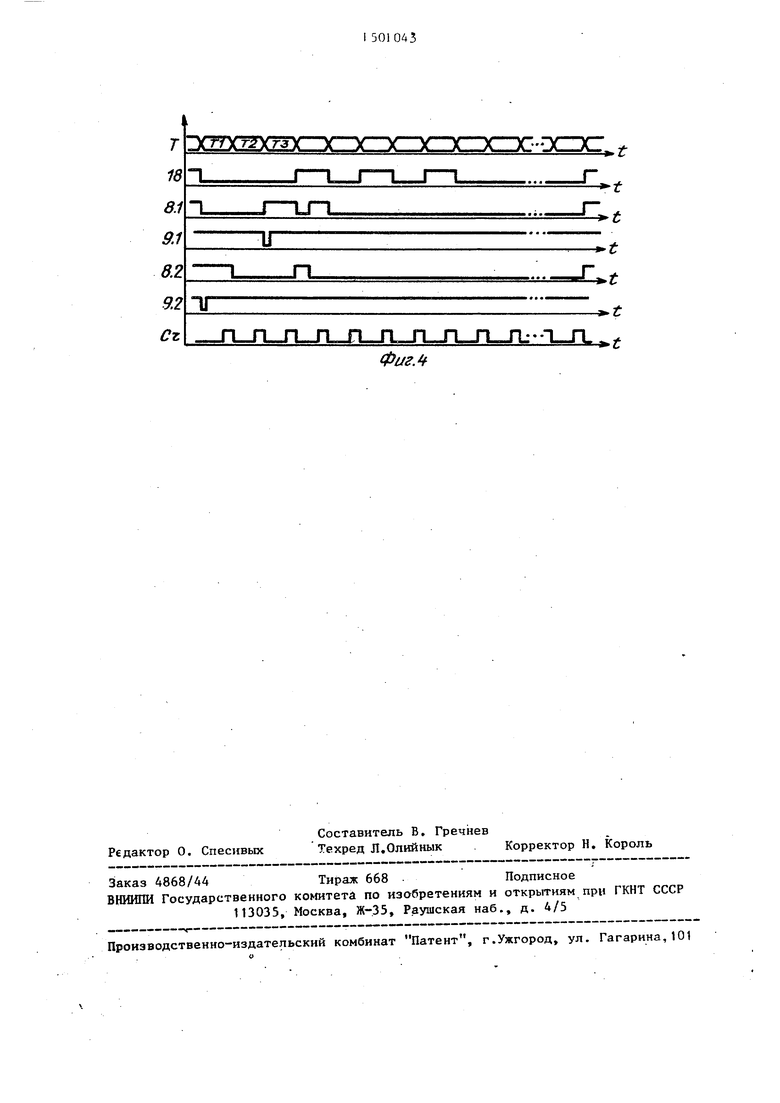

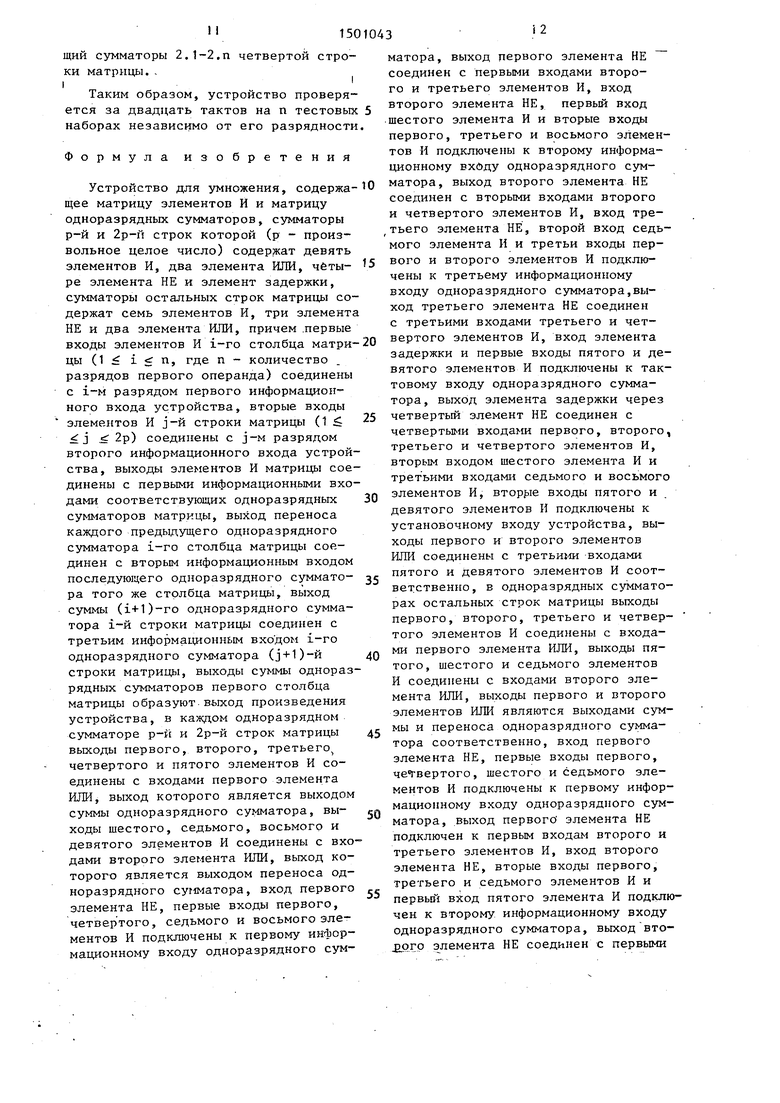

На фиг.1 приведена функциональная схема устройства; на фиг,2 - функци- 10 ональная схема одноразрядного сумматора р-й и 2 р-й строк матрицы; на фиг,3 - функциональная схема одноразрядного сумматора остальных строк матрицы; на фиг.4 - временная диаграм-15 ма работы устройства.

Устройство для умножения (фиг.1), построенное для случая р 2 содержит одноразрядные сумматоры 1 первой и третьей строк матрицы, сумматоры 2 второй и четвертой строк матрицы, матрицу 3 элементов И, первую группу 4 коммутаторов, вторую группу 5 коммутаторов, первый информационный вход 6 устройства, второй информационный вход 7 устройства, первый и второй тактовые входы 8, 9 устройства, выход 10 произведения устройства, первую и вторую группы 11, 12 контрольных выходов устройства, вход 13 расширения разрядности устройства, входы 14-17 задания тестовых кодов устройства, вход 18 задания режима работы устройства, первый и второй установочные входы 19, 20 устройства, 35

Одноразрядный сумматор второй и четвертой строк матрицы., (фиг,2) содержит первый и второй элементы ИЛИ 21, 22, элементы И 23-31, элементы НЕ 32-36, элемент 37 задержки, тре- 40 тий элемент -ИЛИ 38.

Одноразрядный сумматор первой и третьей строк матрицы (фиг,3) содержит первый и второй элементы ИЛИ 39, 40, элементы И 41-47, элементы НЕ 45 48-51, третий элемент ИЛИ 52,

Устройство работает следующим образом.

25

В исходном состоянии на входах Q тактовых и установочных входах 8,9, 19,20 и входе 18 устройства установлен едиьшчный сигнал. Перед началом работы устройства,на вход 20 устройства подается отрицат ельный импульс, который сбрасывает одноразрядные сум- маторц 2,1 четвертой строки в нулевое состояние, при этом на выходах суммы и переноса устанавливаются нулевые

5

0 5

5

0

5

5

Q

сигналы, которые через коммутаторы групп 4 и 5 поступают на входы сумматоров 1,1 первой строки.

Процесс вычисления начинается с подачи на разряды первого информационного входа 6.,п п-разрядного двоичного множимого А-, а на разряды второго информационного входа 7,1 и 7,2 два младших разряда В,1 и В,2 п-разрядного множителя В. Через-время, необходимое для вычисления в сумматорах 1,1 первой строки, на тактовый вход 8 подается сигнал О, по которому производится суммирование на сумматорах 2.1 второй строки. Через время, равное задержке вычислений в сумматорах 2,1 второй строки, на тактовый вход 8 подается сигнал 1, который осуществляет запоминание информации, установившейся на выходах сумматоров 21 второй строки, и запрещает обработку сумматорами 2 i второй строки сигналов, которые будут появляться на их информационных входах .

В течение времени, пока происходит вычисление на сумматорах 1.1 первой и 2.1 второй строк, на сумматорах 1,1 третьей и 2,1 четвертой строк идет подготовка к вычислению. На разряды 7,3 и 7,4 второго информационного входа устройства подаются разряды ВЗ и В4 множителя В. После вычислений в первых двух строках вычисление продолжается на сумматорах 1.1 третьей строки, а затем после подачи через определенное время на вход 9 сигнала О и на сумматорах 2.1 четвертой строки,

В то же время на сумматорах 1,1 первой и 2,1 второй строк осуществляется считывание двух младших разрядов С1 и С2 произведения С с выхода 10 произведения устройства, а также подача разрядов В5 и Вб множителя В на разряды 7,1 и 7,2 информационного входа устройства, I

После подачи на тактовый вход 9 сигнала 1, по которому осуществляется запоминание промежуточного результата, на выходах сумматоров 2,1 четвертой строки, а также запрет обработки сумматорами 2.1 четвертой . строки постутшющей информации, вычисление продолжается в сумматорах 1,1 первой и 2,1 второй строк. За время вычислений в первых двух стро

15

ках осуществляется считывание разрядов СЗ и С4 произведения С с выхода 10 произведения устройства и подача разрядов В7 и В8 множителя В на разряды 7.3 и 7.4 второго информационного входа устройства. Процесс продолжается циклически. Когда все п разрядов множителя В будут поданы, на всех разрядах входа 7 устанавливается сигнал О, а процесс вычисления не прекращается до получения всех 2.1 разрядов произведения С с выхода 10 произведения устройства. При необходимости ускорения получения результата вычисление можно закончить сразу же после ввода разрядов Ъ и В„ множителя В и суммирования их частньк произведений. Тогда на выходах суммы и переноса сумматоров 2.1 четвертой строки получится двухразрядный код старших разрядов произведения С, который после суммирования на сумматоре с ускоренным переносом даст значение старших разрядов произведения С.

Наличие в устройстве входа 13 расширения разрядности устройства позволяет не только наращивать разрядность, но и использовать их для подачи входных наборов в режиме проверки.

Входы 14-17 задания тестовых кодов устройства используются только в режиме проверки. Во время вычислений они отключены от матрицы и на них могут быть произвольные значения сигналов .

В режиме проверки проверяется соответствие таблицы истинности вычисленной ячейки,включающей в себя сумматор 1.1 (2.1) и элемент И матрицы 3 на всех возможных наборах на информационных входах, а также проверяются коммутаторы групп 4, 5, цепи обратной связи и цепи такта и сброса сумматоров 2.1 второй и четвертой строк матрицы. Все устройство проверяется на семнадцати входных наборах за 20 циклов считывания. Число входных наборов и время проверки, т.е. число циклов считывания, не зависит от разрядности матрицы.

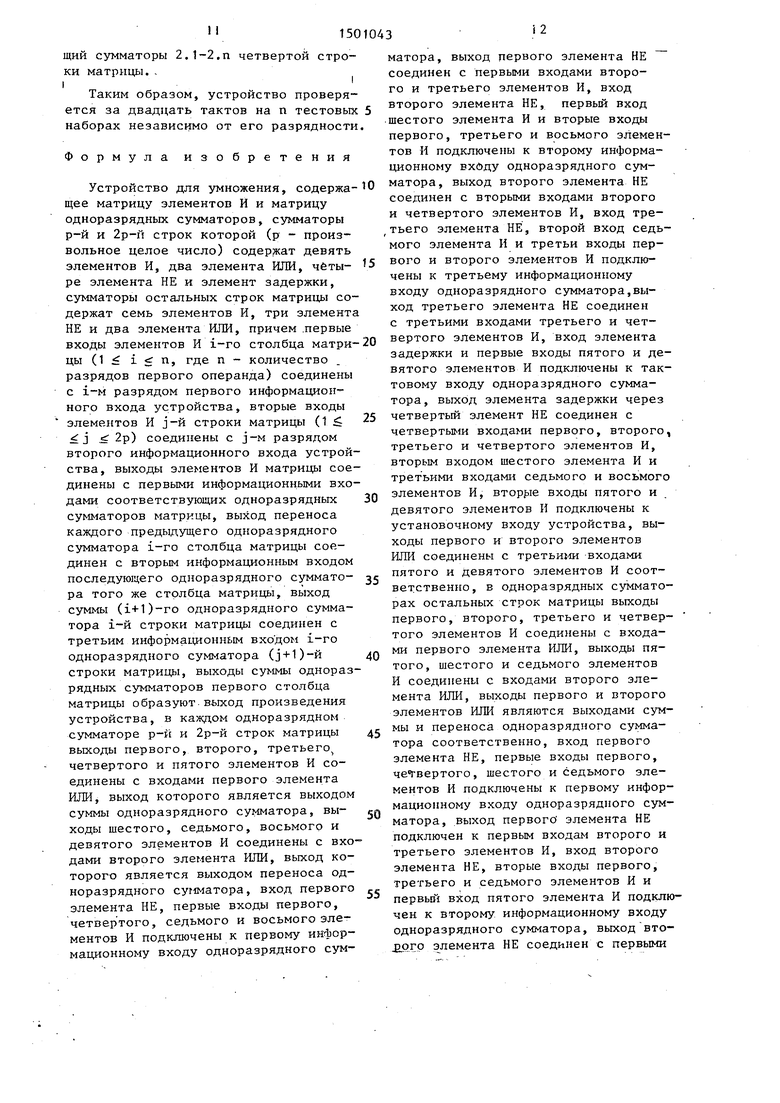

Временная диаграмма работы устройства в режиме проверки приведена на фиг.4.. Контроль устройства начинается с провер1 и четвертой строки матрицы. Вначале проверяется блокировка

10436

информационных входоп и сброс в tfyjie- вое состояние одноразрядных сумматоров 2.1 четвертой строки. этого на тактовом входе 8 устройства устанавливается сигнал 1

который

0

запрещает вычисление информации, появляющейся на входах сумматоров 2.1 четвертой строки. Одновременно подает- ся отрицательный импульс на установочный вход 20 устройства, который сбрасывает сум 1аторы 2.1 четвертой строки в нулевое состояние. На тактовом входе 8 устроцства устанавлиg вается сигнал О, а на установочном входе 19 устройства - 1, что переводит сумматоры 2.1 второй строки матрицы в режим суммирования. На входе 18 задания режима работы уст- ройства устанавливается сигнал О, по которому коммутаторы групп 4 и 5 подключают входы 14-17 задания констант устройства ко вторым и третьим информационным входам сумматоров 1,1

5 первой строки матрицы. На входы 6,7,13- 17 устройства соответственно подается входной набор (11... 11; 1111; 1111 1; 1; 1; 1|), обеспечивающий на информационных входах сумматоров матрицы появление тестового набора (1111). Если в устройстве нет неисправности, то на выходе 10 произведения устройства считываем код 0111, а на дополнительных выходах 11 и 12

устройства все нули. Наличие 1 на

5 I

выходах 11 или 12 соответствует неисправности в одном из сумматоров 2.1 четвертой строки матрицы.

После проверки сумматоров 2.1 чет0 вертой строки на блокировку и сброс проверяется их работа на суммирование, неисправность константный О на выходах коммутаторов групп 4 и 5, а также проверяются все ячейки матрицы

5 на тестовый набор (1111). Дпя этого на тактовом входе 9 устройства устанавливается сигнал о, снимающий блокировку сумматоров 2.1 четвертой строки и разрешающий суммирование,

0 Через время, равное времени задержки сигнала в сумматоре, осуществляется считывание.

При отсутствии неисправности в. устройстве на выходах 10-12 устройст 5 ва будут все единицы.

После этого переходим к проверке блокировки информационных входов и сброс в нулевое состояние сумматоров 2.1 второй строки. Для этого на входы

6, 7, 13-17 устройства подается входной набор (11...11;1100;1100;1;1 1;1;). На тактовый вход 8 устройства подается сигнал 1,блокирующий информационные входы сумматоров 2.1 второй строки, а на установочный вход 19 устройства подается отрицательный импульс, который сбрасывает сумматоры 2.1 второй строки в нулевое состояние. Через время, равное времени вычислений в двух строках, производится считывание выходной информации На выходах 11 и 12 устройства будут все нули, а на выходе 10 произведения устройства - код 0001.

После проверки сумматоров 2.1 второй строки необходимо проверить цепи обратной связи на обрыв,,, переключение коммутаторов групп 4 и 5 на обратную связь и неисправности типа константная 1 на выходах коммута:торов групп 4 и 5. Одновременно будут проверяться все ячейки матрицы на тестовом наборе 0000. Входной набор (00...00; 0000; 0000; 1;. 1; 1; 1;) подается на входе 6, 7,13-17 устройства С выходов сумм и переносов сумматоров 2.1 четвертой строки на первые входы коммутаторов групп 4 и 5 по обратным связям поступают сигналы О На тактовый вход 9 устройства подается сигнал 1, по которому производится запоминание информации в сумматорах 2о1 .четвертой строки и блокировка их информационньк входов. На вход 18 задания режима работы устройства подается сигнал 1, по которому происходит подключение первых входов коммутаторов к информационным входам сумматоров 1.1 первой строки. На тактовый вход 8 устройства подается сигнал О, который переводит сумматоры 2.1 второй строки в .режим суммирования. Через время, равное задержке распространения сиг налов через коммутаторы групп 4 и 5 и сумматоры первых двух строк, на тактовый вход 8 устройства подается сигнал 1. Происходит запоминание результата вычислений и блокировка информационных входов в сумматорах. 2.1 второй строки матрицы. На тактовый вход 9 устройства подается сигнал О, снимающй блокировку информационных входов сумматоров 2.1 четвертой строки и разрешающий суммирование. Через время, равное мени вычисл-ений в сумматорах, пройз

10

15

20

25

30

35

40

45

0

5

водится считывание результата с выходов устройства. На выходах 10-12 устройства все нули.

Так как проверка сумматоров 2.о второй и четвертой строк матрицы на блокировку и сброс проведена, то при дальнейшем контроле для сокращения времени проверки эти сумматоры уста- навливаются в режиме суммирования. Для этого на.тактовые входы 8,9 устройства подается сигнал о, а на установочные входы 19, 20 устройства 1.

Для проверки ячеек матрицы на тес- вьш набор (1001) подается входной набор (11...11; 0000; 1111; 0; 1; 0; 1;). Через время Tj, равное времени задержки в коммутаторах групп 4, 5 плюс время вычислений во всех сумматорах матрицы, считывается результат. На выходе 10 произведения устройства - код 1111, на выходе устройства - 11... 11, на выходе 12 устройства - 00.,00. На следующем шаге проводится проверка обратных связей на замыкание линий. Для этого ис- пйльзуются результаты предшествующей проварки, так как на выходах сумм сумматоров 2,1 четвертой строки все единицы, а на выходах переносов - все нули. Подав на вход 18 задания режима работы устройства сигнал 1, включаем обратную связь. Информация с выходов сумм и переносов сумматоров 2с,1 четвертой строки поступает на информационные входы сумматоров 1.1 первой строки Через время Тц считывается результат, который, если нет неисправностей, равен предыдущему, т.е. на выходах 10 и 11 устройства все единицы, а на выходе 1,2 устройства - все нули.

Для проверки замыканий обратных связей на инверсных сигналах подается входной набор (OO...OOJ 0000; 0101; 1; 0; 1; 1 ), с помощью которого на первом шаге проверяются все ячейки матрицы на тестовых наборах, (0100) и (1100), построчно, т.е. к ячейкам нечетных строк подается набор (0100), а к ячейкам четных строк матрицы набор (1100). Для подачи входного набора на матрицу на вход 18 устройства подается сигнал О. Через время Т считывается результат. На выходе 10 произведения устройства - код

0101, на выходе 11 - все нули, на выходе 12 - все единицы.

Теперь для проверки ячеек на тестовых наборах (1100) и (0100) необходимо подать на вход 18 устройства сигнал о и входной набор (00...00 0000; 1010; 1; 1; 1; 1). Этот входной набор обеспечивает подачу на входы ячеек нечетных строк тестовый набор (1100), а на входы ячеек четн строк тестовый набор (01000. Через- время Тд считьтается результат: на выходе 10 произведения устройства - код 1010, на выходах 11, 12 - все единицы.

При подаче следующего входного . набора (00...00; 1111; 0101; 1; 0; 1; 0) на входы ячеек нечетных строк подается тестовый.набор (0100), а на входы ячеек четных строк - (1110 С выходов считывается результат: на выходе 10 устройства - код 0101, на выходах 11, 12 - соответственно нули и единицы. Подача входного набора (00...00; 1111; tOlO; 1; 1; 1; 1) изменяет значения тестовых наборов. Теперь на входы ячеек не- чгетных строк подается тестовый набо (1110), а на входы ячеек четных (0110). С выходов считываем результат: на выходе 10 устройства - код 1010, на выходах 11, 12 - все еди-- ницы.

Входной набор (11..,11; 0101; 0101; 1; 0; 1; 0) подает на вхоДы ячеек нечетных строк тестовый набор (0101), а на входы ячеек четных строк - 1011. Результат проверки имеет вид: на выходе 10 устройства - код 0101, на выходе 11 - все нули, на выходе 12 - все единицы. Следующий входной набор (11... 11; 1010; 0; 1; 0; 1) изменяет подачу тестовых наборов (1011) и 0101. На входах ячеек нечетных строк тесто- вьй набор (1011), а на входах ячеек четных строк - 0101. С выходов 1итывается результат: на выходе 10 устройства - код 1010, на выходах 11,12 - все единицы и все. нули соответственно.

Следующие четыре входных набора (11... 11; 0101; 0000; 1; 1; 0; 0;), (11...11; 1010; 0000; 1; 0; 0; О), (11...11, 1010; 0101; 0; 0; 1; 0;), (11...11; 0101; 1010; 0; 0; 1; О организуют подачу ко всем яч:ейкам матрицы тестовых наборов(0001),

х

.

10

15

20

25

50104310

(0011), (0111), (1101), Причем при подаче одного из четырех входных наборов к ячейкам матрицы подаются все четыре тестовых набора. Например,для входного набора (11,,.11; 0101; 0000; 1; 1; 0; 0) на входы ячеек нечетных строк будут поданы тестовые наборы (1101) и (0001), Причем к нечетным ячейкам этих строк будут поданы тестовые наборы (1101), а к четным - (0001),

Аналогично организуется подача тестовых наборов (0111) и (0011) к ячейкам четных строк. Соответственно для первого входного набора на выходе 10 устройства будет код 0000, на выходах 11, 12 - коды 10.,,10 и 01.,, ,,,01 соответственно. При втором входном наборе на выходе 10 устройства будет код 0000, на выходах 11, 12 - коды 00..,00 и 01.,,01 соответственно. Для третьего входного набора на выходе 10 устройства будет код 0101, на выходах 11, 12 - код 00,.,00 и 10...10 соответственно. При четвертом входном наборе на выходе 10 устройства будет код 1010, на выходах 11, 12 - коды 0101 и 1010 соответственно.

Следующие входные наборы (00,..00; 0000; 1111; О,; 1; 0; 1),00,,.00; 1111; 0000; 0; 0; 0; 0) и (00.,,00; 1111; 1111; 0; 1; 0; 1) организуют подачу ко всем ячейкам тестовых наборов (1000), (0010) и (1010), Причем при подаче определенного входного набора на входы всех .ччеек матрицы дается один из указанных тестовых наборов. Для первого входного набора на выходах 10-12 устройства при правильной его работе будут присутствовать коды 1111; 11,,,11; 00,..00 соответственно. При втором входном наборе на выходах 10, 11, 12 устройства должны появиться коды 0000; 00,,.00; 00,.,00 соответственно. Для третьего входного набора на выходах 10, 11, 12 устройства должны появиться коды 1111; 11,.,11; 00,..00 соответственно.

30

35

40

45

50

При соответствии всех выходных на- оров правильным значениям кодов проверка устройства заканчивается. На тактовые входы 8, 9 устр ойства и вход 18 задания режима работы устройства подается единичный сигнал, а на вход 20 - отрицательный импульс, обнуляю-

I

щий сумматоры 2.1-2.П четвертой строки матрицы.

Таким образом, устройство проверяется за двадцать тактов на п тестовых 5 наборах независимо от его разрядности.

Формула изобретения

матора, выход первого элемента НЕ соединен с первыми входами второго и третьего элементов И, вход второго элемента НЕ, первый вход шестого элемента И и вторые входы первого, третьего и восьмого элементов И подключены к второму информационному вхйду одноразрядного сум

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для моделирования сетевых графов | 1987 |

|

SU1462346A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении универсальных и специализированных вычислительных устройств. Цель изобретения - повышение быстродействия устройства. Устройство умножения, построенное для случая P =2, содержит одноразрядные сумматоры 1 первой и третьей строк матрицы, сумматоры 2 второй и четвертой строк матрицы, матрицу 3 элементов И, первую группу коммутаторов 4, вторую группу коммутаторов 5. Введение двух групп коммутаторов 4 и 5 позволяет разрывать цепи обратной связи между выходами переноса и результата сумматоров 2.I последней строки матрицы и информационными входами сумматоров 1.I первой строки матрицы по сигналу, поступающему на вход 18 задания режима работы устройства. С помощью подачи тестовых сигналов на входы 14-17 удается осуществить полную проверку устройства за двадцать тактов с помощью семнадцати тестовых наборов. 4 ил.

Устройство для умножения, содержа-1О матора, выход второго элемента НЕ

соединен с вторыми входами второго и четвертого элементов И, вход тре тьего элемента НЕ, второй вход сед мого элемента И и третьи входы пер

щее матрицу элементов И и матрицу одноразрядных сумматоров, сумматоры р-й и 2р-й строк которой (р - произвольное целое число) содержат девять

соединен с вторыми входами второго и четвертого элементов И, вход тре тьего элемента НЕ, второй вход сед мого элемента И и третьи входы пер

элементов И, два элемента ИЛИ, четы- 5 вого и второго элементов И подключены к третьему информационному входу одноразрядного сумматора,выход третьего элемента НЕ соединен с третьими входами третьего и четре элемента НЕ и элемент задержки, сумматоры остальных строк матрицы содержат семь элементов И, три элемента НЕ и два элемента ИЛИ, причем .первые

чены к третьему информационному входу одноразрядного сумматора,выход третьего элемента НЕ соединен с третьими входами третьего и четвходы элементов И i-ro столбца матри-20 вертого элементов И, вход элемента

цы (1 i п, где п - количество разрядов первого операнда) соединены с i-M разрядом первого информационного входа устройства, вторые входы элементов И j-й строки матрицы (1 j 2р) соединены с j-м разрядом второго информационного входа устройства, выходы элементов И матрицы соединены с первыми информационными входами соответствующих одноразрядных 30 сумматоров матрицы, выход переноса каждого предыдущего одноразрядного сумматора i-ro столбца матрицы соединен с вторым информационным входом последующего одноразрядного суммато- 5 ра того же столбца матрицы, выход суммы (i+1)-ro одноразрядного сумматора i-й строки матрицы соединен с третьим информационным входом i-ro одноразрядного сумматора (з+1)-й 40 строки матрицы, выходы суммы одноразрядных сумматоров первого столбца матрицы образуют.выход произведения устройства, в каждом одноразрядном сумматоре р-й и 2р-й строк матрицы 45 выходы первого, второго, третьего четвертого и пятого элементов И соединены с входами первого элемента ИЛИ, выход которого является выходом суммы одноразрядного сумматора, вы- jg ходы шестого, седьмого, восьмого и девятого элементов И соединены с входами второго элемента ИЛИ, выход которого является выходом переноса одноразрядного сумматора, вход первого элемента НЕ, первые входы первого, четвертого, седьмого и восьмого элементов И подключены к первому информационному входу одноразрядного сумзадержки и первые входы пятого и де вятого элементов И подключены к так товому входу одноразрядного сумматора , выход элемента задержки через четвертый элемент НЕ соединен с четвертьп-ш входами первого, второго третьего и четвертого элементов И, вторым входом шестого элемента И и третьими входами седьмого и восьмог элементов И, BTopfiie входы пятого и девятого элементов И подключены к установочному входу устройства, выходы первого и второго элементов ИЛИ соединены с третьи1«1 входами пятого и девятого элементов И соответственно , в одноразрядных суммато рах остальных строк матрицы выходы первого, второго, третьего и четвер того элементов И соединены с входами первого элемента ИЛИ, выходы пятого, шестого и седьмого элементов И соединены с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ являются выходами сум мы и переноса одноразрядного сумматора соответственно, вход первого элемента НЕ, первые входы первого, четвертого, шестого и седьмого элементов И подключены к первому инфор мационному входу одноразрядного сум матора, выход первого элемента НЕ подключен к первым входам второго и третьего элементов И, вход второго элемента НЕ, вторые входы первого, третьего и седьмого элементов И и первьй вход пятого элемента И подкл чен к второму информационному входу одноразрядного сумматора, выход вто .ргр элемента НЕ соединен с первыми

матора, выход второго элемента НЕ

соединен с вторыми входами второго и четвертого элементов И, вход третьего элемента НЕ, второй вход седьмого элемента И и третьи входы первого и второго элементов И подключены к третьему информационному входу одноразрядного сумматора,выход третьего элемента НЕ соединен с третьими входами третьего и четзадержки и первые входы пятого и девятого элементов И подключены к тактовому входу одноразрядного сумматора , выход элемента задержки через четвертый элемент НЕ соединен с четвертьп-ш входами первого, второго третьего и четвертого элементов И, вторым входом шестого элемента И и третьими входами седьмого и восьмого элементов И, BTopfiie входы пятого и девятого элементов И подключены к установочному входу устройства, выходы первого и второго элементов ИЛИ соединены с третьи1«1 входами пятого и девятого элементов И соответственно , в одноразрядных сумматорах остальных строк матрицы выходы первого, второго, третьего и четвертого элементов И соединены с входами первого элемента ИЛИ, выходы пятого, шестого и седьмого элементов И соединены с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ являются выходами суммы и переноса одноразрядного сумматора соответственно, вход первого элемента НЕ, первые входы первого, четвертого, шестого и седьмого элементов И подключены к первому информационному входу одноразрядного сумматора, выход первого элемента НЕ подключен к первым входам второго и третьего элементов И, вход второго элемента НЕ, вторые входы первого, третьего и седьмого элементов И и первьй вход пятого элемента И подключен к второму информационному входу одноразрядного сумматора, выход вто- .ргр элемента НЕ соединен с первыми

входами второго и четвертого элементов И, вход третьего элемента НЕ, Третьи входы первого и второго элементов И и второй вход шестого элемента И подключены к третьему информационному входу одноразрядного сумматора, выход третьего элемента НЕ соединен с третьими входами третьего и четвертого элементов И, тактовые входы одноразрядных сумматоров р-й и 2р-й строк матрицы подключены соответственно к первому и второму тактовым входам устройства, установочные входы одноразрядных сумматоров р-й и 2р-й строк матрицы подключены соответственно к первому и второму установочным входам устройства, третьи И}1формационные входы одноразрядных сумматоров п-го столбца матрицы образуют вход расширения разрядности устройства, выходы суммы одноразрядных сумматоров 2р-й строки матрицы, кроме первого, образуют первую группу контрольных выходов устройства, выходы переносов всех одноразрядных сумматоров 2р-й строки матрицы образуют вторую группу контрольных выходов устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены две группы коммутаторов, в каждый одноразрядньй сумматор р-й и 2р-й строк матрицы введены пятый элемент НЕ и третий элемент ИЛИ, в одноразрядные сумматоры остальных строк матрицы введены четвертый элемент НЕ и третий элемент ИЛИ, причем выходы переноса одноразрядных сумматоров 2р-й строки матрицы соединены с первыми информационными входами соответствующих коммутаторов первой группы, выходы которых соединены с вторыми информационными входами соответствующих одноразрядньк сумматоров первой строки матрицы, выходы cyMi|O.i 1-х одноразрядных сумматоров 2р-й строки матрицы () соединены с первыми информационными входами соответствующих комг-{утаторов второй

группы, КЫХО;Ц,1 которых С.ОСДИНС.ИЬ г.

третьими информационными входами (1-1)-х одноразрядных сумматоров пср- вой строки матрицы, вторые информационные входы нечетных коммутаторов первой группы подключен к первому входу задания тестовых кодов устройства, вторые информационные входы

0 четных коммутаторов первой группы подключены к второму входу задания тестовых кодов устройства, вторые информационные входы нечетных коммутаторов второй группы и вторые ин5 формационные входь четных коммутаторов второй группы подключены соответственно к третьему и четвертому входам задания констант устройства, управляющие входы комь1утаторов пер0 вой и второй групп подключены к входу задания режима работы устройства, четвертые информационные входы всех одноразрядных сумматоров каждого i-ro столбца матрицы соединены с i-м

5 разрядом первого информационного

входа устройства, пятые информационные входы всех одноразрядных сумматоров каждой j-й строки матрицы соединены с J-M разрядом второго инп формационного входа устройства, в каждом одноразрядном сумматоре р-й и 2р-й строк матрицы вход пятого. элемента НЕ и первый вход третьего элемента ИЛИ подключены соответственно к четвертому и пятому информа ционным входам одноразрядного сумматора, выход пятого элемента НЕ соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с третьим входом шестого элемента И, в остальных строках матрицы в каждом одноразрядном сумматоре вход четвертого элемента НЕ и первый вход третьего элемента ИЛИ подключены соответственно к четвертому и пятому инфор- мационным входам одноразрядного сумматора, выход четвертого элемента НЕ соединен с вторьм входом третьего элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И.

0

5

Г 18 8.1 9.1 82 9.2 Сг

УТТУтЗУгзХ

U

п

-t

Фиг.

| Множительное устройство | 1979 |

|

SU817705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-07-30—Подача