1

Изобретение относится к устройствам адресования грузов, моделирующим участки установок непрерывного транспорта, и может быть использовано в устройствах автоматики, где требуется накопление, сдвиг и обработка . кодовой информации.

Известно устройство для адресова1шя грузов установок непрерывного транспорта, состоящее из матрицы памяти, реверсивного распределителя им 1ульсов, элемента контроля продвижения информации, командной схемы и датчиков подвижного объекта. Выходы элементов распределителя импульсов заведены на считывающие входы ячеек матрицы памяти, а его входы управления соединены с выходам кома1здной схемы. На входы командной схемы заведены выходы датчиков подвижного объекта и элемента контроля продвижения адресной информации, а входы последнего соединены с выходами матрицы памяти 1.

. В матрице памяти известного устройства храншся адресная информация всех грузов, находящихся на корггролируемом участке. Однако оператор не имеет доступа к этой

информации, так как любое вмешательство щтводит к ее сдвигу, т.е. к нарушению работы устройства адресования. Вместе с тем, доступ к информации необходим для осуществления (при необходимости) ее коррекции и для получения информационных данных о грузопотоке: количестве находящихся на участке грузов с заданным адресным кодом, порядке расположения грузов с различными адресными .

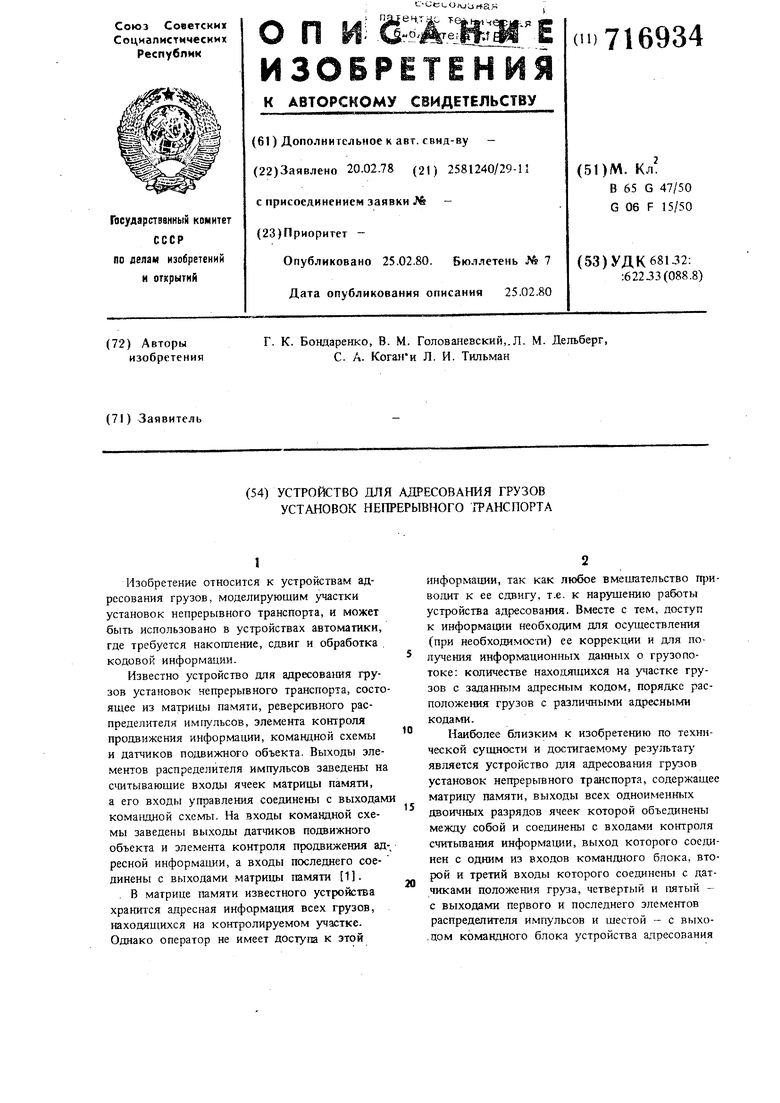

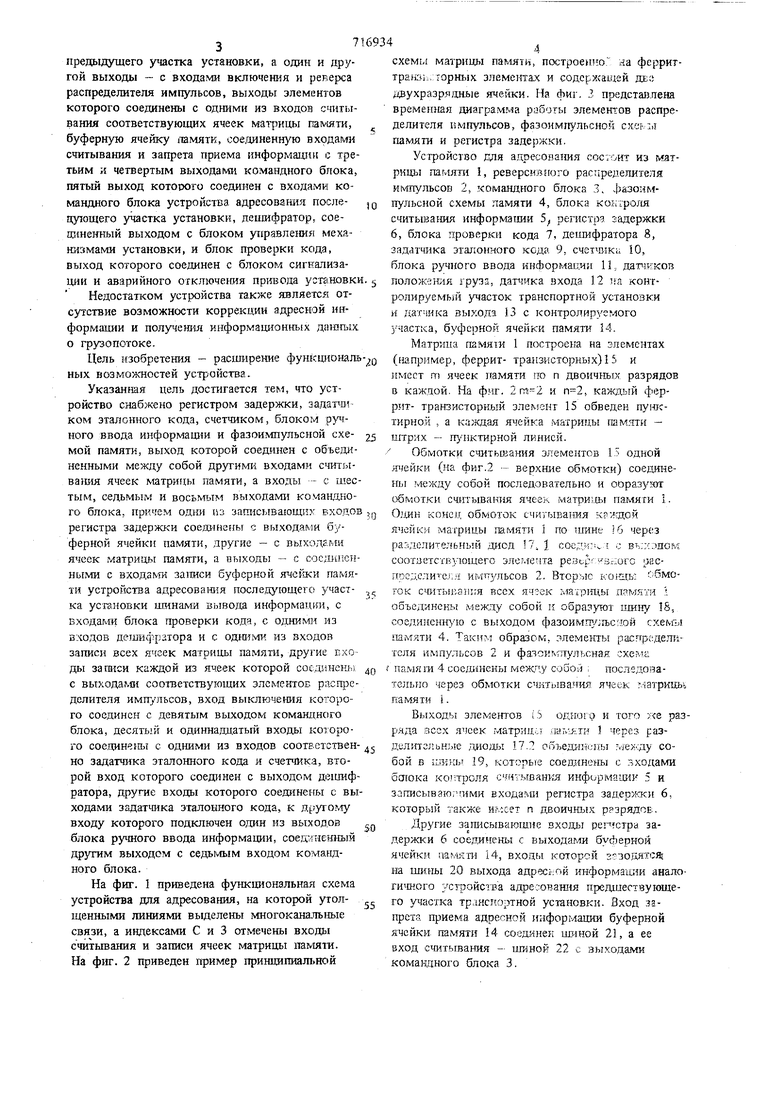

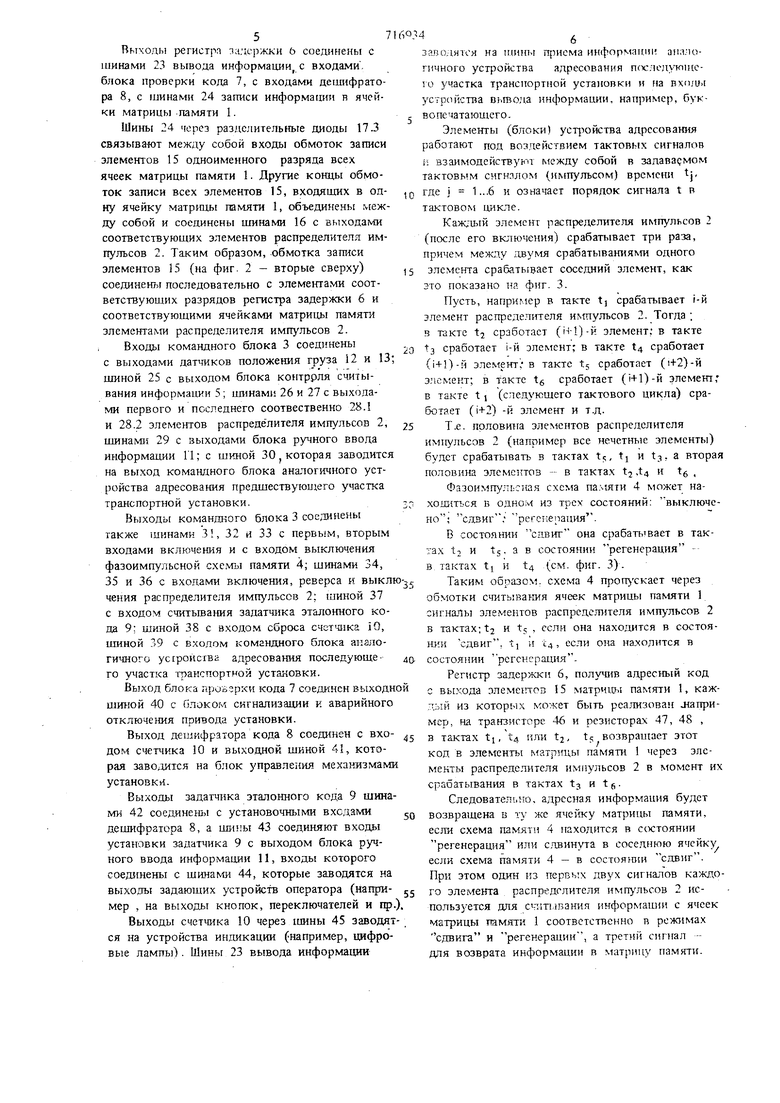

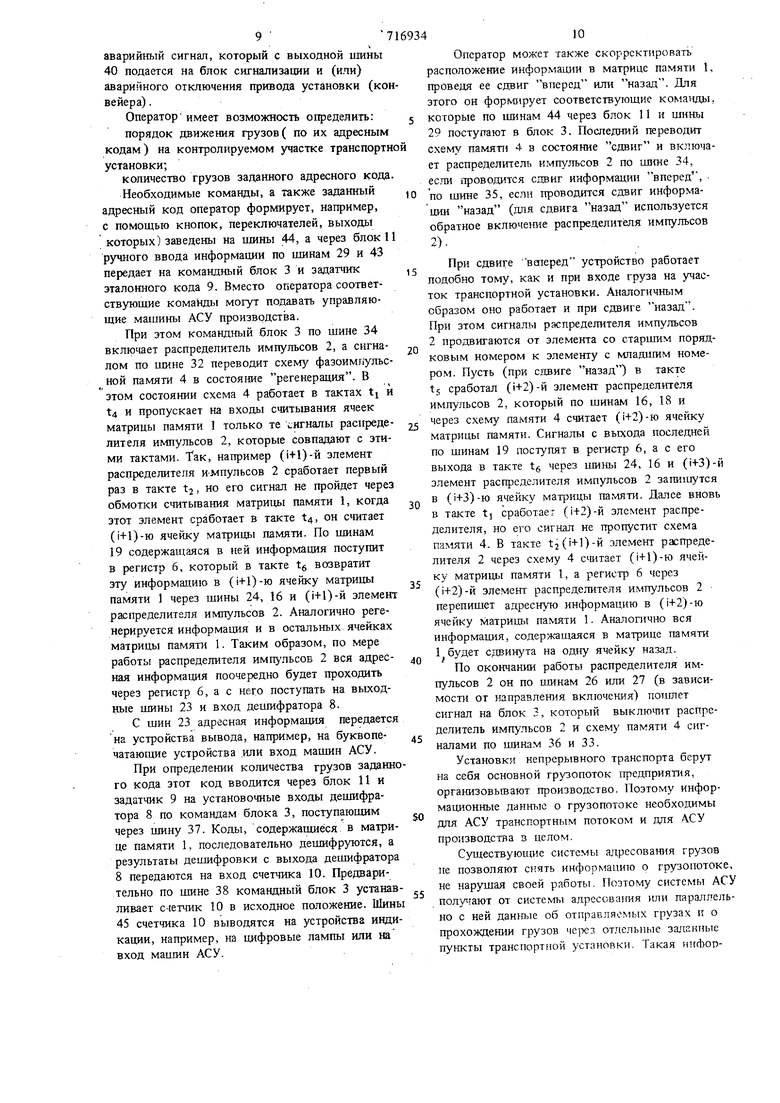

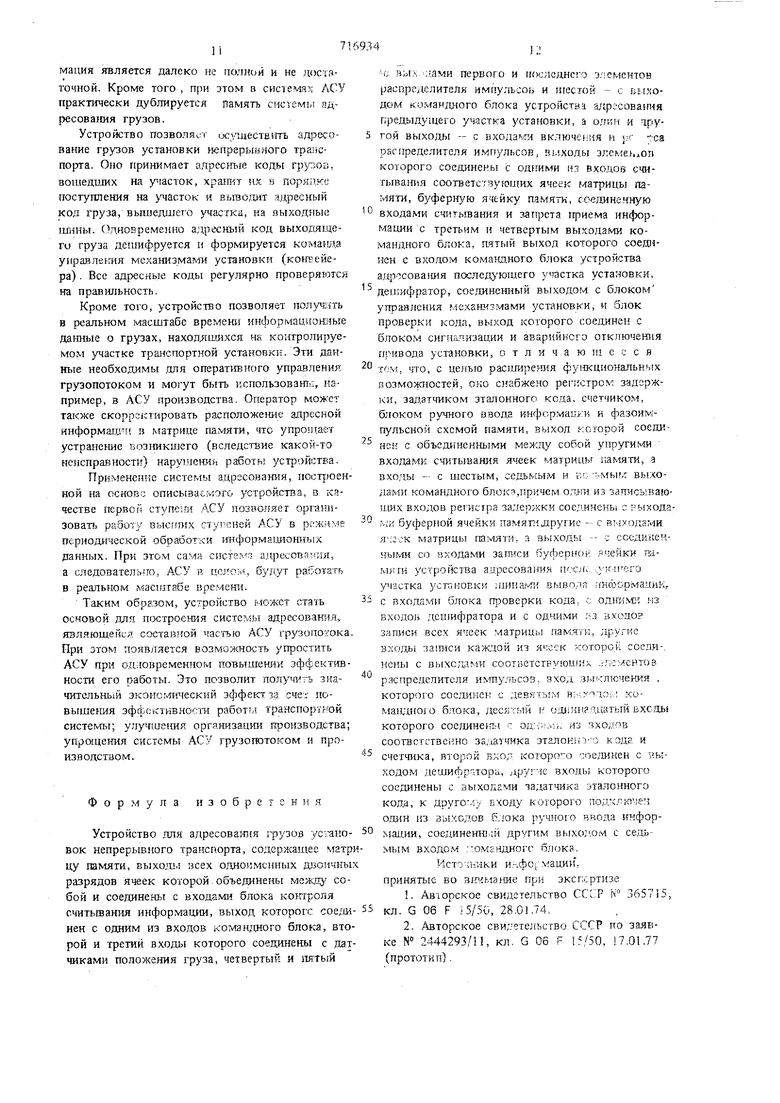

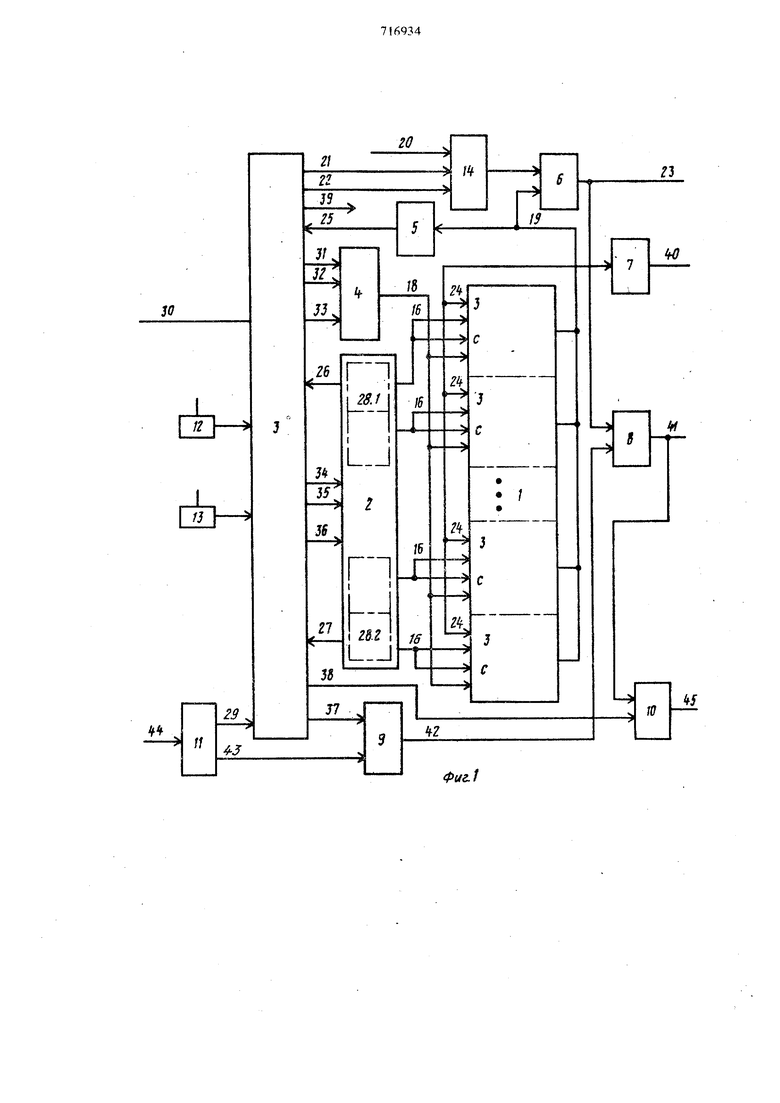

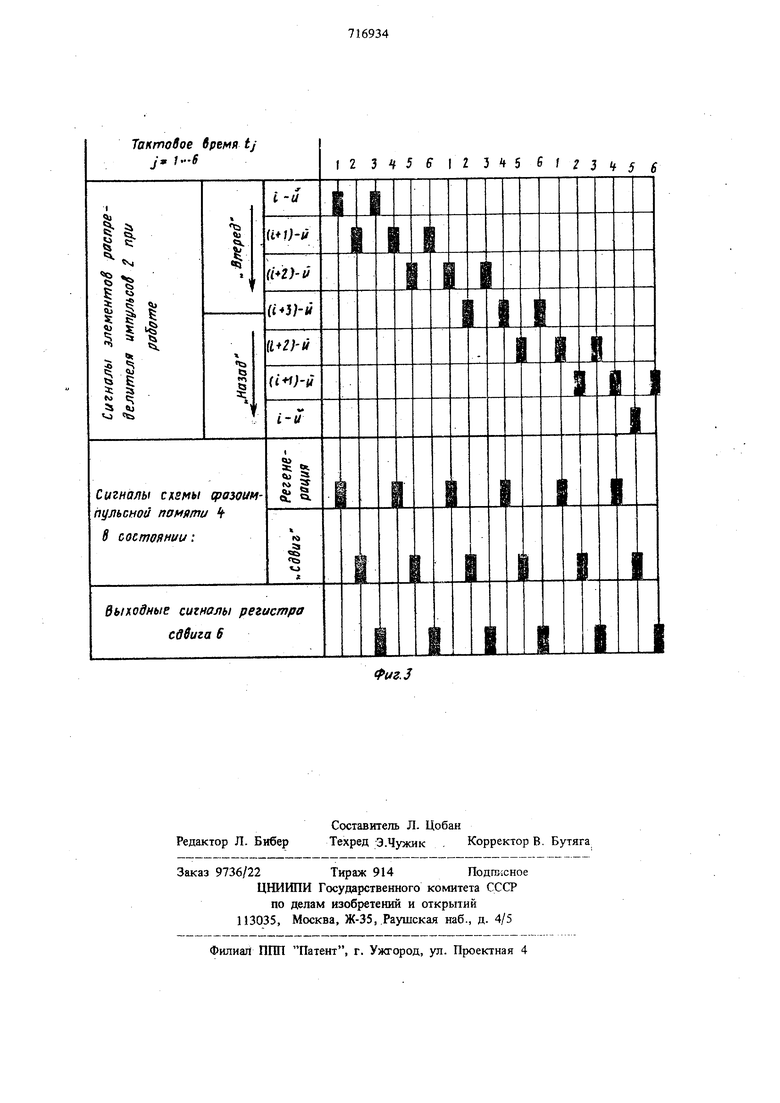

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для адресования грузов установок непрерывного транспорта, содержащее матрицу памяти, выходы всех одноименных двоичных разрядов ячеек которой объединены между собой и соединены с входами контроля считьшания информации, выход которого соединен с одним из входов командного блока, второй и третий входы которого соединета. с датчиками положения груза, четвертый и гштый с выходами первого и последнего элементов распределителя импульсов и щестой - с выхо.цом командного блока устройства адресования предыдущего участка установки, а один и другой выходы - с входами включения и реверса распределителя импульсов, выходы элементов которого соединены с одними из входон считывания соответствующих ячеек )ииы гал-мти, буферную ячейку памяти, соединенную входам и считывания и запрета приема шформащ1Н с тре тьим и четвертым выходами командного блока, пятый выход которого соединен с входами командного блока устройства адресования послег ующего участка установки, дешифратор, соединенный выходом с блоком управления механизмами установки, и блок проверки кода, выход которого соединен с блокорл сигнализации и аварийного отключения привода yotsiHOBK Недостат1 :ом устройства также является отсутствие возможности коррекции адресной информации и получешш информационных дашгых о грузопотоке. Цель изобретения - расширение функционалг ных возможностей устройства. Указанная цель достигается тем, что устройство снабжено регистром задержки, задатгп;ком эталонного кода, счетчиком, блоком ручного ввода информащ и и фазоимпульсной схемой памяти, выход которой соединен с объединенными между собой дpyти IИ входами сштывания ячеек матрицы памяти, а входы - с шес тым, седьмым и BOCbNP- iM выходами коман,а,кого блока, причем од1Ш из загаюывающих входо регистра задержки соедярюны с выходами буферной ячейки памяти, другие - с выходг.ми ячеек матрицы памяги, а выходы - с сосдипеи ными с входами зашси буферной ячейки памяти устройства aдpecoвaшiя после.дующего участка устз.новки иптамл вывода информациги, с входаг-.Щ блока проверки кода, с одними из входов дешифратора и с одними из входов записи всех ячеек матрицы памяти, другие БХО ды записи каждой из ячеек которой сосд5шены с выходаш соответствующих элементов распределителя имггульсов, вход выключения которого соединен с девятым выходом командного блока, десятый и одиннадцатьп входы которого сое.дине}гы с одними из входов соотв.етствен но задатчика эталонного кода и счетчика, второй вход которого соединен с выходом дв1шяф ратора, другие входы которого соединены с вы ходами задатчика эталонного кода, к ,1у входу которого подключен один из выходов блока ручного ввода информации, соед- неню ш другим выходом с седьмым входом комавдного блока. На фиг. 1 приведена функциональная схема устройства дня адресования, на которой уголщенными линиями выделены многокана:11Ы1ые связи, а индексами С и 3 отмечены входы считывания и записи ячеек матрицы памяти. На фиг. 2 приведен пример принцигшал1 ной 7 схемы матрицы памяти, псютроеиноГ на ферриттраюь.: горных элементах и содерхсащей две двухразря, ячеГжи. На фиг. 3 предста{ лена временная диаграм.ма работы элементов распределителя кмпульсов, фазоимпульсной схет-л, памята и регистра задержки. Устройство для адресования сосгоит из матрицы памяти i, реверсивного распределителя импульсов 2, командного блока 3. фазоимпульсной схемы памяти 4, блока кокгрохш считывания информатши 5 регистра задержки 6, блока проверки кода 7, дешифратора 8, задлтчика этагюнного кода 9. счетчики 10, блока ручного ввода информации 11, датчиков положенля груза, датчика входа 12 ;;а контролируемый участок транспортной установки и датчика выхода 13 с контролирзсмого участка, буферной ячейки памяти 14. Матрица памяти 1 построена на элементах (шпример, феррит- тра}1зисторных) 15 и имеет m ячеек памяти по п двоичных разрядов в каждой. На фиг. 2 и , кажд.ый феррит- транзисторный злекгент 15 обведен пуга тирной , а каждая ячейка матриць памяти - штрих - п-унктирной линией. Обмотки считьвзания элементов 1.5 одной ячейки (на фиг.2 - верхние обмотки) соединены между собой последовательно и ооразугот обмотки считьшагтия ячеек матриЩ) памяти 1. OjxHK конец обмоток считывания ,эдой ячейки матрицы тмяти 1 по пгане 6 через разделительный диод 17, 1 соеди ; с вьгхэпом соответствующего элсме та резср«Зг-вгс распосдслите.ьл импульсов 2. Вторые 1 ;о1шк обмогок сщ1ть Еа:(1;;я всех яч:;ек матргщы пагляти 1 объедине &г между собой и образуют шину 18, соединентю с выходом фазоимпу шсяой схемъ памяти 4. Таким образом, элементы расгтределитоля импульсов 2 и фаюимлульсная охема памяги 4 соединены межг,у собой ; последоэательпо через обмотки счз-ггывания ячеек матрицьь памяти 1. Вь ходьг элементов LS однопт и того разр.ада всех ячеек матрзщ . 1 через раздел яте; ьнью диоды 17.2 с51 ед}гн1;11Ы ме:н.:ду собой в 11ш.кь 19, которые соединены с входами бшока контроля считыв&т-л информациз-- 5 и з.зписывагоггими входам регистра задержк 6, которьн также имеет п двоичюлх рРзрядоЕ. Другие записывающие входы репстра задержки 6 сседлнень с выходами буферной ячейки памяп) 14, вход) которой згзодятся на шины 20 выхода адресной информагши аналогишого устройства адресования предшествующего участка транспортной установки. Вход запрета приема адресной информации буферной ячейки памяти 14 соединен 21, а ее вход счит.ывания - шиной 22 с аыходами командного блока 3. Выходы регистрл залсржки 6 соединены с шинами 23 вывода информашш с входами, блока проверки кода 7, с входами дешифратора 8, с шинами 24 записи информация R ячейки матрицы памяти 1. Шины 24 через разделительные диоды 17.3 связыва-ют между собой входы обмоток записи элементов 15 одноименного разряда всех ячеек матрицы памяти 1. Другие концы обмоток записи всех элементов 15, входящих в одну ячейку матрицы гамяти 1, объединены меж ду собой и соединены шинами 16 с выxoдa ги соответствующих элементов распределителя импульсов 2. Таким образом, .обмотка записи элементов 15 (на фиг. 2 - вторые сверху) соединены последовательно с элементами соответствующих разрядов регистра задержки 6 и соответствугощими ячейками матрищз памята элементами распределителя импульсов 2. Входы командного блока 3 соединены с выходами датчиков положения груза 12 и 13 шиной 25 с выходом блока контррля считывания информации 5; щинамн 26 и 27 с выходами первого и последнего соотвественно 28. и 28.2 элементов распределителя импульсов 2, ишнами 29 с выходами блока ручного ввода информации Г1; с шиной 30, которая заводитс на выход командного блока аналогичного устройства адресования предшествуюи ;его участка транспортной установки. Выходы командного блока 3 соединены также шинами 31, 32 и 33 с первым, вторым входами включения и с входом выключения фазоимпульсной схемы памяти 4; шинами 34, 35 и 36 с входами включения, реверса и выкл чения распределителя импульсов 2; шиной 37 с входом считьгоания задатчика эталонного кода 9: шиной 38 с входо.м сброса счетчика iO, шиной 39 с входом командного блока аналогичного усгройства адресования последующе го участка транспортной установки. Выход блока провзрхи кода 7 соединен выход шиной 40 с блоком сигнализации к аварийного отключения привода установки. Выход дсиифрзтора кода 8 соединен с вхо дом счетчика 10 и выходной шиной 41, которая заво;здтся на блок управления механизмам установки. Выходы задатчнка эталонного кода 9 шина ми 42 соединеш) с установочными входами дешифратора 8, а шины 43 соединяют входы установки задатчика 9 с выходом блока ручного ввода информации 11, входы которого соединены с шинами 44, которые заводятся на выходы задающих устройств оператора (напркмер , на выходы кнопок, переключателей и гф Выходы счетчика 10 через итны 45 заводя ся на устройства индикации (например, цифровые лампы). Шины 23 вывода информации заводятся на идины приема информащи ан.члогичного устройства адресования псх-ледующсIO участка транспортной установки и на Bxn.ruii устройства вьшоп.а информации, например, букнепечатающего. Элементы (блоки) уст{юйства адресования работают под воздерктвием тактовых сигналов и взаимодействуют между собой в задаваемом тактовым сигнзлом (и пульсом) времени tj, где j 1...6 и означает порядок сигнала t в тактовом цикле. Каждый элемент распределителя импульсов 2 (после его включения) срабат1 1вает три раза, причем между двумя срабатываниями одного элемента срабатывает соседний элемент, как это показано на фиг. 3. Пусть, например в такте tj срабатывает г-й элемент распределиггеля импульсов 2. Тогда ; в такте tj сработает (+1)-й элемент; в такте t3 сработает i-й элемент; в такте 14 сработает (1+})-й элементов такте t сработает (1+2)-й элемент; в такте tg сработает (|+1)-й элемент, в такте 11 (следующего тактового цикла) сработает (i+2) -и элемент и т.д. Т.е. прловитт элементов распределителя им 1ульсов 2 (например все нечетные элементы) будет срабатывать в тактах , tj и tj, а вторая половина элемсптов - в тактах tj ,14 и t , Фазоимггул1;С1сая схема па.чшти 4 может нахошгтъся в одном ИЗ Трех состояний: выключено ; сдвиг. регсг.епация. В состо.янии снвиг она срабатьшает в тактах ti и t.;. а Б состоянии регенерация в тактах ti и t4 (см. фиг. 3). Таким образом, схема 4 проп скает через обмотки сштывания ячеек матрицы памяти 1 сигналы элементов распределителя импульсов 2 в тактах; t2 и ts , если она находится в состоянии сдвиг, tj V 4 если ока на :олится в состоянии регенерация. Регистр задержки 6, получив адресный код с вьЕ.хода ллеметсв 15 матрииь палтяти 1, каждый из которых может быть реатшзован л аггрир,,ер транзисторе 46 и резисторах 47, 48 , в тактах tt/t4 или tj, 15, возвращает этот код в элементы г атркиы памяти 1 через элементы распределителя импульсов 2 в момент их срабатывания в тактах ±з и t. Следователь;ю, адресная информация будет возвращена в ту же ячейку матрицы памяти, если схема памяти 4 находится в ссктоянии регенерация или сдвинута в соседнюю ячейк если схема памяти 4 - в состояго И сдвиг. При этом один из первых двух сигналов каждого элемента распредслите.пя импульсов 2 испо.пьзуется для ,шания информации с ячеек матрицы памяти 1 соответственно в режимах сдвига и регенерации , а третий сипгал для возврата информации в матрицу памяти. Адресные коды грузов, находящиеся на участке транспортной установки, хранятся в ячейках матрицы памяти 1 в порядке поступления грузов на участок. Причем, адресный код , зашедшего последним на участок, хранит ся в последней ячейке матрицы памяти 1; зашедшего перед ним груза - в предпоследней и т.п. При входе очередного груза на участок транспортной установки информация в матрице гилгяти 1 должна сдвинуться на ячейку впepeд а адресный код вошедшего груза должен записаться в последнюю ячейку, Пусть на участок транспортной установки входит очередной груз. При его выходе с предыдущего участка транспортной установки устройство адресования этого участка передает адресный код груза ка шины 20, послав предварительную на шину 30 входа комагздного блока 3, в ответ на которую последний сигналом по цшне 21 разрешит гфием кода буферной ячейке памяти 14. При входе груза на з шсток по сигналу датчика 12 командный блок 3 включит по шине 34 р;зсг1ределитель импульсов 2, а сигналом по шине 31 переведет фазоимпупьснуго схему памяти 4 в cocTOHiffle сдзиг, т.е. на работу в тактах t2 и tj., Распределитель импульсов 2 начнет Псючеред но считывать ячейки матрицы гамяти I. Если в такте tj сработает, i-й элемент распределителя имп льсов 2, то его сигнал не сможет считать -1о ячейку матрицы памяти 1, так как схема памяти 4, последовательно с которой включень обмотки с шть вания ячеек матрицы памяти, не работает в этом такте. Затем в так те tj сработает (|-И)-й элемент распределителя его сигнал пройдет через обмотку считыважя (+1)-й ячейки матрицы памяти 1 и схему па мяти 4, считая при этом адресный код, содержащийся в этой ячейке. Сигналы с ее выхода по шинам 9 поступят в регистр задержки 6 и в такте t3 появятся на его . В это время вновь сработает i-й элемент распределителя импульсов 2 и через него регастр задержки 6 (по шинам 24 и 16) запишет информаци в i-ю ячейку матр1щь памяти 1. Таким образом, адресный код, содержавшийся ранее в (1+1)-.й ячейке матрицы памяти 1, перепишется в ее i-ю ячейку. Аналогично будет сдвину1га информация в остальных ячейках матрицы пйм ти 1. При считывании последней ячейки матрицы памяти 1 последний злемет распределителя им пульсов (при своем первом срабатывании) пошлет по шине 26 сигнал на вход командног блока 3. После записи информации в предпоследнюю ячейку матрицы памяти команд1ный блок 3 сигналом по шине 22 переведет адрес&гй код вошедшего груза с буферной ячейки 14 в регистр 6, а тот перепишет его через оследний элемент распределителя импульсов 2 последнюю ячейку матрицы памяти I. Затем игналами по шинам 33 и 36 командный лок 3 выключит схему памяти 4 и распределиель импульсов 2. При выходе груза с участка транспортной установки его адресный код должен быть стерт из памяти матрицы 1 и выведен на выходные шины 23. При этом сработает датчик 3, по сигналу которого блок 3 включит по шине 34 распределитель импульсов 2, а сигналом по пшне 32 переведет фазоимгг/льсную схему памяти 4 в режим регенерагик, т.е. на работу в тактах tj к t. Пусть адресный код выходящего груза хранится в (i-H)-й ячейке матрицы памяти (ячейки с меньшим порядковым номером шходятся в нулевом состоянии). При срабатывании в такте tj i-ro. элемента распределителя импульсов 2 он через схему памяти 4 считает i-ю ячейку памяти матрицы I, но она свободна от информации. В такте t2 сработает (i-H)-й элемент распределителя импульсов 2, но его сигнал не пропустит схема памяти 4. В такте 1з вновь сработает i-й элемент распределителя имп льсов 2. но так как в регистр 6 информация не вводится, то i-ю ячейку матрицы памяти запишется нулевой код. В такте i (+5)й элеме1-гг распределителя импульсов через схему памяти 4 считает (i+})-ro ячейку матрицы 1шг 1яти 1. Содержшцийся в ней код по иынам 19 поступит на вход регистра 6 и блока контроля: считьЕвания информации 5. Последний по и.ине 25 пошлет сигнал на вход блока 3, по которому сигналами по шз-шам 36 и 33 блок 3 зы- ; ключит распределитель импульсов 2 к схему памяти 4. В результате, при срабатьшании регистра 6 в такте tg адресный код не будет возБрашен в ()-ю ячейку матриид, ш.мятн i, но будет передан на выходные шины 23 и вход деишфратора 8. По команде, пос:г пившей от блока 3 по Ш1ше 37 задатчик эталонного кода 9 по шинам 42 передаст эталонный код на установочные входы дешифратора 8, который, сравнив коды, сформирует на выходной пшне 41 команду управления мехагшзмом транспортной установки. Одновременно с выключением распределителя импульсов блок 3 по шине 39 пошлет команду передачи информации на вход аналогичного устройства адресования последующего участка транспортной установки. В процессе обработки адресной информа1.1ии все адресные коды поступают с выхода регистра 6 на вход блока проверки кода 7. При обнаружении нарушения кода блок 7 формирует 9 аварийный сигнал, который с выходной ишны 40 подается на блок сигнализации и (или) аварийного отключения привода установки (ко вейера) . Оператор- имеет возможность определить: порядок движения грузов ( по их адресным кодам) на контролируемом участке транспортн установки; количество грузов заданного адресного кода Необходимые команды, а также заданный адресный код оператор формирует, например, с помощью кнопок, переключателей, выходы которых) заведены на шины 44, а через блок 1 ручного ввода информации по шинам 29 и 43 передает на командный блок 3 и задатчик зталонного кода 9. Вместо оператора соответствующие команды могут подавать управляющие машины АСУ производства. При этом командный блок 3 по шине 34 включает распределитель импульсов 2, а сигналом по шине 32 переводит схему фазоимпульсной памяти 4 в состояние регенерация. В этом состоянии схема 4 работает в тактах t и t4 и пропускает на входы считывания ячеек матрицы памяти 1 только те сигналы распределителя импульсов 2, которые совпадают с этими тактами. Так, например (1+1)-й элемент распределителя ИМпульсов 2 сработает первый раз в такте t2, но его сигнал не пройдет через обмотки считьгоания матрицы памяти 1, когда этот элемент сработает в такте t4, он считает (1+1)-ю ячейку матрицы памяти. По шинам 19 содержащаяся в ней информация поступит в регистр 6, который в такте tg возвратит эту информацию в (1+1)-ю ячейку матрицы памяти 1 через шины 24, 16 и (1+1)-й элемент распределителя импульсов 2. Аналогично регенерируется информация и в остальных ячейках матрицы памяти 1. Таким образом, по мере работы распределителя имп льсов 2 вся адресная информация поочередно будет проходить через регистр 6, а с него поступать на выходные шины 23 и вход дешифратора 8. С шин 23 адресная информация передается на устройства вывода, например, на буквопечатающие устройства .или вход машин АСУ. При определении количества грузов заданно го кода этот код вводится через блок 11 и задатчик 9 на установочные входы дешифратора 8 по командам блока 3, поступающим через шину 37. Коды, содержащиеся в матрице памяти 1, последовательно дешифруются, а результаты дешифровки с выхода дешифратора 8 передаются на вход счетчика 10. Предварительно по шине 38 командный блок 3 устанав ливает с-1етчик 10 в исходное положение. Шины 45 счетчика 10 выводятся на устройства индикации, например, на цифровые лампы или на вход маишн АСУ. Оператор может также скорректировать расположение информации в матрице памяти 1, проведя ее сдвиг вперед или назад. Для этого он формирует соответствующие которые по шинам 44 через блок 11 и шины 29 поступают в блок 3. Последний переводит схему памяти 4 в состояние сдвиг и вк.пючает распредел1Пель импульсов 2 по шине 34, если проводится сдвиг информации вперед, . по шине 35, если гфоводится сдвиг информации назад (для сдвига назад используется обратное включение распределителя импульсов 2). При сдвиге вшеред устройство работает подобно тому, как и при входе груза на участок транспортной установки. Аналогичным образом оно работает и при сдвиге назад. При этом сигналы распределителя импульсов 2 продвигаются от элемента со cTapimiM порядковым номером к элементу с младшим номером. Пусть (при сдвиге назад) в такте ts сработал (1+2)-й элемент распределителя импульсов 2, который по шинам 16, 18 и через схему памяти 4 считает (1+2)-ю ячейку матрицы памяти. Сигналы с выхода последней по шинам 19 поступят в регистр 6, а с его выхода в такте tg через шины 24, 16 и (+3)-й элемент распределителя импульсов 2 запишутся в (1+3)-ю ячейку матрицы памяти. Далее вновь в такте tj сработает (1+2)-й элемент распределителя, но его сигнал не пропустит схема памяти 4. В такте t2(i+)-й элемент распределителя 2 через схему 4 считает (1+1)-ю ячейку матрищл памяти I, а регистр 6 через (1+2)-й элемент распределителя импульсов 2 перепишет адресную информацию в (1+2)-ю ячейку матрицы памяти 1. Аналогично вся информация, содержащаяся в матрице памяти 1 будет сдвинута на одну ячейку назад. „ По окончании работы распределителя импульсов 2 он по шинам 26 шт 21 (в зависимости от направления включения) потилет сигнал на блок 3, который выклющ1Т распределитель импульсов 2 и схему памяти 4 сигналами по шинам 36 и 33. Установки непрерывного транспорта берут на себя основной грузопоток предприятия, организовьшают производство. Поэтому информационные данные о грузопотоке необходимы для АСУ транспортным потоком и для АСУ производства в целом. Существуюидае системы адресования грузов не позволяют снять информацию о грузопотоке, не нарушая своей работы. Поэтому системы АСУ от системы адресова1шя или параллельно с ней данные об отправляемых грузах к о прохождении грузов через от.чельпые заданные пункты транспортной установки. Такая яигЬормания является далеко не полной и не достаточной. Кроме того , при этом в сис1емя:ч АСУ практически дублируется память системы мдресования грузов. Устройство позволяет 1х-уществ5ггь адресОванне грузов установки непрерыниого травепорта. Оно принимает адресные коды грузов, вошедших на участок, хршп;т их в порялкс поступления на часток я вьгаодат адресный код груза, вышедшего участка, ка аыходные шины. С.|п.коЕременно адресный код выходящего груза дешифруется н формируется управлеютя механизмарли установки (конвейера) . Все адресные коды регулярно проверяются на правютьность. Кроме того, устройство позволяет получать в реальном масштабе времешг информациоияые данные о грузах, находл1Ш1хся на контролируемом участке транспортной установка. Эти данные необходимы ,для оперативного управления грузопотоком и могут быть кспользоват -, например, в АСУ производства. Оператор может также скорректировать расположение адресной информащп в матрице памяти, что ynpoijiaer устрансьше возьшкшего (вследствие какой-то неисправности) нарушения работы устройства. Применение системь: адресования, ной на основе описываемого устройства, в качестве первой ступсьги АСУ позволяет орган.нзовать работу выспшх сту -еней АСУ в режиме период1-гческой обработки информационных данных. При этом сама системз адрессва-ягя, а следователь г го, АСУ в цшто1-д, будут работать в реальном масштабе времени. Таким обргзом, устройство может стать основой для п(х;троекия системы адресования являющейся составной частью АСУ грузопо :ока При этом появляется возмолшость упростить АСУ при одновременном повьгшенли эффектив ности его работы. Это позволит получк7-ь зкачительньш Э -соноГД1иеский эффект за сче;: повышения эффективности работь транспо;)тной систегуты; организации производства; упрощения системы АСУ грузопотоком л производством. Формула изобретения Устройство для адресования дфузов услно вок непрерывного транспорта, содержащее матр цу памяти, выхода. всех одноименных дззоичны разрядов ячеек которой. объединены собой и соединены с входами блока контроля считьшания информации, выход которого соеди ней с одним из входов командного блока, вто рой и третий входы которого соединены с дат чиками положения груза, четвертый и глтьш -с в:лл.;),ами первого и (госледнсго з;:ементон распределителя импульсоь и шестой - с ы яодом командного блока устройства адресования предыдущего участка установки, а один и другой выходы - с входар..ги включения н рс -:cz распределителя импульсов, выходы элемеь.оп которого соединены с одними из входов считывания соответствугоишх ячеек матрицы памяти, буферную ячейку памяти, соединенную входами считывания и запрета гфиема информации с третьим и четвертым выходами командного блока, пятый выход которого соединен с входом командного блока устройства адрссова1дая последующего угастка установки, дешифратор, соединенный выходом с блоком управления мехгннзмами установки, и блок проверки кода, выход которого соединен с блоком сиг.1 изации и аварийного отключешш привода установки, отличающееся том. что, с целью расширения фу1жциональнь х возможностей, око снабжено регистром задержки, зад.атчиком эталонного кода, счетчиком, блоком ручного ввода информаиуи и фазоимпульсной схемой памяти, котооой соединев с объединенными между собой упругикад входами считывания ячеек матрицы памяти, а входы --- с шестым, седьмым и в-,:- :ьл1ым выходами командного блок,причем оляи из записьваюiiiHX входов peprfcipa задержки соедннскь с гЫУ.олаiK буферной ячейки памятидругие - с вьгходами матрицы naivwTH, а -выходы -- с сосдиг-енными со входами загшси буферной ячейки тMi.jK устройстеа адресования iiocju .го у-|астка устаковки niHP.af/ni вывела ангоормапик, с входами блока проверки кода, с одним:; мз входов дешифратора и с одними ЗХОДОР записи всех ячеек матрицы памлтк, другие входы записи каждой из ячеек которой соепи-, пены с соотБетствуощнх .;,.;:ментоз распреде.лителя ил-шульсоз, вход зьпчлюченкя . которого соединен с девятьм нь:.;ог1П: командного блока, десятый i од11К адцатьш вхсдь которого соедлне ГЬ с од:-П1м;: из -входов соответстве1шо задатчика эталоны )-о кодг и счетчика, второй вход которо о соединен с i biходом дешисЬрктора, другие входы которого соединены с выходами задатчика эталонного кода, к друголу входу которого подк.г;ю- еь о.дин из выходов б..юка ручного ввода инфорГ1 адии, соединенН1.:й другим выхо;|,ом с седьмым ВХО.ЦОМ :-ом Ндногс блока. Исто;н-;-1ки Иг.фО ;маш«, принятые во .ание при экспертизе 1.Авюрское свидетельство СССР К 365715, кл. G 06 F J5/50, 28.01.74. 2.Авторское сви;:ете; ьство СССР по заявке № 2444293/11, кл. G 06 F 15/50, 1.7.01.77 (прототкн).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресования подвижных объектов | 1977 |

|

SU676987A2 |

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ | 1973 |

|

SU365715A1 |

| УСТРОЙСТВО для АДРЕСОВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ ПОДЪЕМНО-ТРАНСПОРТНЫХ И ШАХТНЫХ УСТАНОВОК | 1970 |

|

SU270348A1 |

| Устройство для адресования грузов в установках непрерывного транспорта | 1976 |

|

SU662450A1 |

| Устройство для адресования подвижных объектов | 1979 |

|

SU767776A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство для опроса рабочих мест и ввода информации в систему адресования | 1972 |

|

SU491552A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

| УСТРОЙСТВО КОММУТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1971 |

|

SU320075A1 |

Авторы

Даты

1980-02-25—Публикация

1978-02-20—Подача