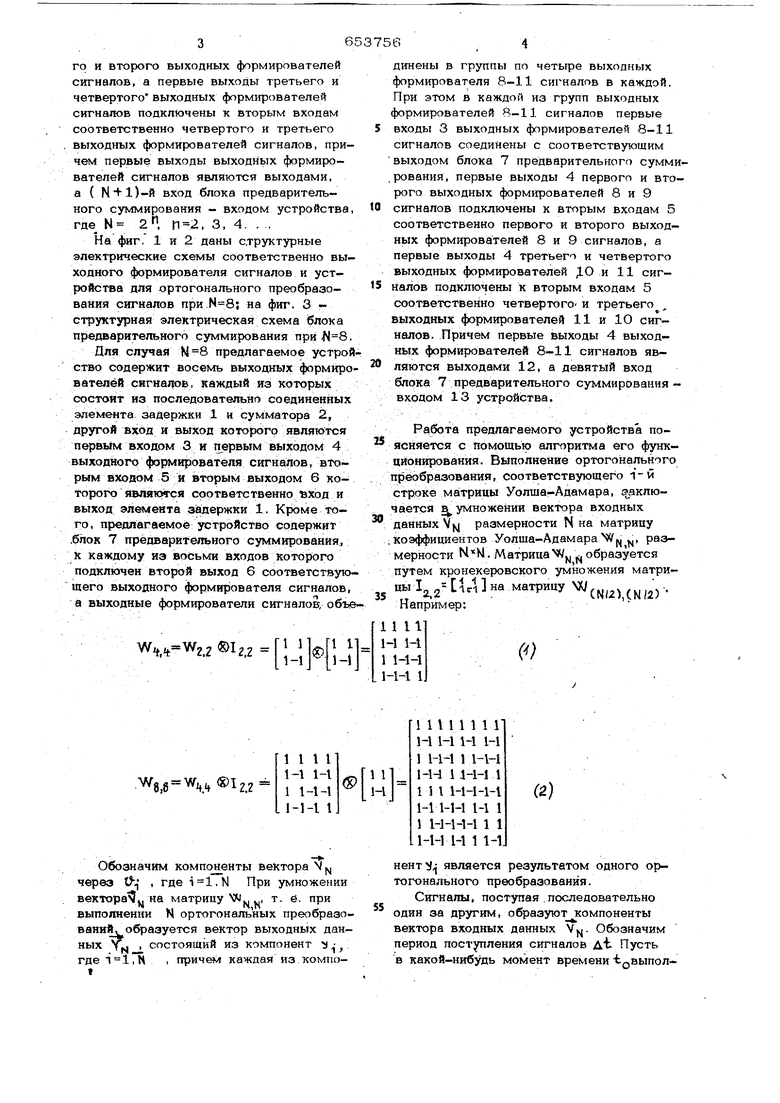

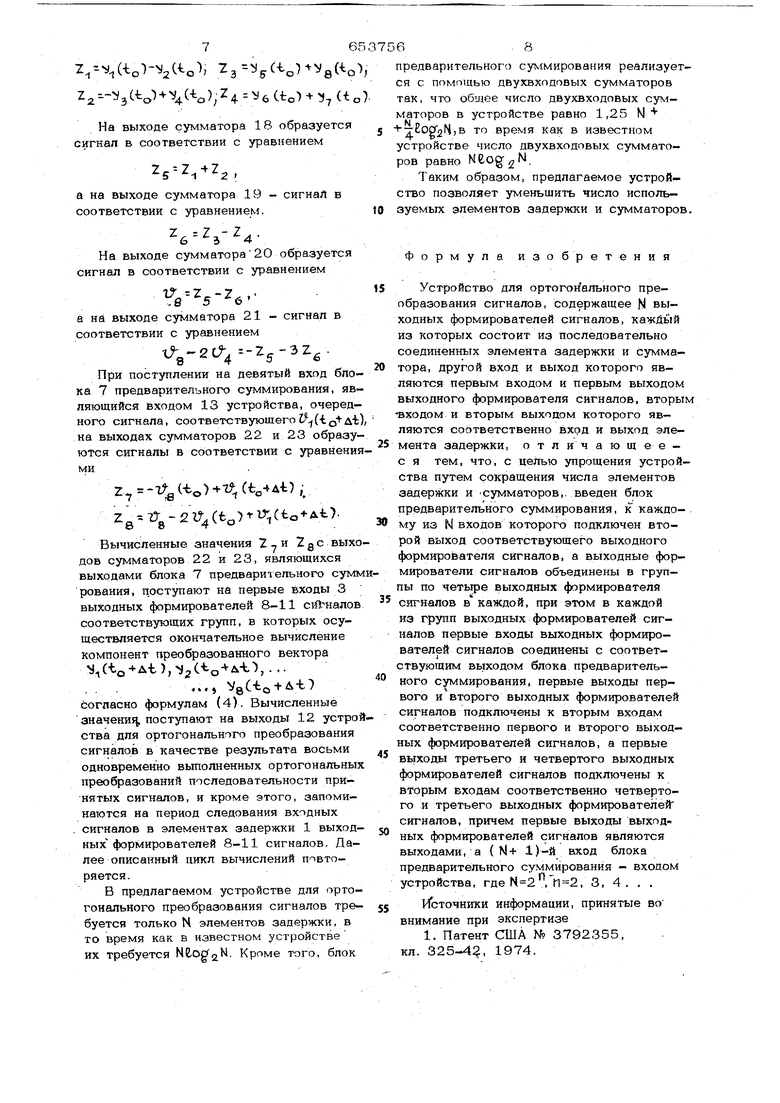

го и второтх) выходных формирователей сигналов, а первые выходы третьего и четвертого выходных формирователей сигналов подключены к вторым входам соответственно четвертого и третьего выходных формирователей сигналов, причем первые выходы выходных формирователей сигналов являются выходами, а { )-ft вход блока предварительного суммирования - входом устройства где N 2, , 3, 4. . . На фиг. 1 и 2 даны с.труктурные электрические схемы соответственно выходного формирователя сигналов и устройства для ортогонального преобразования сигналов при на фиг. 3 структурная электрическая схема блока предварительного суммирования при 8 Для случая предлагаемое устро ство содержит восемь 1выходных формиро вателей снгна;|ов, каждый из которых состоят из последовательно соединенных элемента задержки 1 и сумматора 2, другой вход и выход которого являются первым входом 3 и первым выходом 4 выходного формирователя сигналов, вторым входом 5 и вторым выходом 6 которого являкугся срртввтс твенно вход и выход элемента задержки 1. Кроме того, предлагаемое устройство содержит .блок 7 предварительного суммирования, к каждому из восьми входов которого подключен второй выход 6 соответствую щего выходного формирователя сигналов а выходные формирователи сигналов, объ

W:,W2.2®l2. динены в группы по четьфе выходных формирователя 8-11 сигналов в каждой. При этом в каждой из групп выходных формирователей 8-11 сигналов первые входы 3 выходных формирователей 8-11 сигналов соединены с соответствующим выходом блока 7 предварительного суммирования, первые выходы 4 первого и второго выходных формирователей 8 и 9 сигналов подключены к вторым входам 5 соответственно первого и второго выходных формирователей 8 и 9 сигналов, а первые выходы 4 третьего и четвертого выходных формирователей Д.О и 11 сигналов подключены к вторым входам 5 соответственно четвертого- и третьего выходных формирователей 11 и 10 сигналов. Причем первые выходы 4 выходных формирователей 8-11 сигналов являются выходами 12, а девятый вход блока 7 предварительного суммирования входом 13 устройства. Работа предлагаемого устройства поясняется с помощью алгоритма его функционирования. Выполнение ортогонального преобразования, соответствующего 1-й строке матрицы Уолша-Адамара, %включается умножении вектора входных данных V| размерности N на матрицу коэффициентов Уолша-Адамара , j, размерности . Матрица V/ образуется путем кронек ровского умножения матри(N/2),(N;i)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1982 |

|

SU1098005A1 |

| СПОСОБ, УСТРОЙСТВО И СХЕМА ДЛЯ ОСУЩЕСТВЛЕНИЯ ПРЕОБРАЗОВАНИЯ АДАМАРА | 1994 |

|

RU2150141C1 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| Система последовательного финитного управления конечным состоянием линейных стационарных динамических объектов | 1987 |

|

SU1467534A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| СВЧ-поляриметр | 1988 |

|

SU1649472A1 |

| ЦИФРОВОЙ КОМПЕНСАТОР ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2087000C1 |

| Устройство для выделения ортогональных составляющих электрических величин | 1989 |

|

SU1744733A1 |

W«« Wub ®Ь,

%л

8,62.2

Обозначим компоненты вектора | через , где ,N При умножении вектора., на матрицу VJ , т. е. при

выполнении N ортогональных преобразований.., образуется вектор выходных данных , состоящий из компонент , где , N , причем каждая из компоI

()

является результатом одного ортогонального преобразования.

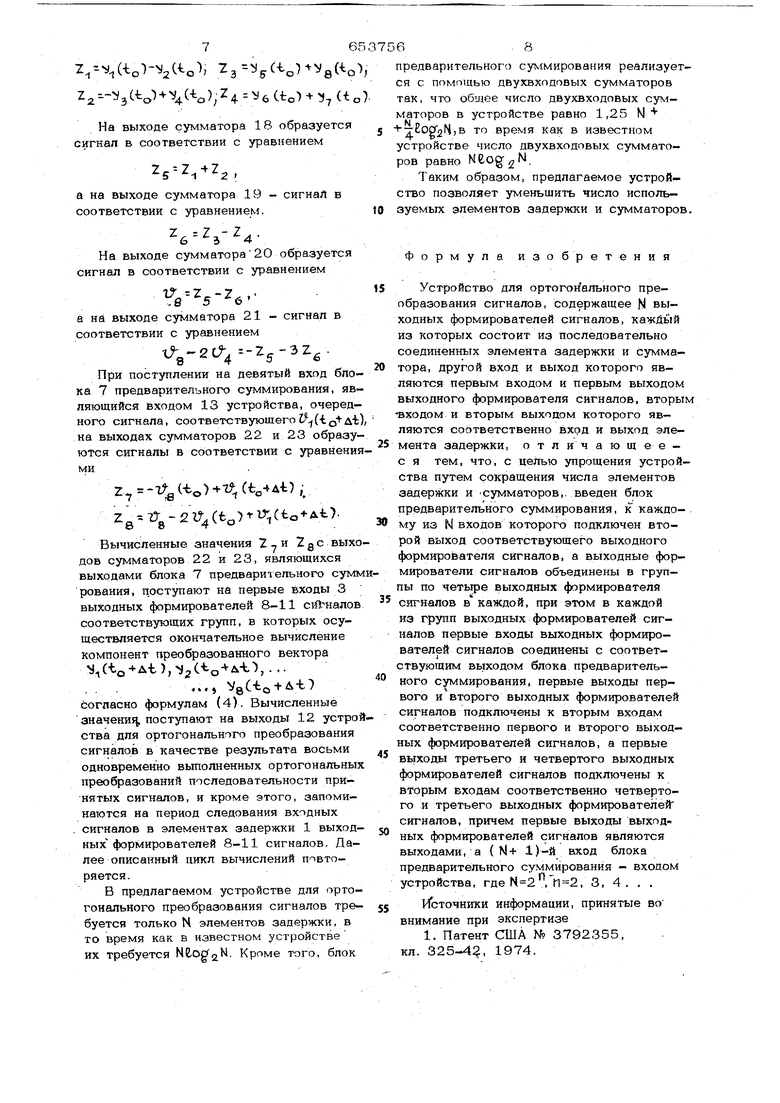

Сигналы, поступая.последовательно один за другим, образуют компоненты вектора входных данных . Обозначим период поступления сигналов Ai. Пусть в какой-нибудь момент времени tQвыпoлнено вычисление (-tp) 1 - Y((tp) вектора выходных данных. В момент вре- Mennij At поступает новый входной сигнал. Принимая его, необходимо изменить вектор входных данных следующим образом; сместить все компоненты так, чтобы ( ( отбросить ком ноненту на компоненте t-J Ct j+A-t) присвоить значение вновь пришедшего сигнала. Рассмотрим матрицу Х/ . Компонен ты вектора выходных данных (-t -t-u-t; можно получить, используя значения компонент .j (t-o) по следующим формулам, I/,1Ь + ДП /i(b)- 1 (to) + , (to -t- Д) ir2(b+At )-lf2 (to)-%(to) +(f-i (0 + Д ) L If3(fo+ДО ytf (fo) (to) u ) if(to+/Jf -1ГзШ-№р(У ( flt)J И.З приведенного выше правила построения матрицы Уолша-Адамара (2) видно, что матрица Wgg состоит из блоков, представляющих матрицу, вида ,,4 Поэтому для преобразования Wg g можно записать уравнения, используя (3) y,(fo+uf) yi(fo)(o)(o+un Уг(о+М)-уИЬ)(о)(Ь-ьДО ff3(fo+Af) ifzf(b)(b)(fo + fln ,)(о)) (fo+ЛП y5({o-byif) 1)5(0)Щ ((if(fo)+(,(fo+M) F6 ()-g6(fa)(b)(to)() r7() 1Г8(Ы+1%(Ы-2i /t(fe)(V/10 У8()(Ь)(Ь)-Z(4(fo)(fo+M)/ Для N 16, 32, 64 . . . выражения; аналогичные формулам (З) и (4)полу- I чаются по индукции. Из формул (3) и J (4) видно, что для вычисления.(-(tg+A-t) необходимо хранить в памяти (IQ) и (to Так, для , необходимо запомнить t (to) для Л (tj,) и IJ-oCio - ДЛЯ ) . V (ip), V(V Ч.(с) Однако из свойств матрицы УолшаАдамара известно, что она обладает обратимостью , т. е. (5) N N N,N В частности, для имеем t;(to)(i(toi- 2ftoi- j(to)-t f (6; Для получаем f(o}(Уi(o}-У2((о) + Уч(+95Ы-Уб(оП7((о)}1б (7) r6(io)(lfi({o)-Ifz(o)Ъ (Ь)+У (M-{f5 (Ь)(М+У7 (0) дв(о)}18 (б) Таким образом, алгоритм выполпения ртогонального преобразования при заключается в выполнении сперва вычислений по формулам (7) и (8), а затем по формулам (4). В целом, при любом N, для полного вычисления компонент вектора Yj () необходимо вычислитьN/4 - компонент вектора (to), а затем использовать их и компоненты BejcTopa ) ДЛя получения вектора (io+u-t)no формулам, аналогичным (4). Предлагаемое устройство при N 8 работает следующим образом. На 1-й - 8-й входы блока 7 предварительного суммирования, построет ного на сумматорах 14 - 23 (см. фиг. 3), аналогичных сумматорам 2, поступают с вторых выходов 6 выходных формирователей 8-11 сигналов хранимые в элементах задержки 1 значения ранее вычисленных компонент вектора Ya(-t):(to-),yi(to),...,gCta). На выходах сумматоров 1.4 - 17 образуются сигналы в соответствии с урав иями2-,( Z3--y a,nvQ(io ) 6 etc) 7 Uo Z Ha выходе сумматора 18 образуется сигнал в соответствии с уравнением s-z.z, а на выходе сумматора 19 - сигнал в соответствии с уравнением. выходе сумматора20 образуется сигнал в соответствии с уравнением а на выходе сумматора 21 - сигнал в соответствии с уравнением г 8-2С 4 - 5- 6При поступлении на девятый вход бло ка 7 предварительного суммирования, яв ляющийся входом 13 устройства, очередного сигнала, соответствующего 1(-Ьд-1-At на выходах сумматоров 22 и 23 образу ются сигналы в соответствии с уравнени ми Z,),CVA. Zg---2:r -2i 4( 4 2 g с ВЫХ Вычисленные значения T-j дов сумматоров 22 и 23, являющихся выходами блока 7 предварительного сум рования, цоступают на первые входы 3 выходных формирователей 8-11 сй налов соответствующих групп, в которых осуществляется окончательное вычисление компонент преобразованного вектора N|,Cto-t-At,). ,.., VeC-to-i- согласно формулам (4). Вычисленные значение поступают на выходы 12 устро ства для ортогонального преобразования сигналов в качестве результата восьми одновременно вьшолненных ортогональны преобразований последовательности принятых сигналов, и кроме этого, запоминаются на период следования входных . сигналов в элементах задержки 1 выход ныхформирователей 8-11 сигналов. Далее описанный цикл вычислений повторяется. В предлагаемом устройстве для ортогонального преобразования сигналов требуется только N элементов задержки, в то время как в известном устройстве их требуется NtOgf - Кроме того, блок предварительного суммирования реализуется с помощью двухвхоповых сумматоров так, что общее число двухвходовых сумматоров в устройстве равно 1,25 N1 vEog IHiB то время как в известном устройстве число двухвходовых сумматоров равно N Og-g Таким образом, предлагаемое устройство позволяет уменьшить число используемых элементов задержки и сумматоров. Формула изобретения Устройство для ортогонального преобразования сигналов, содержащее N выходных формирователей сигналов, кажйый из которых состоит из последовательно соединенных элемента задержки и сумматора, другой вход и выход которого являются первым входом и первым выходом выходного формирователя сигналов, вторым входом и вторым выходом которого являются соответственно вход и выход элемента задержки, отличающеес я тем, что, с целью упрощения устройства путем сокращения числа элементов задержки и сумматоров,, введен блок предварительного суммирования, к каждо- му из N входов которого подключен второй выход соответствующего выходного форм1фователя сигналов, а выходные формирователи сигналов объединены в группы по четь1ре выходных формирователя Сигналов в каждой, при этом в каждой из групп выходных формирователей сигналов первые входы выходных формирователей сигналов соединены с соответствующим выходом блока предварительного суммирования, первые выходы первого и второго выходных формирователей сигналов подключены к вторым входам ссЭответственно первого и второго выходных формирователей сигналов, а первые выходы третьего и четвертого выходных формирователей сигналов подключены к вторым входам соответственно четвертого и третьего выходных формирователей сигналов, причем первые выходы выход. Ных формирователей сигналов являются выходами, а ( М+ 1)-й вход блока предварительного суммирования - входом устройства, где ,п 2, 3, 4. . . Источники информации, принятые во внимание при экспертизе 1. Патент США № 3792355, кл. 325-4, 1974.

Фиг.2

- 4,

il хЦ

IS I/7

.;J

фиг

Авторы

Даты

1979-03-25—Публикация

1976-10-04—Подача