Изобретение относится к технике передачи дискретной информации по каналам электросвязи и может быть использовано в многоканальных модемах передачи дискретной информации с ортогональными составляющими для коррекции сигнала.

Цель изобретения - обеспечение коррекции при наличии частотного смещения спектра рабочего сигнала.

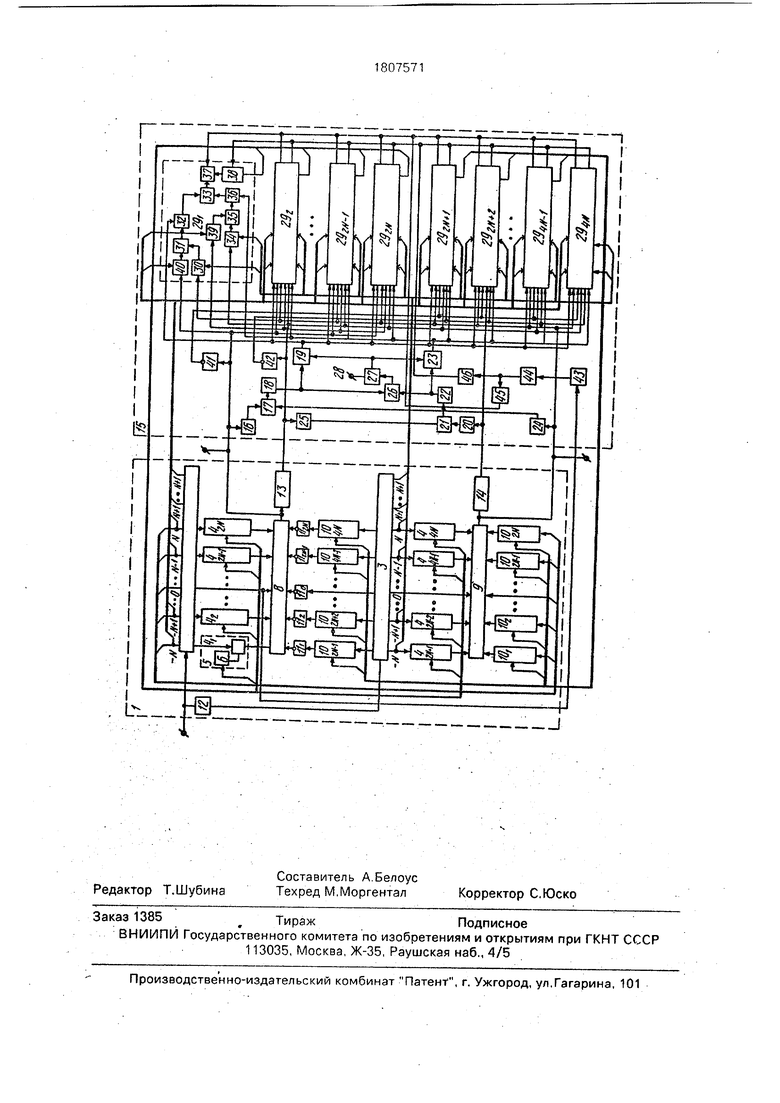

На чертеже показана электрическая структурная схема устройства.

Адаптивный корректор многочастотного сигнала с ортогональными составляющими содержит блок адаптивной коррекции 1, состоящий из первой 2 и второй 3 линий задержки. Задержка сигнала между соседними отводами линий 2 и 3 равна длительности котёльниковского интервала. Число отводов (2N+1) с номерами от (-М)-го по N-й включительно соответствует расчетной длине корректора, а отводы с номерами, начиная с (N+ 1)-го по (N+ Ь)-й,где L - число котельниковских отсчетов входного сигнала, располагающихся на длительности интервала ортогональности Т0, являются дополнительными. Каждый из 2N отводов линий 2 и 3 через соответствующий аттенюатор 4-I-44N, состоящий из последовательно соединенных шины начального значения умножающего коэффициента отвода 5, первого вычитателя б и первого перемножителя 7, второй вход которого соединен со входом аттенюатора 41-44N, а его выход с выходом аттенюатора, присоединен к соответствующему входу соответственно первого 8 и второго 9 сумматоров, выходы которых соединены соответственно с первым и вторым выходами блока 1 и устройства. Второй вход вычитателя 6 соединен со входом управления аттенюатора 4i-44N. a входы управления всех аттенюаторов 4i- 44N объединены в первую шину управления блока. 1. Кроме того, каждый из 2N отводов линии 2 через соответствующий дополнительный аттенюатор 101-102N присоединен к соответствующему дополнительному входу сумматора 9, а каждый из 2N отводов линии 3 через последовательно соединенные соответствующие аттенюатор 102N+1- 104N и дополнительные инвертор 111-112N подключен к соответствующему дополнительному входу сумматора 8. Аттенюаторы 1CH-104N аналогичны аттенюаторам . Центральные отводы линий 2 и 3, имеющие нулевые ноера.подключены к соответствующим входам сумматоров 8 и 9 непосредственно, кроме центрального отвода линии задержки 3, который подключен к соответствующему входу сумматора 8 через инвертор 11, Входы управления аттенюаторов 101-104N соединены во вторую шину управления блока 2. Отводы и дополнительные отводы линий 2 и 3 соединены соответственно в первую и вторую шины отводов блока 1. Вход устройства и вход блока 1 соединены со входом линии 2 непосредственно, а со входом линии 3 через широкополосный фазовращатель 12, кроме того, первая 13 и вторая 14 дополнительные линии задержки, задерживающие сигнал на время интервала ортогональности Т0, подключенные по входу соответственно к первому и второму выходам блока 1, присоединены по выходу соответственно к первому и второму дополнительным выходам блока 1, при этом отвод

линии задержки 2, имеющий нулевой номер, соединен с третьим дополнительным выходом блока 1, Блок 15 управления содержит последовательно соединенные первый квадратор 16, третий сумматор 17, первый

0 функциональный преобразователь 18, первый блок деления 19, причем вход квадратора 16 соединен с пербым входом блока 15, также содержит последовательно соединенные второй квдаратор 20, четвертый

5 сумматор 21, второй функциональный преобразователь 22, второй блок деления 23, причем вход квадратора 20 соединен со вторым дополнительным входом блока 15, второй вход и первый дополнительный вход

0 которого соединены соответственно со входами третьего 24 и четвертого 25 кв адрато- ров, выходы которых соединены со вторыми входами соответственно сумматоров 17 и 21. Блоки деления 19 и 23 аналогичны блоку

5 сравнения известного устройства (Авт.св.№ 790252, кл. Н 03 К 5/22). Выходы функциональных преобразователей 18 и 22 соединены соответственно с первым и вторым входами третьего вычитателя 26, выход ко0 торого соединен со вторым входом третьего перемножителя 27, первый вход которого соединен с шиной коэффициента адаптации 28, а выход подключен к соединенным вторым входам блоков деления 19 и 23. Блоки

5 вычисления коэффициентов 291-294N каждый содержит последовательно Соединенные четвертый перемножитель 30, пятый сумматор 31, пятый перемножитель 32, второй вычитатель 33, также содержит по0 следовательно соединенные шестой перемножитель 34, шестой сумматор 35, седьмой перемножитель 36, выход которого соединен со вторым входом вычитателя 33, выход которого соединен со входом интег5 ратора 37, подключенного выходом ко входу элемента памяти 28, также содержит восьмой перемножитель 39, выход которого соединен со вторым входом сумматора 35, а выход второго перемножителя 40 соединен

0 со вторым входом сумматора 31, Вторые входы перемножителей 32, 40, 30, 39, 34, 36 соединены соответственно с первым, вторым, третьим, четвертым, пятым и шестым входами блока 29n (,4N, а первые входы

5 перемножителей 40, 39, 30 и 34 соединены соответственно с первым, вторым, третьим и четвертым дополнительными входами блока 29П, причем вход сброса интегратора 37 соединен со входом сброса блока, а вход записи элемента памяти 38, соединен со

входом записи блока, при этом его выход соединен с выходом ячейки 38. Первые входы блоков соединены и подключены к выходу блока 19. Шестые входы блоков 29i-2§4N также соединены и подключены к выходу блока 23. Вторые входы блоков 29i- 29aN соединены и подключены к первому входу блока 15. который через первый инвертор 41 подключен к соединенным третьим входам блоков 292N+1-294N, пятые входы которых соединены и подключены к выходу второго инвертора 42. вход которого соединен с первым дополнительным входом блока 15, а также с соединенными четвертыми входами блоков 29i-29aN. третьи входы которых соединены и подключен ко второму входу блока 15, к которому также подключены соединенные вторые входы бликов 292N-H 294N четвертые входы которых сое- .динены, подключены ко второму дополнительному входу блока .15, а также к соединенным пятым входам блоков 29i- 292N. Первые и вторые дополнительные входы блоков 291-294N подключены к первой входной шине отводов блока 15, соединенной с первой выходной шиной отводов блока 1, при этом первые дополнительные входы блоков 29i-292N подключены к отводам линии 2, начиная с номера (-N) со сдвигом на один отвод, т.е. первый дополнительный вход блока 29i подключен к указанному выше отводу блока 292 - к .следующему и так далее, причем первый дополнительный вход блока 29ы+1 подключен не к отводу с нулевым номером, а к следующему, имеющему порядковый номер 1 и так далее, вновь по порядку, до отвода с номером N. Вторые дополнительные входы блоков 291-292N аналогичным образом подключены к отводам линии задержки 2 начи- ная с номера отвода (-N+L) по (N+L) включительно, причем пропущенным оказывается отвод с номером L Первые и вторые дополнительные входы блоков 292N+1-294N соединены с соответствующими входами блоков 29i-292N. Третьи и четвертые дополнительные входы блоков 29i-29qN подключены ко второй шине отводов блока 15, соединенной со второй выходной шиной отводов блока 1, при этом третьи и четвертые дополнительные входы блоков 29i-292N, аналогично подключению соответственно первых и вторых дополнительных их входов к отводам линии 2, подключены к отводам соответствующих номеров Линии задержки 3. Третьи и четвертые дополнительные входы блоков 202м+г- 294N соединены с соответствующими входами блоков 29i-292N. Таким образом

первые и вторые дополнительные входы блоков 291-294N присоединены к отводам линии 2, обеспечивающим взаимную задержку сигналов на интервал Т0 L A tic, где

Atk - интервал между котельниковскими отсчетами, а третьи и четертые дополнительные входы указанных блоков присоединены к отводам линии задержки 3, также обеспечивающим взаимную задержку сигналов на

0 указанный интервал. Выходы блоков 29i- 292N подключены к первой управляющей шине блока 15, соединенной с первой шиной управления блока 1; причем подключение выходов блоков 29П ко входам

5 аттенюаторов 4П выполнено в соответствии с их номерами. Управляющие входы аттенюаторов 42N+1-44N подключены к соответствующим управляющим входам аттенюаторов 41-42N по алгоритму: (2N+ 1) с 1-м, (2N+2)eo

0 2-м и так далее. Выходы блоков 292N r-294N подключены ко второй управляющей шине блока 15, соединенной со второй шиной управления блока 1, причем подключение выходов блоков 29П ко входам дополнитель5 ных аттенюаторов 10п выполнено в соответствии с их номерами. Управляющие входы аттенюаторов lOt-TOzN подключены к соот1- ветствующим управляющим входам аттенюаторов 102N+r 104N по алгоритму (2N+1) с 1-ым, (2N+2) со 2-м итак далее. Блок такте0 вой синхронизации 43, вход которого соединен с третьим дополнительным входом блока 15, через последовательно соединенные од- новибратор 44 и формирователь узкого импульса 45 подключен к соединенным входам

5 записи блоков 291-294N. входы сброса которых также соединены и подключены через элемент задержки 46 к выходу одновибрато- ра 44, причем выходы блока 1 соединены с соответствующими входами блока 15. .

0 Рассмотрим алгоритм работы заявляемого корректора. ..

Передаваемый сигнал на интервале , длительностью Т определяется выражением:

м

S(t) 2 ай sin ((От + m 1

+a)t+rf),...

0)

где ЗпЯ, фт ® - информационные амплитуда и фаза m-й составляющей; I - номер позиции сигнального кода г)ри амплитудно- фазовой манипуляции (при многократной фазовой манипуляции arn const; 1рт,а)т- начальная фаза и частота m-й составляющей; ft - сдвиг спектра многочастотного

сигнала. Выражение (.1) эквивалентно следующему:S (t) - х (t) cos Ш + xr (t) sin Ц; (t):

xltl-Sa ein JjV Vn.)-,.

r«M M

.(a

J«).

M Saln/cosfcOmbtfVv,)...

m-i

Здесь x(t) S(t, QC - 0), т.е. групповой сигнал, в котором сдвиг спектра равен нулю; Xr{t) - преобразование Гильберта от сигнала x(t) (преобразователь Гильберта - это широкополосный фазовращатель на 90°; для получения выражения xr(t) из x(t) необходимо аргумент каждой из гармоник изменить на 90°). Для коррекции сигнала со сдвигом спектра необходимо использовать, наряду с S(t), и преобразование Гильберта Sr(t) от S(t). Выражение Sr(t) на длительности такта Т, определяемое с помощью формул (1) и (2), имеет вид:

Srft) xr(t)-cos Qfct-x(t)- sinflfct...-(3) В системах связи, использующих мно- гочастотный сигнал, интервал между частотами соседних составляющих (ft)m . -.(От - ) выбирается так, что на интервале Т0 :ЈТ составляющие процесса х(т)(или xr(t) взаимно ортогональны. Для уменьше- ния влияния межсимвольных искажений интервал Тзи Т - Тд, называемый защитным интервалом, должен составлять некоторую часть Т, в частности, в многолучевых каналах Тзи выбирают так, чтобы многолучевой . разброс (т.е. максимальное значение задержки или опережения бокового луча относительно основного) не превосходил Тзи (лучи, которые порождают копии сигнала), отличные от копии основного луча, являют- ся боковыми); границы посылок в основном (т.е. наиболее мощном) луче определяет система тактовой синхронизации. Реализуемый в заявляемом корректоре алгоритм настройки использует свойство многоча- стотного сигнала, появляющееся в «нем с введением защитного интервала, именно: при выполняющемся условии взаимной ортогональности составляющих процесса x(t) (и xr(t) отсчеты x(t) и xKt). расположенные в пределах одной посылки, удовлетворяют одному из условий: либо x(t) - x(t + Т0); Xr(t) xi(t + То), либо x(t) -x(t + To); xr(t) - xKt + +To). Считаем для определенности, что выполнено первое из условий:. x(t) x(t + T0);xr(t) Xr(t + To) (4) Если обозначить число отсчетов (К6- тельнмковскйх) на интервале посылки Т через К, а на интервале Т0 - через L, то

указанное свойство для сигнала, заданного формулой (1) (т.е. в отсутствие искажений), можно записать в эквивалентной форме:

. 0-1 (K-L+K-dL, X t (t.+L)-x(t))l2 +

l 1 KqlL, J. + Xr(t|+L)P-Xr(t|)f 0... (5)

Значения x(t) и xr(t) не наблюдаются, т.е. не измеряются, однако x(t) и xr(t) связаны на интервале посылки однозначными соотношениями (2) и (3) с наблюдаемыми процессами S(t) и Sr(t). Из (2) и (3) следует:

x(ti) xi Sicos Siti-Si.r.slnQ; ti... (6) Xr(ti) xi.r Sisin Qfcti + Si.rcos Q;ti... (7)

где Si S(ti); Si.r - Sr(ti).

Подставляя выражения (6) и (7) в (5), получим:

О-Г ( г.

S .

Т

snu,r 5;,r) co5rt+(5 b-4r 55 b/5i)-5 n lii0

(8)

где а - О;Т0. Выразим далее значения cos a и sin а через отсчеты группового сигнала на интервале посылки. Из формул (2) и (4) следует:

SRL Sicos a + Si.r sin a... (9)

Из формул (3) и (4) следует:

Si+u -Sisln a + Sl.rcosa.... (10)

Поделив (9) на (10), получим уравнение, из которого найдем:

д-Sl+L Si .г-S| S|+L,r Т1 , .

Ща Si+L-Si+S,+L.r-S,,(11) n Si-t-L -Su-Si -SH-LK

-Sl + Si+Ur Si.r

Из (11) следует: со5 o ra/Vri2 +Г22 ; sin a n/Vri2 +Г22 ...(12)

Подставляя выражения cos а и sin a из (12) в выражение, заключенное в квадратных скобках формулы (8), получим:

СЗии- б УсодК би Б -З -б;)

efjCOSM r,sinoi -Jr -r « ylSuu + SaL.rl t5; 5;.rJ - 113)

Подставляя (13) в (8), получим:

Q-l (VC-U+Kij,

s z-- ()0

v--°;- x(

Выражение (14) означает следующее: если для многочастотного сигнала выполняется соотношение (4), то аналогичное соотношение выполняется для огибающей указанного сигнала при любом сдвиге спектра (величина Vsf + SiTT- это огибающая многочастотного сигнала в момент T.R). Таким образом, в отсутствие искажений левая часть (14) равна нулю. С появлением частотных искажений при подстановке в левую часть фактических значений сигнала Јi и Јi,r (измеренных на выходе канала связи с искажениями), соотношение (14) нарушается. В качестве критерия качества настройки корректора принимаем следующий критерий, вытекающий из (14): оптимальным является такой набор коэффициентов настройки корректора; который минимизирует величину

(к-Жк .

2Z Ц

Ul4-Ka. Л

Јг А-г

SinA+U

1Л г г .r.-l|5NS:

i.i

(

-V .

где S(t) и Sr(t) - оценки соответственно сигнала и его преобразования Гильберта на выходе корректора. Полагаем, что коррекция осуществляется комплексным гармоническим кбрректором (представляющим собой при цифровой обработке комплекс- цый уерекурсивный фильтр), так что оценки S(t), Sr(t) определяются выражением:

()(АТ ;-ВтЫ

; .+№T j1r+Bi: iV-W .

где J - мнимая единица, Ат a-N, .... Эо, .... ам - (2м+1) - мерный вектор-строка первой (действительной) части корректора;

Вт Ь-м,..., bo,..., (2Ы+1)- мерный вектор-строка отводов второй (мнимой)

части корректора; If ЈI+N, .... §, .... |i - N (2N+1) - мерный вектор-строка отсчетов входного сигнала;

|fr tli.+ N,r, ...,Јl,r, .... |i-N,(2N,1)

- мерный вектор-строка отсчетов процесса на выходе широкополосного преобразователя 12, верхний индекс Т у вектора - это

обозначение операции транспонирования вектора.

Непосредственной проверкой устанавливается, что матрица вторых производных 5 от (15) по вектору (А - IB) является положительно определенной формой (при наличии искажений), поэтому (15} имеет единственный минимум при (Ао + jBo) 0.

Для получения решения, отличного от 10 нулевого, представ искомый вектор в виде: А. An + а0; В Bn + bo. где An - (2N+1) - мерный вектор, отличающийся от Д тем, что центральный его отвод р авен нулю; 1о - (2N+1)-MepHbiu вектор, центральный отвод 15 которого равен а0, а все остальные равны нулю.

Аналогично определяются Ви и В0. Полагаем далее, что модификацмям под верга- ются отводы векторбв Аи и Ви, а а0 и bo, т.е. 20 центральные отводы обеих частей корректо ра в процессе настройки корректора остают ся.неизменными, при этом оценки Si и 5|,гиз (16) записываются в виде:

25 .si(AJ-S -Bl-§ )r + (eo-e-boS.r);

S,,r (Aj-||J r + ) +

30 +(а0-§.г + Ьо §) ....(17)

где |Р - (2N+1) - мерный вектор, отличающийся оту|| тем, что 1-я координата равна нулю; аналогично определяется и вектор 35 |V

Для определения Аи, опт и Вц.опт ис- пбльзуём стохастическую аппроксимацию градиентного алгоритма. Полагаем, что модификация коэффициентов осуществляется на каждой посылке, так что усреднение на посылках в (15) можно исключить. Выполняя дифференцирование (15) с учетом (17) соответственно по Аиипо Ви, получаем алгоритм настройки корректора:

40

45

50

.. O Hjvpr e.lV l-a -f-S

(c1r Kt

;,,..,,«- Ji WtТ ....- -г-------7,оТ(

b.M- W-P;jS

«г ,r

«. «2 / u

,rj рг --; -- Гъ; ь

N5Ui.5;tUlP i

ЧцД -и-пЬдр (.)/

Алгоритм (18), (19) получен при условии, что для многочастотного сигнала выполняется соотношение (4). Алгоритм сохраняет форму (18), (19) и в случае, когда для многочастотного сигнала выполняется соотношение:

x(t) -x(t + To); xXt) - xKt + То).

Для устойчивости процесса адаптивной настройки коэффициент адаптации /г должен удовлетворять условию:

(к-и)-(2М + 1)-1Ј2,

где UЈ-дисперсия процесса |(t). Алгоритм (18), (19/ записан в форме, предназна- ченой для цифровой реализации.

Для аналоговой реализации алгоритм (18), (19) записывается в виде:

.-...-- i

MV )«o.W-|u {(|sW(tvrb)-(lb(

/|ррйпш ш .

xtsM-rtt-r. .« lVbWtf-H (() ) 1

.

iTOShra 1

(i - W$bs® x(-bH)(t-«-b4 SrW-(i-«4tO ldt,

(«

где т + kT - граница k-й посылки, определяемая системой тактовой синхронизации. Подстраиваемый по алгоритму (18), (19) вектор коэффициентов сходится к оптимальному значению, ебли искажения в канале не превосходит допустимы величин. Если обозначить через hk, hk отсчёты импульсной реакции канала связи, то, как показывают результаты моделирования, настройка корректора по алгоритму

(18). (19) улучшает характеристики систе- мы канал + корректор, если У VhtPf hl,r Vh0 + hor. Отметим, что

°

при коррекции многочастотного сигнала ре- .зульатты легко контролируются, для этого достаточно сравнивать уровни переходных шумов в одном из подканалов, свободных от сигнала, до коррекции и после коррекции.

Устройство работает следующим образом. Входной сигнал УПС со входной шины устройства поступает непосредственно на вход линии задержки 2 и через широкополосный фазовращатель 12 на вход линии задержки 3. Фазовращатель 12 изменяет фазу каждой из гармонических составляющих сигнала на 90°. Таким образом входные сигналы линий 2 и 3 в совокупности представляют собой комплексный входной сигнал устройства. На отводах линий 2 и 3 формируются сигналы, задержанные относительно предыдущего на интервал Atk между Котельниковскими отсчетами. 2N сигналов Ј(t + n Atk) отводов линии задержки 2 номерами п, симметричными относительно центрального имеющего нулевой номер, представляют собой 2Ы-мерный вектор входных сигналов: |uT(t)g(t + NAtk),..., . Ј(t.+ Atk),Ј(t-Atk),..,,(t-NAtk)J. Эти сигналы, через перемножители 7 аттенюаторов 101-102N, осуществляющие умножения сигналов отводов на исходные весовые коэффициенты отводов напряжения которых присутствуют .на шинах 5, причем исходные управляющие напряжения ыа вторых входах вычитателей б равны нулю, поступают на входы сумматора 9. Умножающие коэффициенты аттенюаторов 101-102N представляют собой 2М-мерный вектор весовых коэффициентов отводов7 первой (действительной) части комплексного корректора: Аит а-м, ..,., а-1, a+i, ..., ам. 2N сигналов. Јг (t) отводов линии задержки 3 с номерами п, симметричными относительно центрального, имеющего нулевой номер, представляяют : собой 2М-мерный вектор сигналов, сопряженных по Гильберту со входными:

l w-KrM KU.irrit- i.v,

(,...,Vr -N-bt,fl:

Эти сигналы через апенюаторы 42N+1- 44N, умножающие коэффициенты которых представляют собой 2М-мерный вектор весовых коэффициентов отводов второй (мнимой) части корректора Впт Ь-м, .... b-1, bi, ..., Ьы), поступают на дополнитель0

5

0

5

0

5

0

5

0

ные входы сумматора 9. Учитывая, что сигналы с центральных отводов линий 2 и 3, имеющих нулевые номера, поступают на входы сумматора 9 непосредственно, т.е. умножающие коэффициенты а0 Ь0 1. на его выходе в соответствии со вторым выражением (17), модифицированным для случая аналоговой обработки, сформирован выходной гильбертов сигнал корректора:

Sr(t)

)+ВпТ-Г (t) +

+ во -Јr (t)+bo Т

Аналогичным образом сумматор 8, обрабатывающий поступающие к нему через аттенюаторы 4i-42N (действительные коэффициенты) сигналы отводов линии 2, а также поступающие к нему через аттенюаторы 102N-M-104N (мнимые коэффициенты) и инверторы 1ti-tl2N сигналы отводов линии 3 (сигналов, сопряженных по Гильберту со входными), формирует в соответствии с первым выражением (17), модифицированным для случая аналоговой обработки, выходной синфазный сигнал корректора:

Sft) Г ()- 1)+ S(tj )-boMt)- В тот момент времени, когда с центрального отвода линии задержки 2 (третьего дополнительного выхода блока 1) снимается сигнал Ј (t), на выходе сумматора 8 формируется сигнал S(t), поступающий на линию задержки 13, задерживающую сигнал на время интервала ортогональности То. В это же время на вход линии задержки 14с выхода сумматора 9 поступает сигнал Sr(t). Таким образом через время, равное То, на выходе линии 14 появится сигнал ASr(t), на выходе линии 13 появится сигнал S(t), а на их входах (т.е. на выходах устройства) будут соответственна присутствовать сигналы Sr{t + То) и S(t + То). При этом на Центральных отводах линий задержки 2 и 3, имеющих нулевые номера, будут присутствовать сигналы Ј (t + То) и Јr{ t + То), а сигналы Ј(t) и Јr (t) при этом будут наблюдаться на отводах линий задержки 2 и 3, имеющих номер L, отстоящих от центрального на интервал ортогональности. Соответственно на первых отводах линий 2 и 3, имеющих номер (-N), будут наблюдаться

10 втором дополнительном выходах сформ рованы сигналы §r(t +T0) и St(t) соответ венно, а на первой и второй шинах отвод присутствуют сигналы Ј (t - nAtk) и i -пД tk) (n Ј 1.4N), соответствующие р

15 личным отводам корректора, а аткже сиг лы, запаздывающие относитель указанных на интервал ортогональнос | (t + То - п Atk) и Ј{t + То - n Д Квадраторы 16, 20, 24, 25, подключенны

20 первому и второму, а также к первому второму дополнительным выходам бло 1, возводят в квадрат указанные вы сигналы. Сумматор 17 формирует сигн S2(t + То) -t-JS/tt + То), а сумматор 21 с

blt+ 25 нал S2(t) + Sr2(t).

30

Функциональные преобразователи 18 и осуществляют преобразование у v5T формируют соответственно выходные с налы,пропорциональные

50

V

S2() + SE(t+T0)

35 vS2(t)(t).

На выходе вычитателя 26 сформиров разностный сигнал указанных выражений после перемножителя 27 он преобрета вид:

40 -(VS2(t+To) + a2(t+T0)-VS2(t)(t)) ,.

где/г определяется напряжением на ши коэффициента адаптации 28. Этот сигн поступает на вторые входы первого 19 второго 23 блоков деления и определяет н пряжение числителя. Для блока 19 напряж ние, пропорциональное знаменател

поступает с выхода функционального пр образователя 18, таким образом выходн сигнал блока 19 описывается выражение

nuivicy (, , паи/ичдаюим/ prff-------JTff----- Гл л5

§(t To 4-N-A tk) и &t + To + N 55 .(i|S() + SP(i+T0 --yIs (t + Sr(t))

сигналы

Atk), а на отводах, имеющих номер (-N+L), сигналы |(t + N Д tk) и |r (t + N Д tk) и так далее, причем на отводах линий задержки 2 и 3. имеющих номер (N) и соответствующих последним отводам расчетной

52U+T0 5(tfT0)

Аналогично с учетом того, что напряж ние знаменателя для блока 23 поступает

длины коррекора, будут наблюдаться сигналы Ј(t+ т° N Atk) и Јr (t + То - N Д tk), a на последних дополнительных отводах линий задержки с номером (N+L) будут наблюдаться сигналы Ј(t-N -Дт.|)и rft-N-Д tk). Таким образом в каждый момент времени t + T0 на первом и первом дополнительном выходах блока 1 сформированы сигналы §(t + To) и S(t); на его втором и

втором дополнительном выходах сформированы сигналы §r(t +T0) и St(t) соответственно, а на первой и второй шинах отводов присутствуют сигналы Ј (t - nAtk) и ii{t -пД tk) (n Ј 1.4N), соответствующие ра зличным отводам корректора, а аткже сигналы, запаздывающие относительно указанных на интервал ортогональности: | (t + То - п Atk) и Ј{t + То - n Д tk). Квадраторы 16, 20, 24, 25, подключенные к

первому и второму, а также к первому и второму дополнительным выходам блока 1, возводят в квадрат указанные выше сигналы. Сумматор 17 формирует сигнал S2(t + То) -t-JS/tt + То), а сумматор 21 сигblt+нал S2(t) + Sr2(t).

Функциональные преобразователи 18 и 22 осуществляют преобразование у v5T и формируют соответственно выходные сигналы,пропорциональные

V

S2() + SE(t+T0)

vS2(t)(t).

На выходе вычитателя 26 сформирован разностный сигнал указанных выражений, а после перемножителя 27 он преобретает вид:

-(VS2(t+To) + a2(t+T0)-VS2(t)(t)) ,.

где/г определяется напряжением на шике коэффициента адаптации 28. Этот сигнал поступает на вторые входы первого 19 и второго 23 блоков деления и определяет напряжение числителя. Для блока 19 напряжение, пропорциональное знаменателю,

поступает с выхода функционального преобразователя 18, таким образом выходной сигнал блока 19 описывается выражением:

52U+T0 5(tfT0)

Аналогично с учетом того, что напряжение знаменателя для блока 23 поступает от

15. 1807571 16

преобразователя 22, определяется и выход-При этом перемножите ль 40 формирует

ной сигнал блока 23:на выходе сигнал: Sr{t + ) Ј(t + Т0 - ni :...., г, Atk), перемножитель 30: S(t +До). То. AIУ5(tvT0}4s()- -jЈ2(t) 5 (t)) .-n Atk), перемножитель 39: Sr(t) § (t- n

K Atk), а перемножитель 34 сигнал: (S(t)

: H5ttv

11 Јa (tl n Atk). Далее работа второй половиt ны блоков модификации аналогична опиТаким образом, в соответствии с алго-саннбй выше, т.е. на выходах вычитэтелей

ритмами (18) и (19) на первом входе каждого33 данной группы присутствуют напряжеизблоков291-294N сформировано напряже-10 ния, пропорциональные суммируемому выние, пропорциональное умножаемому ко-раже кию правой части алгоритма (19),

эффициенту перед первой внутреннейсоответствующее обработке в момент врекруглой скобкой, а на шестом входе каждо-М6ни г+Т0 сигнала данного n-го отвода. Блок

го из указанных блоков сформированотактовой синхронизации 43, анализируя

напряжение, пропорциональное умножае-15 сигнал на нулевом отводе линии 2, отмечает,

мому коэффициенту перед второй внутрен-например, в некоторый момент времени наней круглой скобкой. вчало тактового интервала. При этом на выКак упоминалось выше, по шинам отво-,ходе одновибратора 44 появляется нулевой

дов на первый и второй дополнительныеимпульс, задерживаемый на небольшой инвходы каждого m-го блока 29т (т 6 1,4NJ20 тервал в элементе задержки 46. Длительпоступают разнесенные на интервал ор-ность сформированного импульса равна

тогональности сигналы с бтводов линииинтервалу Тзи Т - Т0 (К - L отсчетных

2: §(t + То - n A tk) и § (t - п1 A tk),интервалов, где К - число котельниковских

соответственно на третьем и четвертом До-отсчетов на интервале длительности посылполнительных входах данного блока будут25 ки). При этом интеграторы 37 в блоках 29iприсутствовать сигналы r(t+ Т0 - n-A tk)294N переключаются из режима сброса в

И r(t-n Atk) с отводов линии задержки 3.режим интегрирования и осуществляют на

Блоки 291-292N, на второй, третий, четвер-протяжении указанного интервала накоплетый и пятый входы котррых поступают сеют-ниё выходных сигналов вычитателей 33, ТаffeTCTBeHHO сигналы: S(t + Т0), or(t + То), S(t),30 ким образом к концу защитного интервала

r(t), осуществляют обработку в соответст-в интеграторах 37 блоков соответбии с алгоритмрм (18). На выходе перемно-ственно номерам обрабатываемых отводов

жителей 40, 30, 34, 39 сформированынакоплены напряжения пропорциональные

сигналы соответственно. вычитаемому выражению правой части (18),

А .35 а в интеграторах 37 блоков 292N+1-294N

S (t -ЬТо) §(t +Т0 - n Atk) Iнакоплены соответствующие напряжения,

.- хпропорциональные вычитаемому выраже Sr(t Ч-То) §(t + То n Atk) i .нию правой части (19). Благодаря тому, что

л .сигнал интегрирования с выхода одновибSr (t) vЈr(t - n Atk) ;40 ратора 44 задерживается в элементе заА .; ....держки 46, узкий импульс с выхода

S (t) §.(t - П Atk) .формирователя 45, появляющийся в мо.мент прохождения положительного фронта

Сумматор 31 объединяет первые дваимпульса одновибратора 44, поступает на

сигйала, а сумматор 35 - вторую пару, фор-45 управляющие входы элементов памяти 38

мМруя сигналы, описываемые первой и вто-непосредственно перед переключением инрой внутренними круглыми скобкамитеграторов 37 в режим сброса, в результате

алгоритма 918). В перёмножителях 32 и 36чего накопленные интеграторами напряжеосуществляются умножения на сформиро-ния фиксируются в элементах памяти 38. G

ванные, как показано выше, напряжения50 выхода ячейки 38 этот сигнал по первой

умножающих коэффициентов, а на выходевыходной шине управления блока 15 от кажвычитателя 33 формируется напряжение,дого из блоков 291-292N поступает на управггропорциональное суммируемому выраже-ляющие входы пары аттенюаторов из числа

нию в правой части (18). Блоки 292N+1-294N,4i-44N, обрабатывающих сигналы n-х отвона второй, третий, четвертый и пятый входы55 дов линий задержки 2 и 3, а по второй выкбтцрых поступают сигналы соответствен-ходной шине управления блока 15 от

но: Sr(t + То); S(t + Т0); Sr(t); -S(t), осуще-каждого из блоков 292N+1-294N поступает на

ствляют обработку в соответствии суправляющие входы пары аттенюаторов из

алгоритмом (19).числа Ют-Юзм, также обрабатывающих сигналы отводов, имеющих указанный номер п. Посредством вычитателя 6, входящего в состав каждого аттенюатора, выходной сигнал блока обработки вычитается из первоначально установленных на шинах 5 исходных значений коэффициентов отводов по алгоритму:

an(1) an(0)- AI; ,

an(2)-an(l)- Д an(0)-(Ai + Л);

an(q+1) an(0)-( Ai + ; . . +Дд + 1)(при- мер для описания работы аттенюаторов 4i- 44N). Отсюда следует, что в элементах памяти 38 блоков 29-I-294N осуществляется накопление напряжений, отображащих необходимые изменения весовых коэффициентов ап и bn комплексного корректора. Из

описанного алгоритма работы устройства следует, что время выполнения одной итерации равно тактовому интервалу, а скорость сходимости итерационного процесса задается выбором коэффициента адаптации ft.

Основным преимуществом заявляемого устройства по сравнению с прототипом явсляется инвариантность процесса и результата коррекции относительно сдвига спектра. Это значит, что процесс коррекции не зависит от наличия и величины сдвига спектра. Прототип функционирует только

при условии, что сдвиг спектра предварительно сведен к нулю.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор | 1986 |

|

SU1319295A1 |

| Адаптивный корректор искажений каналов передачи данных | 1982 |

|

SU1083372A1 |

| Устройство для селекции сигналов заданной формы | 1977 |

|

SU733097A1 |

| Цифровой адаптивный корректор сигналов многократной фазовой модуляции | 1981 |

|

SU1012445A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

| Устройство для полосовой адаптивной коррекции сигналов относительной фазовой модуляции | 1982 |

|

SU1100736A1 |

| Адаптивный рекурсивный фильтр | 1979 |

|

SU813705A1 |

| Нелинейно-нелинейный корректор коррелированного сигнала | 1984 |

|

SU1225017A1 |

| Устройство для селекции сигналовзАдАННОй фОРМы | 1979 |

|

SU834879A2 |

| Устройство для моделирования многолучевого радиоканала | 1984 |

|

SU1224810A1 |

Изобретение относится к технике передачи дискретной информации по каналам электросвязи и может быть использовано в многоканальных модемах с ортогональными составляющими для коррекции сигнала. Целью изобретения является обеспечение коррекции при наличии частотного сдвига спектра корректируемого сигнала. Адаптивный корректор содержит блок адаптивной коррекции 1 и блок управления 15, причем блок 1 включает линии задержки 2, 3, 13, 14 аттенюаторы 4i-44N, 10i-104N, шину начального значения умножающего коэффициента отвода 5, вычитатель 6, перемножитель 7, сумматор 8, 9, инверторы 2 111-112N, широкополосный фазоврэщатель 12, а блок управления 15 включает квадраторы 16, 20, 24, 25, сумматоры 17,27, 31,35, функциональные преобразователи 18, 22, блоки деления 19, 23, вычита тели 26, 33 перемножители 27, 30, 32, 34, 36, 39, 40, шину коэффициента адаптации 28, блоки вычисления коэффициентов 29i-294N, интегратор 37, элемент памяти 38, инверторы 41, 42, блок тактовой синхронизации 43, одновиб- ратор 44, формирователь узкого импульса 45, элемент задержки 46. Для настройки гармонического корректора используется Свойство многочастотного сигнала с ортогональными составляющими, обусловленное наличием е нем активных защитных интервалов. Коэффициенты передачи аттенюаторов в цепях отводов от линии задержки настраиваются таким образом, чтобы минимизировать среднеквадратическое отклонение пар значений огибающей сигнала, расположенных на одной посылке и удаленных друг от друга на интервал ортогональности. Алгоритм настройки корректора, в основе которого лежит сопоставление пар значений огибающей, является инвариантным относительно частотного сдвига спектра сигнала. Настройка корректора осуществляется без использования решений из демодулятора, что упрощает настройку корректора и эксплуатацию приемной части устройства обработки в целом. 1 ил. Ј 00 о х| СЛ XI

Формула изобретения Адаптивный корректор многоканального сигнала с ортогональными составляющими, содержащий блок адаптивной коррекции, включающий первую и вторую линию задержки, 2 N отводов каждой из которых через соответствующий аттенюатор подключены к входам соответственно первого и второго сумматоров, причем каждый аттенюатор состоит из первого перемножителя, выход которого является выходом аттенюатора, первый вход - входом аттенюатора, а второй вход подключен к выходу первого вычитателя, один из входов которого является входом сигнала начального значения коэффициента умножения, а второй вход - управляющим входом аттенюатора, при этом выходы первого и второго сумматоров являются соответственно первым и вторым выходами блока адаптивной коррекции и адаптивного корректора, а также блок управления, включающий две группы по 2N в каждой блоков вычисления коэффициентов, каждый из которых состоит из второго перемножителя и последовательно соединенных интегратора и элемента памяти, выход которого является выходом блока вычисления коэффициентов, кроме того, блок управления включает третий перемножитель, первый вход которого является входом сигнала коэффициента адаптации, при этом выходы первой группы блоков вычисления коэффициентов объединены и являются первым выходом блока управления и. подключены к управляющим входам аттенюаторов, а выходы второй группы блоков управления объединены и являются вторым выходом блока управления, отличающийся тем, что, с целью

обеспечения коррекции при наличии частотного сдвига спектра корректируемого сигнала, в блок адаптивной коррекции введены дополнительные аттенюаторы, третья и четвертая линии задержки и широкополосный фазовращатель, а в блоке управления в каждый блок вычисления коэффициентов введены четвертый, пятый, шестой, седьмой и восьмой перемножители, второй вычита- тель и третий и четвертый сумматоры, кроме того, в блок управления введены первый, второй, третий и четвертый квадраторы, четвертый и пятый сумматоры, первый и второй инверторы, первый и второй блоки деления, третий вычитатель, первый и второй функциональные преобразователи, формирователь узкого импульса, одновибратор, блок тактовой синхронизации и элемент задержки, при этом в блоке адаптивной коррекции вход первой линии задержки является входом блока адаптивной коррекции и входом адаптивного корректора и через широкополосный фазовращатель подключен к входу второй линии задержки, дополнительные 2N отводов первой линии задержки через соответствующие дополнительные аттенюаторы подключены к дополнительным входам второго сумматора, центральный отвод подключен непосредственно к соответствующему дополнительному входу второго сумматора, дополнительные 2N отводов второй инии задержки подключены через последовательно соединенные дополнительный аттенюатор и инвертор к соответствующим дополнительным входам первого сумматора, центральный отвод второй линии задержки подключен через соответствующий инвертор к соответствующему допол нител ь- ному входу первого сумматора, управляющие входы дополнительных аттенюаторов объединены и подключены к второму выходу блока управления, при этом вход первого сумматора подключен к первым входам вто- рых перемножителей первой группы блоков вычисления коэффициентов, через первый инвертор - к первым входам вторых перемножителей второй группы блоков вычисления коэффициентов и через первый . квадратор - к первому входу четвертого сум- матора, выход первого сумматора подключён к входу третьей линии задержки, выход которой соединен с первыми входами восьмых перемножителей первой группы блоков вычисления коэффициентов, через второй инвертор-с первыми входами восьмых перемножителей второй группы блоков вычисления коэффициентов и через второй квадратор с первым входом пятого сумматора, дополнительные отводы, кроме цент- рального. первой линии задержки подключены к вторым входам второго и восьмого перемножителей соответствующих блоков вычисления коэффициентов, выход второго сумматора подключен к первым входам четвертых перемножителей каждого блока вычисления коэффициентов, через четвертый квадратор - к второму входу четвёртого сумматора и через четвертую линию задержки - к первым входам шестых пере- множителей всех блоков вычисления коэффициентов, выход четвертой линии задержки через третий квадратор подключен также к второму входу пятого сумматора, дополнительные отводы, кроме центрального, второй линии задержки подключены к вторым входам четвертого и шестого перемножителей соответствующих блоков вычисления коэффициентов, кроме того в блоке управления выход четвертого сумматора соединен со входом первого функционального преобразователя, выход которого подключен к первому входу третьего вычитателя и через первый блок деления - с первыми входами пятых перемножителей всех блоков вычисления коэффициентов, выход пятого сумматора соединен с входом второго функционального преобразователя, выход которого подключен к второму входу третьего вычитателя и через второй блок деления - к первым входам седьмых перемножителей всех блоков вычисления коэффициентов, выход третьего вычитателя через третий перемножитель подключен к вторым входам первого и второго блоков деления, центральный отвод первой линии задержки соединен с входом блока тактовой синхронизации, выход которого соединен с входом одновибратора, выход которого подключен через элемент задержки к входам записи элементов памяти всех блоков вычисления коэффициентов и через формирователь узкого импульса - к входам сброса интеграторов всех блоков вычисления коэффициентов, при этом в каждом блоке вычисления коэффициентов выходы второго и четвертого перемножителей соединены через третий сумматор с вторым входом пято- г-о перемножйтеля; выходы шестого и восьмого перемножителей соединены через четвертый сумматор с вторым входом седьмого перемножителя, а выходы пятого и седьмого перемножителей подключены через второй вычитатель к входу интегратора.

| С.А.Курицын и др, Оптимальный адаптивный прием многоканальных сигналов | |||

| Техника средств связи, .серия ТПС, 1984, вып | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для испытания прессованных хлебопекарных дрожжей | 1921 |

|

SU117A1 |

| С,А.Курицын и др | |||

| Адаптивная коррекция полосового сигнала в многоканальном УПС | |||

| Техника средств связи, серия ТПС, 1987, вып.4, с.73-82. | |||

Авторы

Даты

1993-04-07—Публикация

1990-10-05—Подача