У1.а;. , i.i,; ,},

( «.. cJet

IJ

,«() q(k-.)

j (k-ir

ЧгО (k-ij

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматического регулирования частоты и перетоков активной мощности в энергосистеме | 1982 |

|

SU1089698A1 |

| Адаптивное устройство для идентификации линейных объектов | 1988 |

|

SU1520478A1 |

| Телеизмерительная система | 1983 |

|

SU1161981A1 |

| АДАПТИВНАЯ СИСТЕМА ТЕРМИНАЛЬНОГО УПРАВЛЕНИЯ | 2012 |

|

RU2500009C1 |

| Дискретная самонастраивающаяся система | 1979 |

|

SU824139A1 |

| Устройство для магнитно-импульсной обработки деталей | 1973 |

|

SU470251A1 |

| Адаптивный измеритель параметров сигнала | 1981 |

|

SU970251A1 |

| Система идентификации параметров линейных объектов | 1988 |

|

SU1534429A1 |

| Устройство для формирования сигнала управления с оптимальными коэффициентами обратной связи | 1984 |

|

SU1242913A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

Изобретение относится к системам управления динамических объектов, а именно объектов с постоянными во времени параметрами. Целью изобретения является повьшение точности управления конечным состоянием динамического объекта. Система последовательного финитного упракпения содержит объект управления 1,блок исполнительных органов 2, блок датчиков состоя- ния 3, первый блок 4 источников . тоянных напряжений, блок 5 вычисления, коэффициентов передачи, запоминающий элемент 6, ключ 7, первый инвертор.. 8, второй блок 9 источников постоянных напряжений, блок 10 запуска, первый 21, второй 20, третий 11, четвертый 19 и пятьй 15 блоки матричного умножения, сумматор 12,. первый блок 13 формирования переходной матрицы объекта, блок 14 запоминающих элементов, таймер 16, второй инвертор 17, блок 18 матричного вычи- , тания, второй блок 22 формирования переходной матрицы объекта, элемент 23 задержки. 1 з.п. ф-лы, 7 ил.

(i-Kh {i-){j-4)

r

n-k, 1(cf,f,

h-3

П a

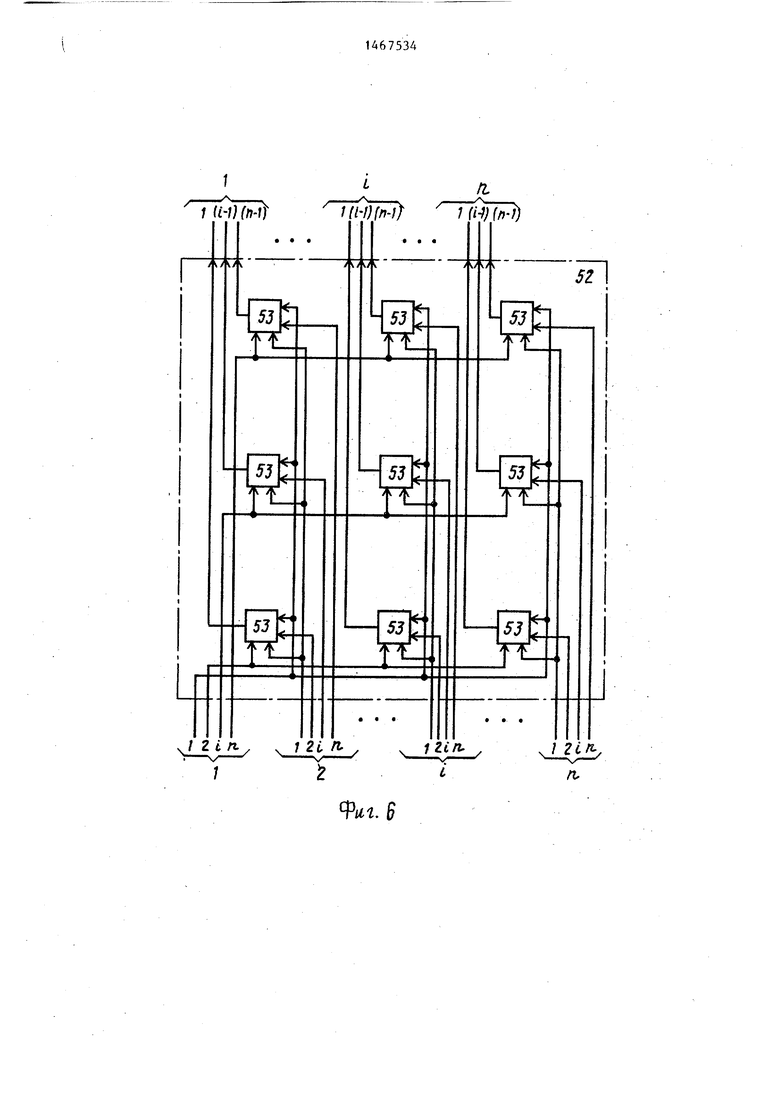

Матрицы A (k 1, n -1) реализу- ЮТСЯ блоками понижения порядка соответственно с номерами п - k, т.е. блок 55 реализует матрицу , , а блок п - 1 реализует матрицу А,, АО А - исходная матрица, детерминант которой определяется.

Известно, что матрица, обратная матрице А при условии ее невырожденности (det А 0), определяется выражением

detCAl П i 1, п; j In, где С ,j (-1) -М;- - алгебраические

дополнения;

detB,jtn-1 ,п-1 - миноры (определители мат- риц, полученны из исходной . матрицы путем вьтеркивания соответственно i-й и j-ro столбца.

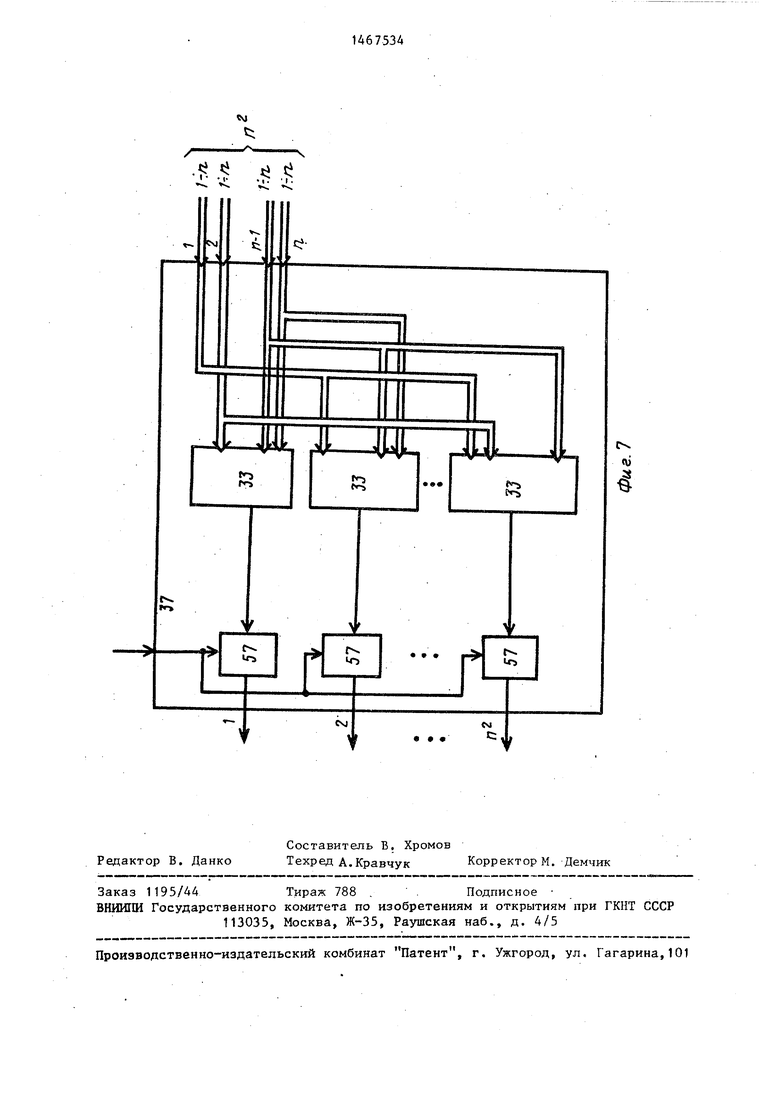

Функциональная схема блока обращения матриц представлена на фиг, 7. Данный блок состоит из п блоков вычисления определителей 33 и п делителей 57. Причем значения миноров формируится на выходах блоков вычисления определителей, а алгебраические дополнения формируются за счет использования инверсньгх входов делителей для i и J, образующих в сумме нечетное число.

n 7, 3 ,

25

30

5

0

5

0

5

Пусть объект управления описывается векторно-матричньгм уравнением вида . ,

X Ах f Ни,(1)

где X {x,,.,nj - вектор состояния;

А - матрица объекта; В . - матрица управL i J

ления,

(; J вектор управляющих параметров,

и требуется его к моменту времени Т перевести из состояния x(to) х в состояние х(Т). Один из законов финитного управления конечным состоянием имеет вид

u(t),,t)R- (T,t,)0(.to,T)- - x(to) ,(2)

где O(t,,t)

(t ,, t - переходная Фундамен- тальная) матрица системы, которая может быть представлена в виде матричной экспоненты

Ф(t,,t,)

Т

Ё(т, to) 5 o(to,-: )вв Ф(to,c)d г. в

Поскольку для произвольного текущего состояния x(t) решение системь: (1) относительно терминальной точки может быть представлено в виде

х(т) Ф(т,t)x(t) + U(T,i:)Bu(c)dt:,

t(3)

a также

ф(Т, t)

TO данное интегральное уравнение может быть переписано в виде системы порядка пет неизвестнь11 и (п / т) -Л Г„. .. --At.

5 ()d х(Т) - (t).

t(4)

Данной системе, как несложно проверить простой подстановкой, удовлетворяет решение вида

u(f)(T,-t) )

-AT . .-, - е x(t)J ,

(5) (6)

.где R(T, t) e BB e Mt,.

t В Данном соотношении моменты С и t

могут не совпадать (Т Ч t) вследствие того, что в измерительном тракте присутствует запаздывание dt Г- t. Здесь С - текущее время, at- момент времени, на который приходится используемая текущая информация x(t) о состоянии объекта.

Закон управления (5) в отличие от

R(ll,t) ARC-J, t) + R(, t) (

при R(t, t) 0, Сб t, T или, что то же, 2 е Со, Т.,- t .

Следует отметить, что для полностью управляемых динамических систе матриц .R(t,, ti) является всегда неособой за исключением случая t, t. Однако следует учесть, что в момент времени t Т матрица R вырождается, и от нее не может быть взята обратная. В связи с этим при

20

25

закона (2) позволяет не только учесть ° реализации необходимо: вести контзапаздывание в информационном тракте, но и корректировать управление с учетом прогноза движения объекта из точки x(t) вточку х(Т) строго за заданное время Т, т.е. осуществлять после- довательное финитное управление конечным состоянием.

Основными сложностями в реализации закона (5) в общем случае являются: формирование переходной матрицы Ф(0, €) Ф Ч, 0) для разных значений t, формирование матрицы R(T, t) для разных значений t, формирование матрицы R XT, t) - обращения матриц.

Следует иметь в виду, что е g ДИ;) т.е. в данном случае обращение матрицы не требуется. Кроме

е

fii

I

SiT

(At) - может

быть представлено бесконечным-рядом, где I - единичная матрица. Однако в технической реализации можно ограничиться некоторым усечением данного ряда. В частности-, погрешности от приближенного задания матрицы

,Л

легко интерпретируются в пог

решности прогноза движения объекта

5

146753А6

на заданном интервале управления ,0,.Т. В этой связи всегда может быть задано некоторое число S -с 1 , такое, что усечение ряда считается

удовлетворительным при выполнении условия

(I

ettjlle ll)/ ,

Ai где е ,,

1

(7)

I +Z (At) ,

1-1 1 а II- И - норма матрицы.

Матрица R(T, t) определяется соотношением (6). Однако процедура вьии- сления данного интервала может быть заменена процедурой решения дифференциального уравнения

R(ll,t) ARC-J, t) + R(, t) (8)

при R(t, t) 0, Сб t, T или, что то же, 2 е Со, Т.,- t .

Следует отметить, что для полностью управляемых динамических систем матриц .R(t,, ti) является всегда неособой за исключением случая t, t. Однако следует учесть, что в момент времени t Т матрица R вырождается, и от нее не может быть взята обратная. В связи с этим при

роль детерминанта. Общим правилом обращения квадратной матрицы п х п является

д-1 IГг.

j«4-T

Т n

detA

где С,-; (-1)- М,-,-

0

M;J detB.jCn-1, n-1

дополнения;

5

0

миноры (определители матриц, полученных из исходной матрицы путем вычеркивания соответственно i-й строки и j-ro столбца).

Закон управления (5), (8) объектом (1) реализуется устройством, представленным на фиг. 1, следующим образом. Значения элементов матриц В и А объекта управления (1) формируются соответственно на m х п выходах первого 4 и п выходах второго 9 блоков источников постоянных напряжений. Требуемое время Т завершения переходного процесса вводится перед началом этапа управления и фиксируется в зппоьпшающем элементе 6, Вектор х(Т), используемый ДЛ5Г прогноза невязки требуемого конечного состояния, формируется на выходе блока 11, вводится и фиксируется в блоке 14 запоминающих элементов, содержащем п запоминаюищх элементов и имеющем столько же выходов.

Таймер 16 предназначен для форми- д рования значений текущего времени управления. Блоки 13 и 22 в соответствии с выражением (7) формируют на своих п выходах текущие значения переходной матрицы системы (1). Блок j 5 вычисления коэффициентов передачи решает в ускоренном времени дифференциальное уравнение (8) и формирует на своих п выходах текущее значение матрицы (Т, t). Блоки 15 и 18-21 20 служат для реализации u(t) в соответствии с выражением (-5) . В частности, на выходе блока 18 формируется е- х(Т) x(t), а на выходе блока 20 , tTr ) -25

- e (t)J.

Вторые матричные входы блоков 20 и 21 матричного умножения предназна- чен для транспортирования поступающей на них матричной информации за 30 счет соответствующей коммутации входов этих блоков с вьгходами блоков 13 и 4 соответственно (операция транспортирования предполагает изменение порядка индексации элементов матриц 35

С (Cij , i 1,:П,- j 1, го} tc,j , j 1, m; i 1, п}.

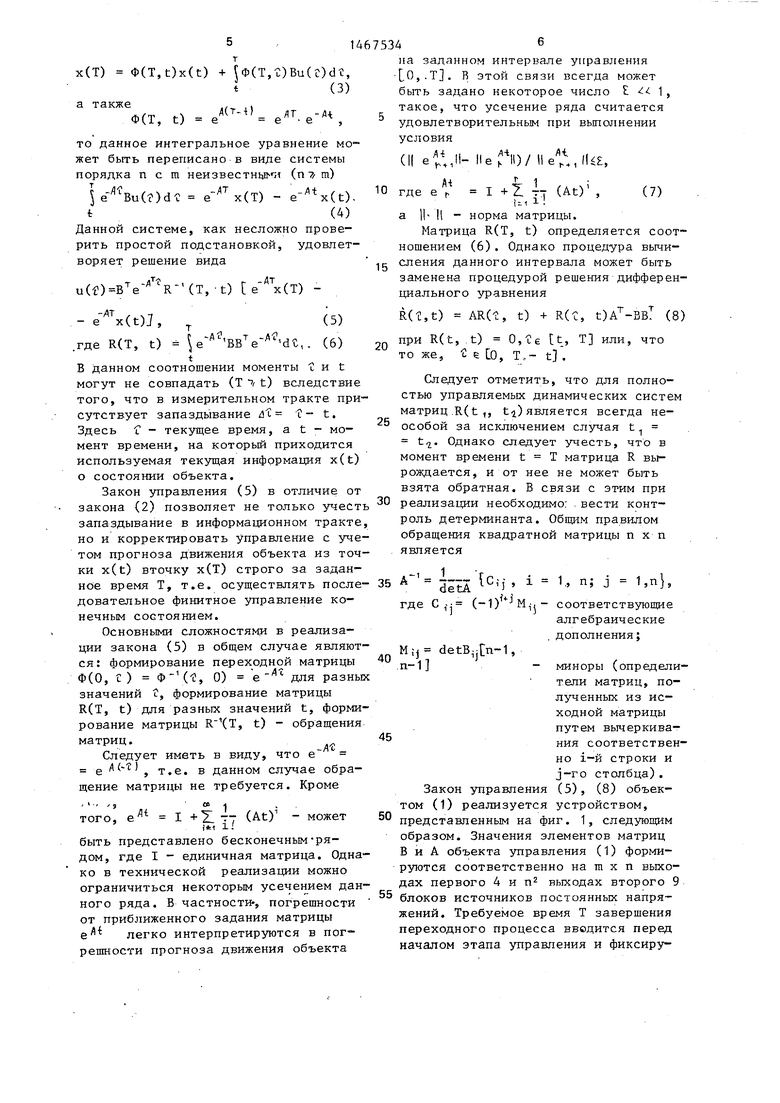

В.блоке 5 (фиг. 2) элементы 26 и 27 формируют правую часть уравнения (8), источник 28 единичного постоянного напряжения формирует пра- вую часть дифференциального уравнения С, 1, предназначенного для формирования на скалярном выходе блока интеграторов 29 текущего значения внутреннего (ускоренного) времени блока 5, Сумматор 32 формирует на своем выходе Т - t, а компаратор 31 сравнивает , с Т - t. Блок вычисления матричного определителя 33 формирует на своем выходе detR( С, t) и в случае неравенства данного зна.чения нулю разрешает подачу сигнала R(«) на вход блока 37 матричного инвертирования. Для фиксации текущего значения (Т, t), , Т, j 20 25

30 5

0

5

0

5

жит Итерой блок 38 : ;1ппми11люгш1х элемент он .

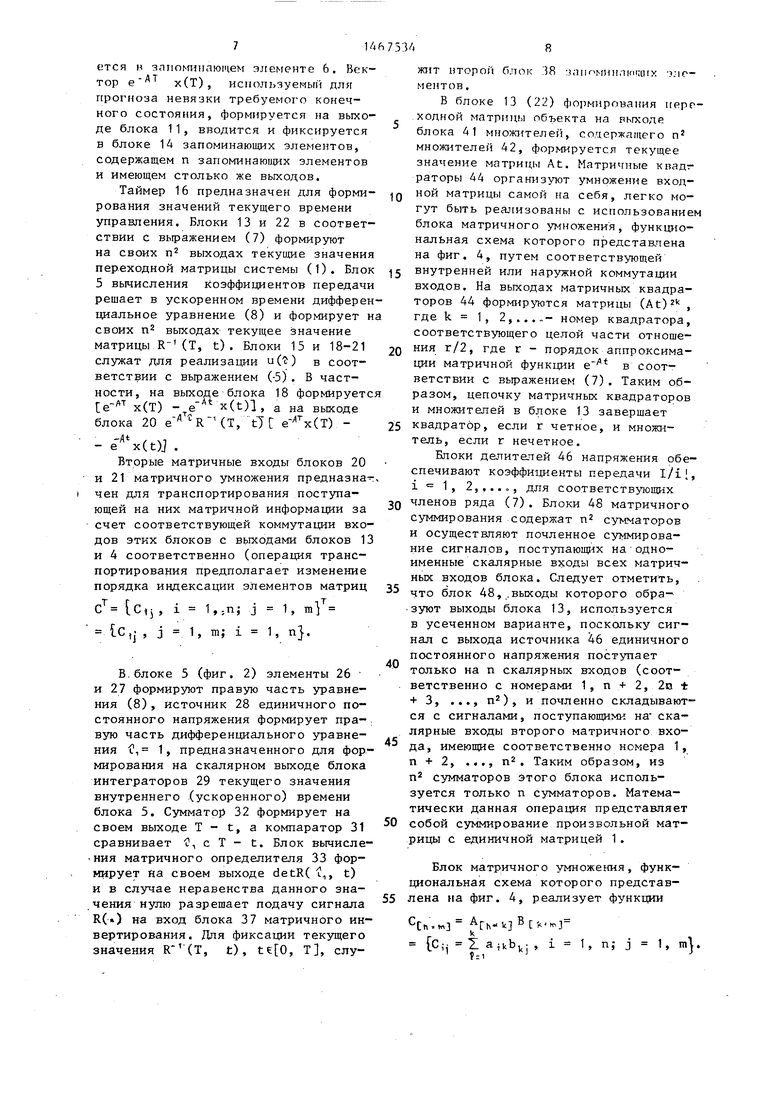

В блоке 13 (22) формирования иеро- ходной матрицы объекта на яьгходе блока 41 множителей, содержащего п множителей 42, формируется текущее значение матрицы At. Матричные квадт раторы 44 организуют умножение входной матрицы самой на себя, легко могут быть реализованы с использованием блока матричного умножения, функциональная схема которого предстаапена на фиг. 4, путем соответствующей внутренней или наружной коммутации входов. На выходах матричных квадраторов 44 формируются матрицы (At) , где k 1, 2,....- номер квадратора, соответствующего целой части отношения г/2, где г - порядок аппроксимации матричной функции в соответствии с выражением (7). Таким образом, цепочку матричных квадраторов и множителей в блоке 13 заверщает квадратор, если г четное, и множитель, если г нечетное.

Блоки делитатей 46 напряжения обеспечивают коэффициенты передачи Г/Ц, 2,,.. о, для соответствующих членов ряда (7). Блоки 48 матричного суммирования содержат п сумматоров и осуществляют почленное суммирование сигналов, поступающих наодноименные скалярные входы всех матричных входов блока. Следует отметить, что блок 48, .выходы которого обра- зуют выходы блока 13, используется в усеченном варианте, поскольку сигнал с выхода источника 46 единичного постоянного напряжения поступает только на п скалярных входов (соответственно с номерами 1, п 2, 2п t +3, .,.,п2),и почленно складываются с сигналами, поступающими на скалярные входы второго матричного входа, имеющие соответственно номера 1, п + 2, .,., п. Таким образом, из п сумматоров этого блока используется только п сумматоров. Математически данная операция представляет собой суммирование произвольной матрицы с единичной матрицей 1.

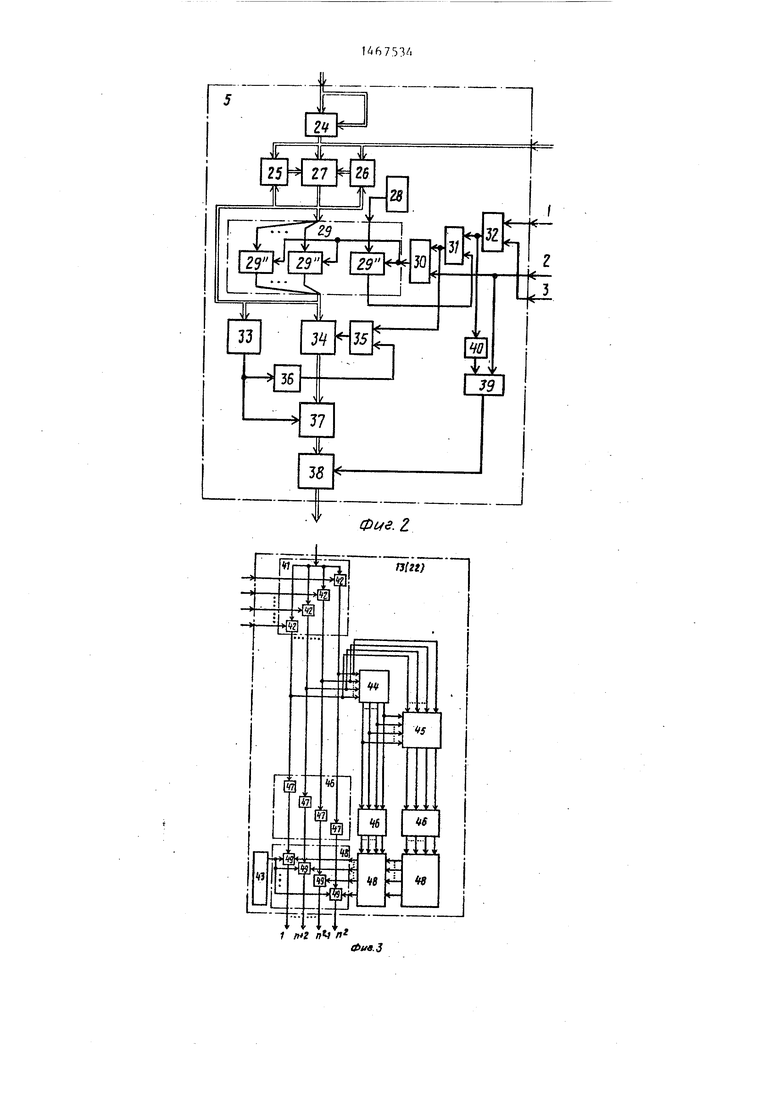

Блок матричного умножения, функциональная схема которого представлена на фиг. 4, реализует функции

Сп.м С

V

Ci,- Z , i 1, n; j 1, m.

9 :14

Устройство работает следующим образом.

Перед началом управления в блок 6 вводят параметр Т, характеризующий требуемую длительность переходного процесса, на матричный вход блока 11 подают значение компонент требуемого конечного положения объекта -хСТ). Работа устройства начинается по сиг- налу Пуск, поступающему с выхода блока 10. ,По этому сигналу открывается ключ 7, пропуская через блоки 8 и 12 на вход блока 13 значение парметра Т. Блок 13- производит вычисле- ние матрицы е , значение компонент которой поступает на вход множителя 11, формирующего на своем выходе вектор (Т). Длительность сигнала Пуск должна быть достаточной для гарантированного срабатывания блоков 13 и 11, а также записи вектора ) в блоке 14. Этим же сигналом запускается таймер 16, формирующий текущее значение параметра i текущего времени.

Сигнал Пуск через второй скалярный вход поступает в блок 5, где, пройдя через первый элемент ИЛИ 30, он устанавливает в ноль ин- теграторы блока 29, и, пройдя через второй элемент ИЛИ 39, обнуляет запоминающие элементы блока 38. После окончания действия сигнала Пуск ключ 7 закрывается и на выходе сум- матора 12 формируется лишь сигнал , который поступает на вход блока 13, формирующего текущее значение переходной матрицы е-. На выходе блока 15 формируется матрица е xCt) где t - i й велинина задержки, обеспечиваемой элементом 23. На выходе блока 5 формируется вектор R- CT, t), где t 1} -Л - время с учетом задержки, значение которого поступает на третий скалярный вход блока 5 (на первый скалярный вход постоянно поступает величина Т с выхода элемента 6). На выходах блоков 18-21 формируются векторные сигналы в соответствии с приведенным описа- ,нием работы устройства в статике. Блок 5 работает следующим образом.

На выходе элемента 32 постоянно формируется временное (таймерное) рассогласование 6 Т - t, которое в кошараторе 31 сравнивается с текущим значением внутреннего ускорен10

ного времени D, блока 5, формируемого на (п2 + 1)-ом выходе блока 29 интеграторов. Если оказывается, что 6 -ifO, то разрешающий сигнал поступает на вход элемента И 35 через элемент ИЛИ 30 устанавливает блок 29 в нулевое состояние R(0,0) 0 с тем, чтобы процесс интегрирования начинался сначала. Матрицы В и А задающие параметры объекта управления, поступают соответственно на первый и второй матричные вкоды блока 5,. На выходе блока 24 формируется матрица В-в , с выходов блоков 25 и 21 снимаются соответственно значения матриц А-R(-С,, 0) и R(D, , 0)А . В соответствии с этим на выходе сумматора 27 формируется матричный сигнал ARC,, 0) + R(,, 0)А - В В (вход два сумматора 27 взят с инверсией) .

Блок 33 постоянно вычисляет определитель матрицы RCc,, 0) , формируемо на выходе блока 29. Если detR(L,, 0) О, то с выхода нуль-индикатора 36 формируется нулевой сигнал, который, поступая на инверсный вход элемента И 35, является разрешающим. Однако элемент И 35 формирует разрешающий сигнал по условию detR Ф О, Г - 7,0. При этом срабатывает блок 34 ключей, пропуская на вход блока 37 матричного инвертирования сигнал R( , 0). При этом в блоке 38 запоминающих элементов фиксируются значения матрицы (6, 0). После этого цикл интегрирования в блоке 29 повторяется и в блоке 38 фиксируется новое значение матрицы ( 6 0) для изменившегося таймерного рассогласования 6, В момент, когда t становится равно Т, т.е. когда , срабатывает второй нуль-индикатор 40, а сформированный им единичный сигнал, пройдя через второй элемент ИЛИ 39, устанавливает в ноль блок 38. При этом управление, формируемое системой, обнуляется. Процесс управления заканчивается .

Преимущества предложенной системы перед известной заключаются в следующем. Известная система осуществляет управление по разомкнутой схеме, т.е. по временной программе, исходными данными при формировании которой являются лишь начальное и требуемое конечное положен11е объекта управления. В связи с этим при налиII

чии действукиилх на объект 1 коорди натно-параметрических возмущений

X + + 5(t), где А А +. ЛА в-

реальная матрица объекта; В + /3 В- реальная матрица

управления; А, 4В- параметрические

возмущения, кото могут представля собой матричные функции времени. ) - вектор координат

возмущений.

Известная система не позволит обесчить требуемую точность перевода оекта в заданное терминальное состояние.

Координатная погрешность в конц этапа управления с учетом соотноше (3) и (2) оценивается выражением

е )х(0) -ь

Лх(Т) е

45

е-« (В Т

(Т лдСт-т;

|Т/1

X

-AT

Hi

-й(.

в в

(в + лв)в

, т -1 е d C

-л г.

.(Т) - х(0) - 5 e i.Md f}

о и в случае задания матрицы А, 4А,

В, ЛВ и вектор-функции (t) може быть оценена аналитически. Посколь алгоритм формирует управление не т лько в функции текущего времени, н и вектора фазовых координат, то закнутая система объект-регулятор стновится нестационарной и получение в аналитическом виде координатной невязки представляет собой дотаточ но сложную задачу. Позтому сравнен известной и предложенной систем по точности приведения в окрестность терминальной точки производилось птем математического моделирования процесса управляемого движения объ екта с А ; и В о, и , где

и р const - максимальное значение управляющего ускорения. В модель вводилось параметрическое ли и координатное const возмущения.

Предложенная система за счет организации постоянной коррекции формируемого управления с учетом прогноза движения объекта в терминальн точку (организации последовательно финитного управления) в значительн мере обеспечивает компенсацию дей

0

5

5

0

5

0

5

0

5

стНИН координатно-параметрических возмущений. Этот факт в зависимости от конкретных условий позволяет повысить точность утгравления от нескольких десятков процентов до несколько раз. Формула изобретения

связана с первой группой из п входов четвертого блока матричного умножения, вторая группа из п входов которого соединена с группой из п выходов

13

блока вычисления коэффи1сиеитон передачи, группа из п выходов четвертого блока матричного умножения подключена к второй группе из п входов второго блока матричного умножения, группа из п выходов которого подключена к второй группе из п входов первого блока матричного умножения, группа из п выходов которого через блок исполнительных органов подключена к входу объекта управления, о т л и - чающаяся тем, что, с целью повышения точности управления конечным состоянием динамического объекта, она дополнительно снабжена вторым блоком формирования переходной матрицы объекта, пятым блоком матричного умножения и элементом задержки, причем выход второго инвертора соединен с входом элемента задержки, выход которого соединен с третьим ..-, входом блока вычисления коэффициентов передачи и входом второго бло ка формирования переходной матрицы, группа из п входов которого подключена к группе из п выходов второго блока источников постоянных напряжений, а группа из п выходов подключена к первой из п входов пятого блока матричного умножения, вторая группа из п входов которого подключена к группе выходов блока датчиков состояния объекта., а группа из п выходов пятого блока матричного умножения связана .с второй группой из п входов блока матричного вычитания.

10

15

20

25

30

35

40

к группе из п входов блока ин раторов, k(n2 + 1)-му входу ко подключен выход источника един постоянного напряжения, группа п выходов блока интеграторов ключена к вторым группам из п второго и третьего блоков матр умножения, к группе из п вход ка вычисления определителя мат и к группе из п информационны дов блока ключей, а (п + 1)-й ход блока интеграторов подключ первому входу компаратора, пер и третий входы блока вычислени фитщентов передачи подключены ветственно к первому и второму сумматора, вьпс од которого соед вторым входом компаратора и вх второго нуль-индикатора, второ блока вычисления коэффициентов дачи связан с вторьпум входами и второго элементов ИЛИ, первы первого элемента ИЛИ связан с дом компаратора и первым входо мента И, выход блока вычислени дели геля матрицы соединен чере вый нуль-индикатор с вторым вх элемента И, выход элемента И п чен, к управляющим входам блока чей, группа из п выходов блок

чей соединена с группой из п блока матричного обращения, вх торого соединен с выкодом блок числения определителя матрицы,

из п выходов блока матричного щения подключена к группе из входов блока запоминающих элем управляющий вход блока запомин элементов связан с выходом вто

50 элемента ИЛИ, второй вход кото соединен с выходом второго нул дикатора, группа из п2 выходов ка запоминающих элементов соед с группой из п выходов блока

па из п входов блока вычисления коэф-, 55 йления коэффициентов передачи.

7534U

фиииент -4 передачи соединен; с первыми группами из п пходок нторого и третьего блоков - матричного умножения , группы из п выходов первого, второго и третьего блоков матричного умножения соединены воответственно с первой, второй и третьей группами из п входов блока матричного рования, группа из п выходов блока матричного суммирования подключена

10

5

0

5

0

5

0

к группе из п входов блока интеграторов, k(n2 + 1)-му входу которого подключен выход источника единичного постоянного напряжения, группа из п выходов блока интеграторов подключена к вторым группам из п входов второго и третьего блоков матричного умножения, к группе из п входов блока вычисления определителя матрицы и к группе из п информационных входов блока ключей, а (п + 1)-й выход блока интеграторов подключен к первому входу компаратора, первый и третий входы блока вычисления коэф- фитщентов передачи подключены соответственно к первому и второму входам сумматора, вьпс од которого соединен с вторым входом компаратора и входом второго нуль-индикатора, второй вход блока вычисления коэффициентов передачи связан с вторьпум входами первого и второго элементов ИЛИ, первый вход первого элемента ИЛИ связан с ныхо- дом компаратора и первым входом элемента И, выход блока вычисления опре- дели геля матрицы соединен через первый нуль-индикатор с вторым входом элемента И, выход элемента И подключен, к управляющим входам блока ключей, группа из п выходов блока ключей соединена с группой из п входов блока матричного обращения, вход которого соединен с выкодом блока вычисления определителя матрицы, группа

из п выходов блока матричного обращения подключена к группе из п входов блока запоминающих элементов, управляющий вход блока запоминающих элементов связан с выходом второго

элемента ИЛИ, второй вход которогр соединен с выходом второго нуль-индикатора, группа из п2 выходов блока запоминающих элементов соединена с группой из п выходов блока вычи-

пт-:Ч4--

а™

.J

UU

G

И

W

lyt

ЙЬ

UjkziSn

; /нг /7« ff

. 2.

I

Ииип

1 2i П

Viii.S

.fJtVz.

/ 6/t,

-ЧХ- fb

:

IT

П

f

W-)

Cvj

i

E

c

«V)

Г

t

CSJ

C;

| Ройтенберг Я.Н | |||

| Автоматическое управление | |||

| М.: Наука, 1973, с | |||

| Затвор для дверей холодильных камер | 1920 |

|

SU182A1 |

Авторы

Даты

1989-03-23—Публикация

1987-06-11—Подача