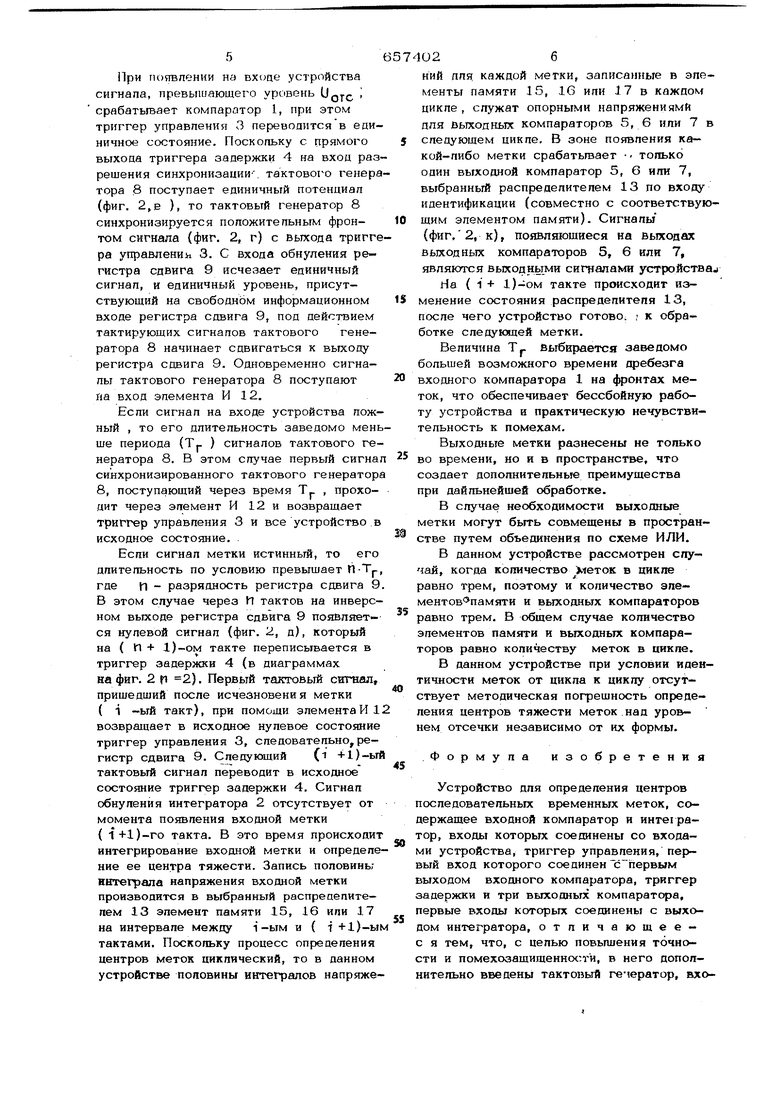

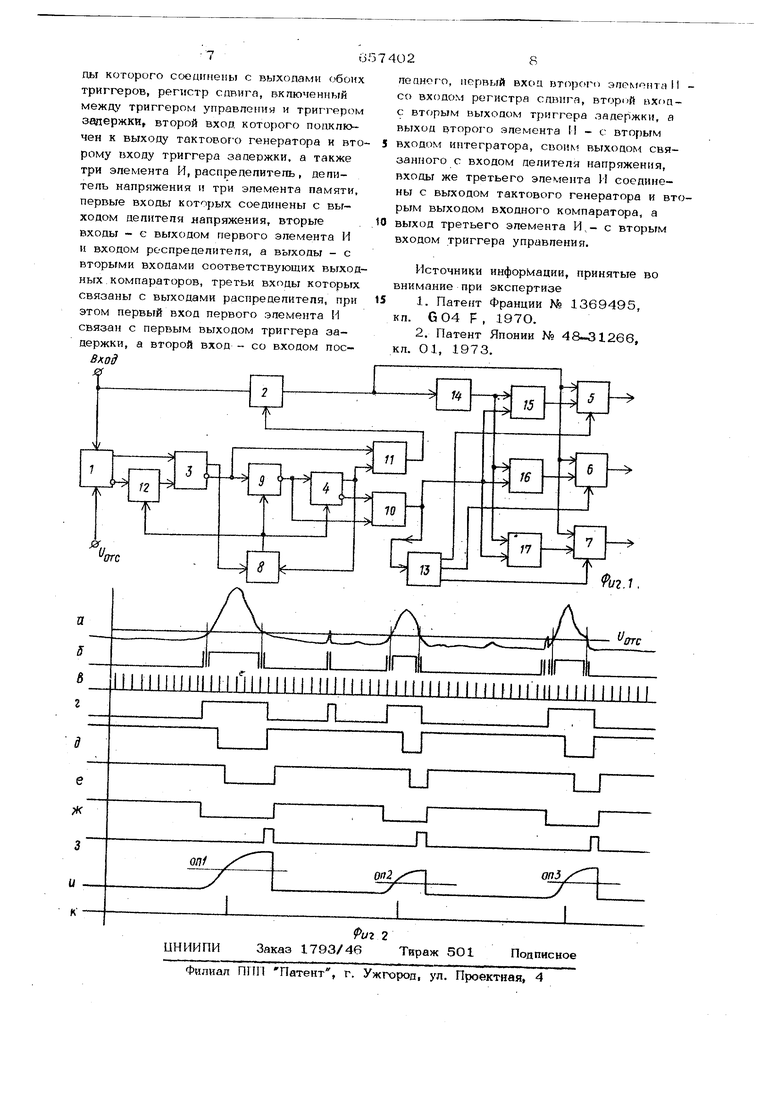

(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЦЕНТРОВ ПОСЛЕДОВАТЕЛЬНЫХ ВРЕМЕННЫХ МЕТОК 12 входы которых соединены с входами устройства,триггер управления, первый вход которого соединен с первым выхо домвходного компаратора, триггер задержки и три выхопньгх компаратора, первые входьг которых соединены с выходом интегратора, цопопнительно введены тактовый генератор, входы которого соединены с выходами обоих триггеров, регистр сдвига, включенный между триггером управления и триггером задержки, второй вход которого подключен к выходу тактового генератора и второму входу триггера задержки, а также три элемента И, распредепитепъ, делитель напряжения и три элемента памяти, первые входы которых соединены с выходом делителя напряжения, вторые входы - с выходом первого элемента И и входом распредепи тепя, а выходы с вторыми входами соответствующих выходных компараторов третьи входы которьрс связаны с выходами распределителя, при этом первый вход первого элемента И связан с первым выходом тригтера задержки, а второй вход - с входом последнего, первый вход второго элемента И - со входом регистра сдвига , второй вход - с вторы выходом триггера задрежки, а выход вто рого элемента И - с вторым входом интегратора, своим выходом связанного с входом делителя напряжения, входы же третьего элемента И соединены с выходо тактового генератора и вторым выходом входного компаратора, а выход третьего элемента И - с вторым входом триггера управления.. На фиг, 1 представлена функциональная схема преилагаемого устройства для определения центров последовательных временных меток; на фиг. 2 - временные диаграммы, поясняющие работу данного устройства. Это устройство содержит входной компаратор 1 и интегратор 2, входы которых соединены со.входами устройства, триггер управления 3, первый вход которого соединен с первым выходом вход ного компаратора 1, триггер задержки 4 и три выходных компаратора 5, 6. и 7., первые входы которых соединены с выхо дом интегратора 2. Кроме того, устройство содержит тактовый генератор 8, его входы соединены с выходами обоих триггеров управления 3 и 4, регистр сдвига 9, включенный между триггером . управления 3 и триггером задержки 4, второй вход которого подключен к выхо624 ду тактового генератора 8 и второму входу триппера задержки 4, а также три элемента И 1.0, 11 и 12, распреде 1Итель 13, делитель напряжения 14 и три элемента памяти 15, 16 и 17, первые входы которых соединены с выходом делителя напряжения 14, вторые входы - с выходом первого элемента И 1О и входом распределителя 13, а выходы - со вторы- ми входами соответствующих выходных компараторов 5, 6 и 7, третьи входы Лторых связаны с выходами распределителя 13. Первый вход первого элемента И 10 связан с первым выходом триггера задержки 4, а второй вход с входом триггера задержки 4. Первый вход второго элемента И 11 соединен с входом регистра сдвига 9, второй вход - со вторым выходом триггера задержки 4, а выход второго элемента. И 11 - со вторым входом интегратора 2, своим выходом связанного с уходом делителя напряжения 14. Входы третьего элемента И 12 соединены с выходом тактового генератора 8 и вторым выходом входного компаратора 1, а выход третьего элемента И - со вторым входо триггера управления 3. Данное устройство работает следующим образом. Из входных меток (фиг, 2,а) компаратор 1 на уровне отсечки ( Uotc ) формируются бинарные сигналы (фиг.2,б). В исходном состоянии при отсутствии меток -единичный сигнал с инверсного выхода компаратора 1 разрешает прохождение через элемент И 12 сигналов тактового генератора 8 (фиг. 2, в), устанавливающих в нулевое состояние триггер управления 3. Единичный сигнал с инверсного выхода триггера управления 3 удерживает в нулевом состоянии регистр сдвига 9, при этом триггер задержки 4 тактирующими сигналами (фиг.2, в) гак-б тового генератора 8 устанавпивается в единичное состояние. С выхода элемента И И на вход обнуления интег|1атора 2 поступает единичный сигнал (фиг. 2, ж), удерживающий интегратор 2 в нугеевом состоянии. На выходе элемента И 10 присутствует вупевЪй сигнал (фиг, 2, з), благодаря чему элементы памяти 15, 16 и 17 находятся в режиме хранения опорных уровней. Выходные компараторы 5, 6 и 7 закрыты Н пе&ым уровнем, поступаюшим с выхопа ватет штора 2 (фиг. 2, в). При появлении на входе устройства сигнала, превышающего уровень UQI. срабатывает компаратор 1, при этом триггер управления 3 переводится в еди ничное состояние. Поскольку с прямого выхода триггера задержки 4 на вход раз решения синхронизации-, тактового генер тора 8 поступает единичный потенциал (фиг. 2,в ), то тактовый генератор 8 синхронизируется положительным фронтом сигнала {фиг, 2, г) с выхода тригг ра управлени11 3. С вхопа обнуления регистра спвига 9 исчезает единичный сигнал, и единичный уровень, присутствующий на свободном информационном входе регистра сдвига 9, под действием тактирующих сигнапов тактового генератора 8 начинает сдвигаться к выходу регистра сдвига 9. Одновременно сигналы тактового генератора 8 поступают fta вход элемента И 12. Если сигнал на входе устройства пож ный , то его длительность заведомо мен ше периода (Тр ) сигналов тактового генератора 8, В этом случае первый сигнал синхронизированного тактового генератора 8, поступающий через время Т- , проходит через элемент И 12 и возвращает триггер управления 3 и все устройство в исходное состояние. Если сигнал метки истинный, то его длительность по условию превышает П-Т, где П - разрядность регистра сдвига 9 В этом случае через И тактов на инверсном выходе регистра сдвига 9 появляется нулевой сигнал (фиг. 2, д), который на ( И + 1)-ом такте переписывается в триггер задержки 4 (в диаграммах на фиг, 2 fi 2). Первый тактовый сигнал, пришедший после исчезновения метки ( i -ый такт), при помощи элемента И 1 возвращает в исходное нулевое состояние триггер управления 3, следовательно,регистр сдвига 9, Следующий (i +1)-ьгй тактовый сигнал переводит в исходное состояние триггер задержки 4. Сигнал обнуления интегратора 2 отсутствует от момента по5тления входной метки ( 1-И)-го такта. В это время происходит интегрирование входной метки и определение ее центра тяжести. Запись половины интеграла напряжения входной метки производится в выбранный распреаепите- лем 13 элемент памяти 15, 16 ипи 17 на интервале между 1-ым и ( i +1)-ым тактами. Поскольку процесс определения центров меток циклический, то в данном устройстве половины интегралов напряжеO2бНИИ пля каждой метки, записанные в элементы памяти 15, 16 ипи 17 в каждом цикле, служат опорными напряжениями пля выходных компараторов 5, 6 или 7 в следующем цикле, В зоне появления какой-либо метки срабатьгаает только один выходной компаратор 5, 6 или 7, выбранный распределителем 13 по входу идентификации (совместно с соответствующим элементом памяти). Сигналы (фиг.2, к), появляюшиеся на выходах выход ньтх компараторов 5, 6 или 7, являются выходными сигналами устройства На ( 1 + 1)-ом такте происходит изменение состояния распределителя 13, после чего устройство готово ; к обработке следующей метки. Величина Т.. Выбирается заведомо большей возможного времени дребезга входного компаратора 1 на «{рентах меток, что обеспечивает бессбойную работу устройства и практическую нечувствительность к помехам. Выходаые метки разнесены не только gQ времени, но и в пространстве, что создает дополнительные преимущества при дайльнейшей обработке. В случае необходимости выходные метки могут быть совмещены в пространстве путем объединения по схеме ИЛИ. В данном устройстве рассмотрен случай, когда копичество)йеток в цикле равно трем, поэтому и количество элементов памяти и выходных компараторов равно трем. В общем случае количество элементов памяти и выходных компараторов равно количеству меток в цикле. В данном устройстве при условии идентичности меток от цикла к циклу отсутствует методическая погрешность определения центров тяжести меток.над уровнем отсечки независимо от их формы. Формула изобретения Устройство для определения центров последовательных временных меток, содержащее входной компаратор н интегратор, входы которых соединены со входами устройства, триггер управления, первый вход которого соединен с первым выходом входного компаратора, триггер задержки и три выходных компаратора, первые входы которых соединены с выходом интегратора, отличающее- с я тем, что, с целью повышения точности и помехозащищенно ;ти, в него дополнительно введены тактовый гемератор, входьг которого соешгнеиы с выхопами обоих триггеров, регистр сдвига, вкпюченньгй между триггером управпония и триггером задержки, второй вход которого поцкпючен к выходу тактового генератора и вто рому входу триггера задержки, а также три элемента И, распредепитель , депитепь напряжения и три элемента памяти, первые входы которых соединены с выходом делитепя напряжения, вторые входы - с выходом первого эпемента И н входом роспределитепя, а выходы - с вторыми входами соответствующих выход ных компараторов, третьи входы которых связаны с выходами распределителя, при этом первый вход первого элемента И связан с первым выходом триггера задержки, а второй вход - со входом последнего, перврлй вход вторсгч aneNtonr; И со входом регистра сдвига, второй вхпдс вторым выходом триггера задержки, а выход второго элемента II - с вторым входом интегратора, своим выходом связанного с входом делителя напряжения, входы же третьего элемента И соединены с выходом тактового генератора и вторым выходом входного компаратора, а выход третьего эпемента И,- с вторым входом триггера управления. Источники информации, принятые во внимание при экспертизе 1. Патент Франции № 1369495, кл. G04 F , 1970. 2. Патент Японии № 48-31266, кл. 01, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство слежения за задержкой псевдослучайной последовательности | 1984 |

|

SU1225033A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Цифровое устройство управление весовым дозированием | 1980 |

|

SU866418A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

Авторы

Даты

1979-04-15—Публикация

1976-08-01—Подача