Изобретение относится к автомати- ice и технике связи и может быть ис- тользовано в системах передачи инфор- ilaции с помощью дельта-модуляции.

Цель изобретения - повышение на дежности функционирования.

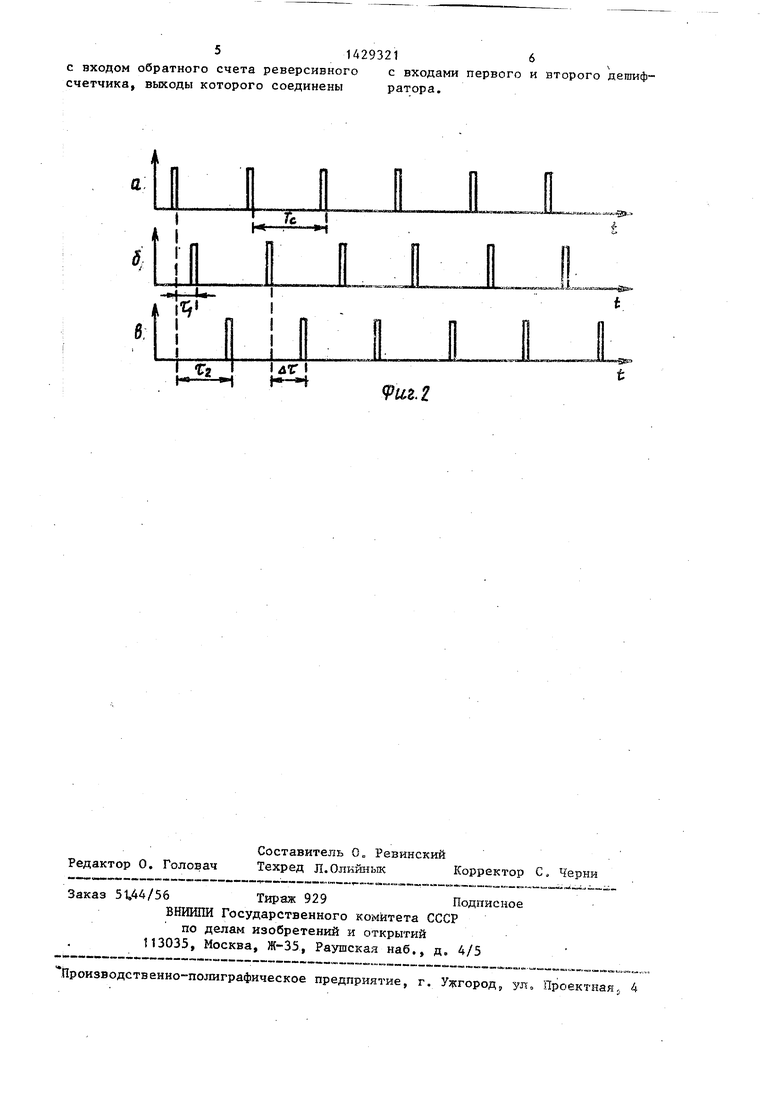

На фиг. 1 дана функциональная схема дельта-кодера5 на фиг. 2 - временные диаграммы сигналов на входе И выходах элемента задержки, I Дельта-кодер содержит компаратор 1| J триггер 2j первый регистр 3 сдви Га, первый-четвертьй элементы И 4-7 йервый 8 и второй 9 элементы ИЛИ, реверсивный счетчик 10, кодопреоб- |)азователь 11, цифровой интегратор 12, первый 13 к второй 14 дешифрато- |)Ы, первый 15 и второй, 16 элементы НЕ, делитель 17 частоты, элемент 18 адеретш и второй регистр 19 сдвига, kpoMe того, дельта-кодер имеет инфор рационный 20 и тактовый 21 входы и выход 22..

Кодопреобразователь 11 выполнен, на блоке постоянной памяти и блоке ;Мультиплексоров, подключающем к вы ходам кодопреобразователя 11 соответствующие выходы блока постоянной памяти по сигналам на его управляющих входах.

Цифровой интегратор 12 выполнен на арифметико-логическом блоке, цифро- аналоговом прео бразователе и буферном регистре, выходы которого подключены к входам цифроаналогового преобразо- 1зателя и первым входам арифметико-логического блока, выходы которого соединены с информационными входами буферного регистра, управляющий вход Которого является тактовым входом цифрового интегратора 12 вторые информационные и управляющий входы арифметико-логического блока и выход цифроаналогового преобразователя яв- соответственно информационными и знаковым входаг-си и выкoдo s цифрового интегратора 12,

. Первый 13 и второй 14 дешифраторы служат для индикации достижения ре- версивным счетчиком 10 соответственно максимального и минимального значений (величины шага квантования).

Элемент 18 задержки по тактовым импульсам на входе (фиг„ 2а) форми- рует на первом и втором выходах задержание, последовательности импульсов (фиг. 26 и в), Первьш и второй выходы второго регистра 19 сдвига

S

0

5

,

Q

Q

5

0

5

являются выходами его первого и последнего разрядов.

Первьй регистр 3 сдвига, элементы И 4 и 5 и элемент ИЛИ 8 представляет собой анализатор цифрового дельта-мо- дулированного (ДО) сигнала.

Дельта кодер работает следующиг-i образом.

Цифровой ДМ сигнал, образованный в результате .сравнения входного U(O и аппроксш-шрукщего U (t) сигналов компаратором 1 и дискретизации результатов сравнения триггером 2, последовательно заполняет разряды регистра 3 сдвига и анализирует элементы И 4 и 5, ИЖ 8. Результаты анализа в виде цифрового сигнала записываются в регистр 19 сдвига и, продвигаются 3 нем с приходом тактовых ш-отульсов с входа 21, В каждом такте информация,, записанная в регистр сдвига,, через третий 7. и четвертьйВ элементыИ и второй элемент ИЛИ 9 воздействуют . на счетные входы реверсивного счетчика 10„ Кроме Toroj, на третьи входы элементов И 7 и 8 поступают сигналы с первого и второго выходов элемента 13 задержки, -на вход которого посту- nasQT тактовые импульсы. Сигнал на первом выходе элемента 18 задержки задержан (сдвинут) относительно входного сигнала на некотор ое произвольное время , , а сигнал на втором выходе элемента 18 задержки ;г на время cTj, J причем С s f но l Т , где Tj) - период тактовой частоты.

Таким образом в каждом такте ка третьи входы элементов И 7 и 8 поочередно (с интервалом Ь. г. ) воздействуют сканирующие импульсы, переключая сначала информационный бит из первого разряда регистра 19 сдвига на вход прямого счета реверсивного счетчика 10, а затем, инфор- мационньй бит из последнего разряда регистра 19 сдвига на вход обратного счета реверсивного счетчика 20. Состояние реверсивного счетчика 10, таким образом, постоянно отражает плотность (соотношение единичных и г/.,певьгх пачек) 7дифрового ДМ-сигнала на некотором фрагменте (интервале), длительность которого определяется разрядностью регистра 6 сдвига. Длительность анализируемого фрагмента целесообразно выбирать в пределах 3-10 мс, что при тактовых частотах 16-32 кГц позволяет выбирать разряд- .

ность регистра J9 сдвига в пределах 50-300, в зависимости от конкретной тактовой частоты и требуемой инерционности адаптации. Кодовая комбинация на выходах реверсивного счетчика 10 в дальнейшем используется для формирования конкретного шага квантования (двоичного числа, отображающего шаг квантования) на выходе кодопреобразователя 11. Восстановление аппроксимирующего сигнала происходит при помощи цифрового интегратора.

Дешифраторы 13 и 14 в совокупности с первым 15 и вторым 16 элементами НЕ создают цепи блокировки крайних состояний реверсивного счетчика 10 в режиме холостого хода и кратковременной перегрузки кодера для устранения сбоев, связанных с перегрузкой реверсивного счетчика 10.

Делитель 17 частоты и второй элемент ИЛИ 9 используют для очистки реверсивного счетчика 10 от результатов воздействия шумов и сбоев в цифровом Д Г-cигнaлe. Коэффициент деления делителя 17 частоты целесообразно выбирать таким, чтобы импульсы, посту- .пакщие время от времени на вход обратного счета реверсивного счетчика 10 (и уменьшающие двоичное число на его выходах), не оказывали определяющего влияния на величину шага квантования при передаче полезного сигнала, но позволяли счетчику 10 освобождаться от результатов юбоев (а не накапливать их в течение всего времени работы). На практике коэффициент деления рекомендуется выбирать в пределах 10-20, что конкретно зависит от зашумленности канала связи.

Таким образом, благодаря способу управления величиной шага квантования в цепи компандирования в дельта-кодере без дополнительного синхроканала обеспечивается требуемая для нормальной работы подстройка (адаптация) шага квантования по параметрам передаваемого сигнала. Отпадает необходимость в дополнительном канале син- хроя.изации, что приводит к повышению стабильности работы за счет отсутствия принципиальной возможности сбоев в синхронизации, сокращения аппаратуры синхронизации и уменьшения до минимума времени вхождения в синхронизм на приемной стороне.

Предлагаемый дельта-кодер (и частности, его цепь адаптации) имее бо0

5

0

5

0

5

5

0

5

лее простое выполнение, чем известный, что, в свою очередь также обусловливает лучшую стабильность и надежность.

Формула изобретения

Дельта-кодер, содержащий компаратор, первый вход которого является информационньм входом дельта-кодера, выход компаратора соединен с информационным входом триггера, выход которого подключен к информацнонночу входу первого регистра сдвига, знаковому входу цифрового интегратора и является выходом депьта-кодера, прямые и инверсные выходы разрядов первого регистра сдвига соединены с входами соответственно первого и ато- рого элементов И,- вькоды которых подключены к входам первого элемента ИЛИ, второй элемент ИЛИ, реверсивный счетчик, выходы которого подключены к входам кодопреобразователя, выходы которого соединены с информационными

О

входами цифрового интегратора, выход которого подключен к второму входу компаратора, первьш и второй дешифраторы, выходы которых соединены через одноименные элементы НЕ с пер- выми входами соответственно третьего и четвертого элементов И, выход третьего .элемента И подключен к входу прямого счета реверсивного счетчика, тактовые входы триггера, первого р ;гистра сдвига и цифрового интеграг тора объединены и являются тактовым входом дельта-кодера, отличающийся Teivi, что, с целью повы- 0 шения надежности функцион фования, в дельта-кодер введены второй регистр сдвига, элемент задержки и делитель частоты, вход которого объединен с входом элемента задержки и тактовым входом второго регистра сдвига и подключен к тактовому входу дельта- кодера, выход первого элемента ИЛИ соединен с информационньм входом второго регистра сдвига, первый и второй выходы которого подключены к к вторым входам соответственно третьего и четвертого элементов И, первый и второй выходы элемента задержки соединены с третьими входами соответственно третьего и четвертого элементов И, выходы делителя частоты и четвертого элемента И подключены к первому и второму входам второго элемента ИЛИ, выход которого соединен

514293216

с входом обратного счета реверсивного с входами первого и второго дешиф- счетчика, выходы которого соединены ратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

| ДЕЛЬТА-КОДЕК | 1998 |

|

RU2172554C2 |

Изобретение относится к автоматике и технике связи. Его использование в системах передачи информации с помощью дельта-модуляции позволяет повысить надежность функционирования дельта-кодера, который содержит компаратор 1, триггер 2, регистр 3 сдвига, элементы И 4-7, элементы ИЖ , 9, 9, реверсивный счетчик 10, кодопреобразователь 11, цифровой интегратор 12, дешифраторы 13, 14 и элементы НЕ 15, 16. Благодаря введению делителя 17 частоты, элемента 18 задержки и регистра 19 сдвига упрощается выполнение дельта-кодера, а также отпадает необходимость в до- .полнит ельном канале синхронизации при передаче. 2 ил.

а

1Г

9 иг. 2

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Адаптивный дельта-модулятор | 1984 |

|

SU1246379A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-17—Подача