1

Изобретение относится к измеритель- ной технике и предназначено для дискретного изменения фазы входногоСинусои.дального напряжения от О до 36О в соответствии с управляющим сигналом.

Наиболее близким техническим решением к данному изобретению является дискретный фазовращатель, содержащий источники управляющего сигнала, фазовращатель, вход которого под1шючен х первому входу первого умножителя сигналов выход фазовращателя подключен к первому входу второго умножителя сигналов, выходы первого и второго умножителей сигналов подключены ко входам сумматора YI. В этом фазовращателе напряжение выходного сигнала равно

Ug.j,-А Cacos jot-vl33inait),

где А - постоянный коэффициент;

Ои- частота входного сигнала; Q Ь - сигналы, поступающие на ВХОД первого и второго умножителей сигналов соответственно.

Недостатком такого устройства является то, что сигналы а и в в нем представляют собой кусочно-линейные функции от величины управляющего сигнала. Отклонение указанных функций от синусои- дал ьных приводит к значительному изменению амплитуды и нелинейному изменению фазы выходного сигнала при линейном изменении величины управл1аощего сигнала. Это не позволяет получить сдвинутый по фазе синусоидальный сигнал с наименьшими амплитудными и фазовыми искажениями.

Целью Изобретения является получение дискретных фазовых сдвигов синусоидального сигнала с наименьшими амплитудными и фазовыми искажениями.

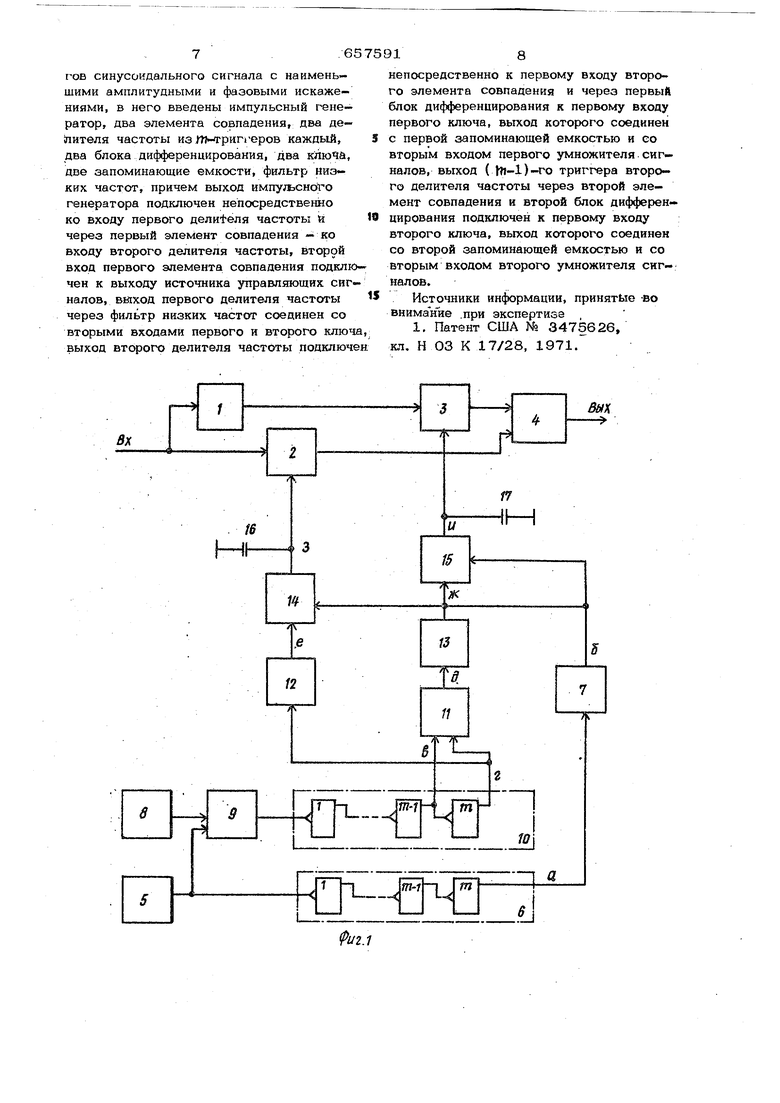

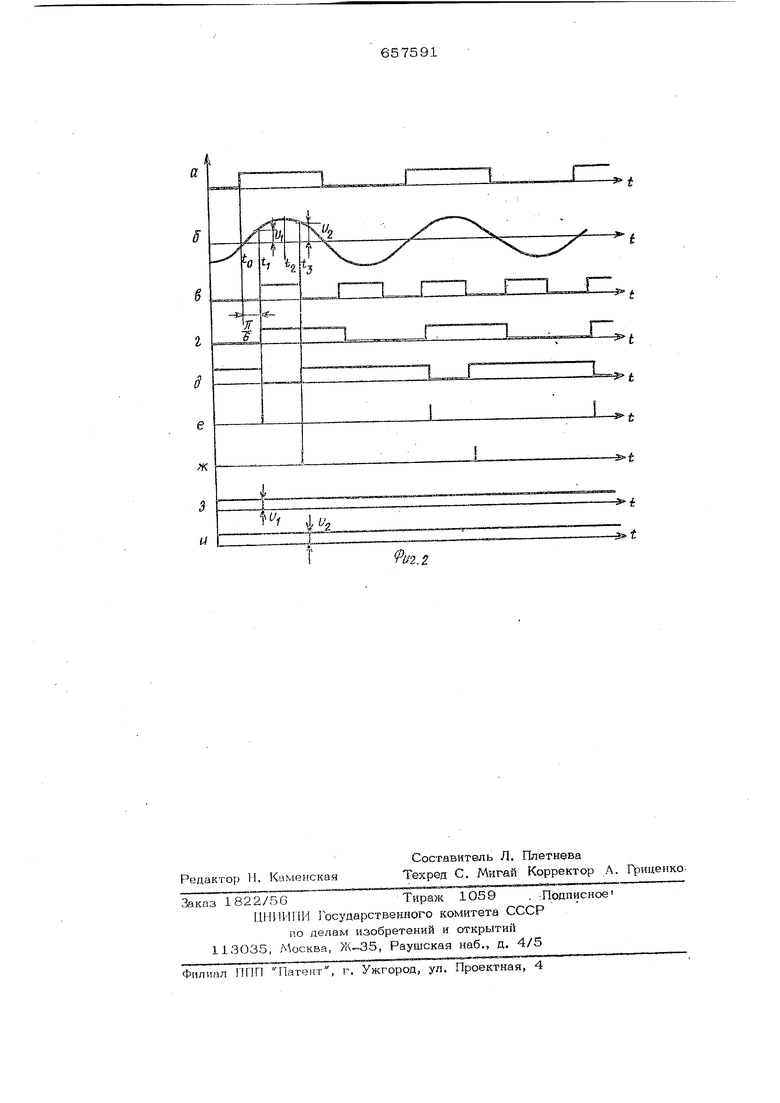

Это достигается тем, что в предлагаемый дискретный фазсдаращатель введены импульсный генератор, два элемен- та совпадения , два делителя частотой изm триггеров каждый, два блока дифференцирования, два ключа, две запоминающие емкости, фильтр низких частот, причем выход импульсного генератора подключен непосредственно ко входу первого делителя частоты и через первый эле мент совпадения ко входу второго делителя частоты, второй вход первого эле- мента совпадения подключен к выходу источника управляющих сигналов, выход, первого делителя частоты через фильтр низких частот соединен со вторыми входами первого и второго ключа, выход вто рого делителя частоты подключен непосредственно к первому входу второго элемента совпадения и через первый блок дифференцирования к первому входу первого ключа, выход которого соединен с пер- вой запоминающей емкостью и со вторым входом первого умножителя сигналов, вц ход ( )-го триггера второго делителя частоты через второй элемент совпадени и второй блок дифференцирования подключен к первому входу второго ключа, выход которого соединен do второй запоминающей емкостью И;со вторым вхо дом второго умножителя сигналов. На фиг. 1 представлена функцнональ- ная схема предлагаемого устройства} на фиг. 2 временные-диаграммы, иллюстри рующие его работу. Дискретный фазовращатель содергкит фазовращатель 1, первый к второй умножители сигналов 2 и 3, сумматор 4, импульсный генератор 5, первый делитель частоты 6, фильтр низких частот 7, ис- точник управляющего сигнала 8, элемент совпадения 9, второй делитель частоты 10,элемент совпадения 11, первый и второй блоки дифференцирования 12, 13, первый и второй ключи 14, 15,-первую и вторую запоминающие емкости 16, 17, Вход фазовращателя 1 подключен к первому входу умножителя сигналов 2. Выход фазовращателя 1 подключен к первому входу умножителя сигналов 3. Выхо ды умножителей сигналов 2 и 3 подключе ны ко входам сумматора 4. Выход импул сного генератора 5 подключен непосредст венно ко входу делителя частоты 6 и через .элемент совпадения 9 ко входу делителя частоты Ю. Второй вход элемента ,совпадения 9 подключен к выходу источ ника управляющих сигналов 8. Выход дел теля частоты 6 через фильтр низких -частот соединен со вторыми входами ключей 14 и 15. Один выход делителя частоты 10 подключен непосредственно к первому входу элемента, совпадения 11 и через блок дифференцирования 12 к одному из входов ключа 14, выход которого соединен с запоминающей емкостью 16 и со вторым входом умножителя сигналов 2. Другой выход делителя 10 (выход Щ-)го триггера) через последовательно сое- динрнные элемент совпадения 11 и блок дифференцирования 13 подключен к одному из входов ключа 15, выход которого соединен с запоминающей емкостью 17 и со вторым входом умножителя,сигналов 3. Устройство работает следующим образом. Входной синусоидальный сигнал поступает на вход фазовращателя 1 и первый вход умножителя сигналов 2, где он умножается на. коэффициент, пропорциональный величине сигнала 6, поступающего на второй его вход. Сдвинутый на 9О входной сигнал с выхода фазовращателя 1 поступает на первый вход умножителя сигналов 3, где он умножается на коэффициент, пропорциональный величине сигнала ё , поступающего на второй его вход. Умноженные сигналы поступают «на сумматор 4, в котором складываются и суммарный сигнал - этовыходной сигнал устройства. Сигналы айв, пропорциональные соответственно синусу и косинусу одной и той же величины, получаются следующим образом. Сигнал с .выхода импульсного генератора 5 делится в триггернрм делителе 6, содержащем .fn триггеров, и поделенный импульсный сигнал (фиг. 2а) преЪбразуется в синусоидальный в фильтре низкой частоты 7 (фиг. 26). При отсутствии сигнала с выхода источника управляющих сигналов 8, через схему совпадения 9 пройдут сигналы импульсного генератора 5 на вход делителя 10 (который также содержит Ж триггеров), на его выходе появятся поделенные сигналы (фиг. 26),. идентичные выходным сигналам делителя 6 (фиг. 2а). С выхода (.fti-l)-ro триггера (фиг. 2в) делителя 10 и с выхода Л1-го триггера делителя 10 (фиг. 2а) сигналы поступают на элемент совпадения 11, на выходе которого появляется сигнал (фиг. 2а) со скважностью, равной четырем, и положительный фронт его на 90 отстоит DT положительного фронта сигнала с выхода , ni-ro триггера делителя 1О. Блоки дифференцирования 12 и 13 формируют короткие импульсы в моменты, соответствующие положительным фронтгам импульсов с выхода (П1-го триггера делителя 10 (фиг. 2е) и с выхода элемента совпадения 11 (фиг. 2ж). Эти короткие импульсы отстоят один от другого на четверть периода выходной частоты делителей 6 и 10. Выходные сигналы блоков дифференцирования 12 и 13 поступают на первые входы ключей 14 и 15 соответственно. На вторые входы ключей 14 и 15 поступает синусоидальный сигнал с выхода фильтра низкой Частоты Тис частотой, равной частоте выходного сигнала делителей 6 и 1О. На выходах ключей 14 и 15 появляются короткие импульсы с амплитудой равной амплитуде выходного сигнала фильл-- ра низкой частоты 7 в моменты открыва 1кя ключей 14 и 15 (в моменты поступ ния на их входы коротких импульсов). Э амплитуда запоминается емкостями 16 (фиг. 2з) и 17 (фиг. 2и) и передается на вторые входы умножителей сигналов 2 и 3 соответственно. В случае, когда управляющий сигнал с блока 8 отсутствует, выходные сигналы делителя 6 и делителя 10 (выход Щ-го триггера) не сдвинуты по фазе один относительно дру гого. При наличии сигнала управления фаза выходного сигнала делителя 1О (вы ход Я1-ГО триггера) сдвигается относительно выходного сигнала делителя 6 на величину, пропорциональную количеству импульсов, поступающих с выхода источника управляющего сигнала 8. Соот- ветственно меняются амплитуды импульсов с выходов ключей Ifl и 15. Так например, при отсутствии управляющего сигнала на выходе блока дифференцирования 12 появлялся бы импульс в момент, соответствующий нулевому зна чению сигнала с выхода фильтра низкой частоты 7 (момент ij-j фиг. 2б), а на выходе блока дифференцирования 13- в момент, соответствующий максимуму сигнала с выхода фильтра низкой частоты 7 (момент времени |;2 26). Соответственно, на выходе ключа 14 бу дет нулевой сигнал, а на выходе ключа 15 -.максимальный. Коэффициент О О, и лло|-КС в рассматриваемом на временных диаграммах случае управляющий сигнал сдвинул по фазе сигнал с выхода делителя 10 фиг. 2г) относительно сигнала с выхода делителя 6 (фиг. 2а), на 30 . Тогда импульс с выхода блока дифференцирования 12 (фиг. 2е) откроет ключ 14 в момент времени (фиг. 26), и амплитуда выходногО сигнала ключа 14 соответствует значению синусоидального вы- ходного сигнала фильтра низкой частоты 7 в этот момент U(-t,)-U S-ln 30°-0,5U, гдеи(Ь) - значение выходного сигнала фильтра низкой частоты в момент времени 4 и, - максимальное значение выходного сигнала фильтра низкой частоты. Емкость 16 запоминает это мгновенное значение сигнала с выхода фильтра низкой частоты и на ней поддерживается постоянное напряжение, равное О,5и(фиг. 2з). Импульс с выхода блока дифференцирова- 13 (фиг. 2ж) откроет ключ 15 в момент времени Т. , и амплитуда выходного сигнала ключа 15 соответствует значению синусоидального выходного сигнала фильтра низкой частоты 7 в этот момент времени U(-t,V-U,sin(50°-vf-1--U cos3o U, Где:и(Ъз)- значение выходного сигнала ф ильтра низкой частоты в момент времени t . Запоминающая ек кость 17 запоминает это мгновенное значение сигнала с выхода фильтра низкой частоты и на ней будет постоянное напряжение, равное О (фиг. 2и). Таким образом напря)сение на запоминающих емкостях 16, 17, соответствующие коэффициентам айв, имеют значения,. пропорциональные синусу и косинусу одного-и того же угла, а обеспечение таких величин напряжений позволяет получить на выходе устройства сигнал неизменной амплитуды. Кроме того, в зависимости от числа управляющих импульсов с выхода источника управляющего сигнала 8 фаза выходного сигнала устройства меняется линейно. Прирост изменения фазы постоянен и зависит от коэ()фициента деления делителей 6 и 1О. Следовательно, предлагаемая схема обеспечивает минимальные амплитудные и фазовые искажения синусоидального сигнала, сдвинутого по фазе. Формула изобретения Дискретный фазовращатель, содержащий источник управляющего , фазовращатель, вход которого подключен к первому входу первого умножителя сигналов, выход фазовращателя подключен к порвому входу второго умножителя сигналов, выходы первого и второго умиожи-телой сигналов подключены ко входам су матора, отличающийся том, что, сцелью получен1 я дискретных (:)м(х сдпи- гов синусоидального сигнала с наименьшими амплитудными и фазовыми искажениями, в него введены импульсный генератор, два элемента совпадения, два делителя частоты из 17Ьтриг1еров каждый, два блока дифференцирования, два кЛюча, две запоминающие емкости, фильтр ниэ- ких частот, причем выход импу/ьсного генератора подключен непосредственно ко входу первого делифеля частоты и через первый элемент совпадения - ко входу второго делителя частоты, второй вход первого элемента совпадения подклю чен к выходу источника управляющих сиг налов, внход первого делителя частоты через фильтр низких частот соединен со вторыми входами первого и второго ключ выход второго делителя частоты подключ непосредственно к первому входу второго элемента совпадения и через первый блок дифференцирования к первому входу первого ключа, выход которого соединен с первой запоминающей емкостью и со вторым входом первого умножителя сигналов, выход ( )-го триггера второго делителя частоты через второй элемент совпадения и второй блок дифференцирования подключен к первому входу второго ключа, выход соединен со второй запоминающей емкостью и со вторым входом второго умножителя сигналов. Источники информации, принятые -во внимание при экспертизе 1, Патент США № 3475626, кл, Н 03 К 17/28, 1971.

и

t

t

Ul.i

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр с оптимальным квантованием | 1988 |

|

SU1569741A1 |

| Цифровой фазометр | 1984 |

|

SU1234779A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU596993A1 |

| Умножитель частоты | 1978 |

|

SU798831A1 |

| Программный генератор | 1983 |

|

SU1190484A1 |

| Управляемый фазовращатель | 1985 |

|

SU1282311A1 |

| Преобразователь составляющих комплексных сопротивлений | 1986 |

|

SU1430908A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Инфранизкочастотный программный генератор | 1980 |

|

SU919055A1 |

| Дискретный умножитель частоты повторения импульсов | 1977 |

|

SU692065A1 |

Авторы

Даты

1979-04-15—Публикация

1976-05-17—Подача