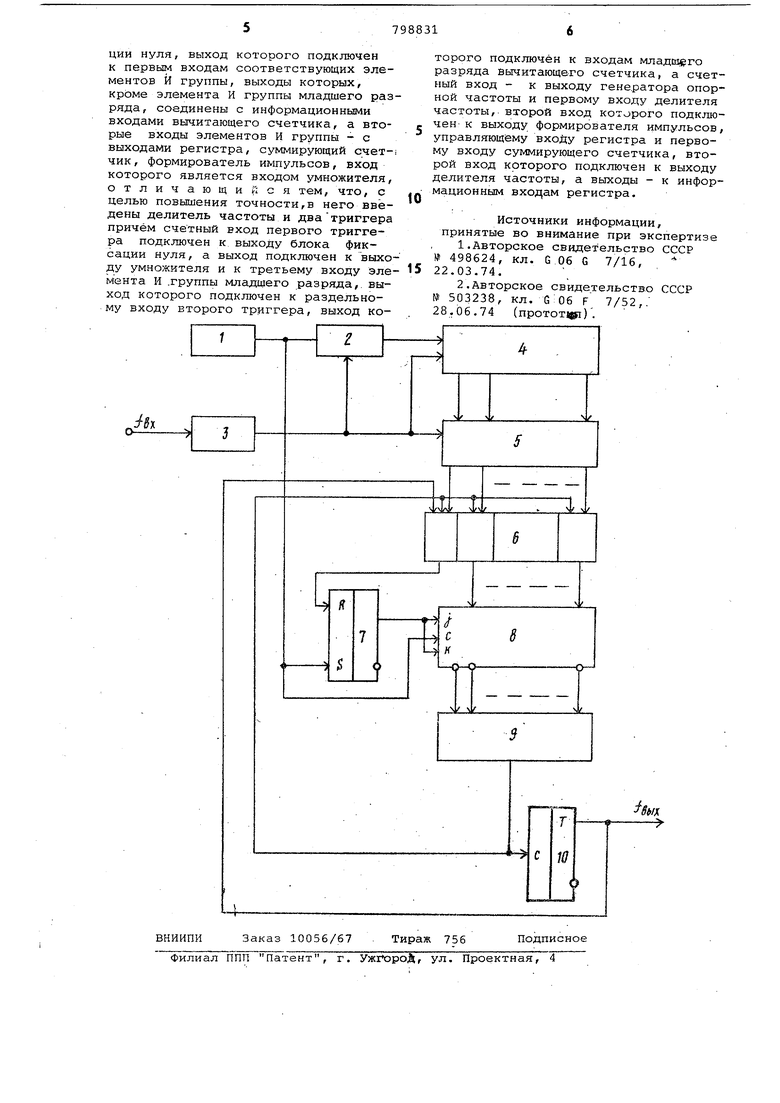

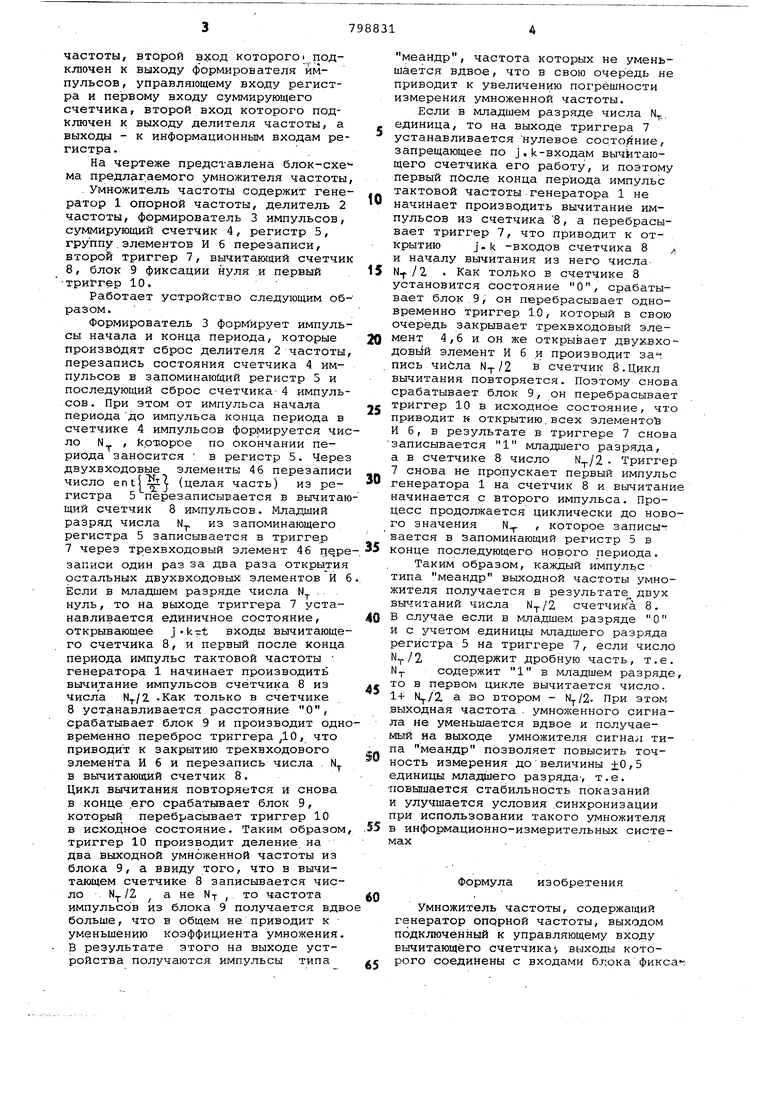

Изобретение относится к измерите ной технике и, в частности, может найти применение в информационноизмерительных и управляющих система где требуется синхронизация работы вторичных измерительных устройств, а также повышение быстродействия и точности измерения. Известен умножитель частоты, содержащий счетчики, генератор тактовых импульсов, блок сравнения, два делителя частоты, регистр, триггер, управления и элементы И, ИЛИ Недостатком его является малая точность измерения полученной частоты на выходе. Наиболее близким к предлагаемому является -умножитель частоты, содержащий генератор опорной частоты, последовательносоединенные суммиру щий счетчик, схему записи, регистр, схему переноса и вычитающий счетчик а также формирователь импульсов, сх му дифференцирования ираспределени управляющий триггер, вспомогательны счетчик, схему фиксации нуля, два ключа и дополнительный опорный, гене ратор 2j . Недостатком его является также низкая точность. Цель изобретения - повышение точности умножения. Поставленная цель достигается тем, что в умножитель частоты, содержеиций генератор опор-ной частоты, выходом подключенный к управляющему входу вычитающего счетчика, выходы которого соединены с входами блока фиксации нуля, выход которого подключен к первым входам соответствующих элементов И группы, выходы которых, кроме элемента И группы младшего разряда, соединены с информационными входами вычитающего счетчика, а вторые входы элементов И группы - с выходами регистра, суммирукнций счетчик, формирователь импульсов, вход которого является входом умножителя, в него введены делитель частотыи два триггера, причем сче.тный вход первого триггера подключен к выходу блока фиксации нуля, а выход подключен к выходу умножителя и к третьему входу элемента и группы младшего разряда, выход которого подключен к раздельному входу второго триггера, выход которого ;подключен к входам младшего разряда вычитающего счетчика, а счетный .вход - к выходу генератора опорной частоты к первому входу делителя частоты, второй вход которого подключен к выходу формирователя импульсов , управляющему входу регистра и первому входу суммирующего счетчика, второй вход которого подключен к выходу делителя частоты, а выходы - к информационным входам регистра. На чертеже представлена блок-схе ма предлаг.аемого умножителя частоты . Умножитель частоты содержит гене ратор 1 опорной частоты, делитель 2 частоты, формирователь 3 импульсов, суммируюгдий счетчик 4, регистр 5, группу.элементов И 6 перезаписи, второй триггер 7, вьочитающий счетчи 8, блок 9 фиксации нуля и первый триггер 10. Работает устройство следующим об разом. Формирователь 3 формирует импуль сы начала и конца периода, которые производят сброс делителя 2 частоты перезапись состояния счетчика 4 импульсов в запоминающий регистр 5 и последующий сброс счетчика-4 импуль сов. При этом от импульса начала периода до импульса конца периода в счетчике 4 импульсов фор лируется чи ло N , по окончании периода заносится . в регистр 5. Чере двухвходовые элементы 46 перезапис число entjU; (целая часть) из регистра 5 перезаписывается в вычита щий счетчик 8 импульсов. Младщий разряд числа N из запоминающего регистра 5 записывается в триггер 7 через трехвходовый элемент 46 записи один раз за два раза открытия остальных двухвходовых элементов И Если в младшем разряде числа N . . . нуль, то на выходе триггера 7 устанавливается единичное состояние, открывающее jk-t входы вычитающе го счетчика 8, и первый после конца периода импульс тактовой частоты генератора 1 начинает производить вычитание импульсов счётчика 8 из числа -Как только в счетчике . 8 устанавливается расстояние О, срабатывает блок 9 и производит одн временно переброс триггера,О, что приводит к закрытию трехвходового элемента И 6 и перезапись числа N в вычитающий счетчик 8. Цикл вычитания повторяется и снова в конце его срабатьшает блок 9, который перебрасывает триггер 10 в исходное состояние. Таким образом триггер 10 производит деление на два выходной умноженной частоты из блока 9, а ввиду того, что в вычитающем счетчике 8 записывается число а не NT , то частота импульсов из блока 9 получается вдв больше, что в общем не приводит к уменьщению коэффициента умножения - В результате этого на выходе устройства получаются импульсы типа меандр, частота которых не уменьшается вдвое, что в свою очередь не приводит к увеличению погрешности измерения умноженной частоты. Если в младшем разряде числа N.. единица, то на выходе триггера 7 устанавливается нулевое сос.тойние, запрещающее по j,k-вxoдaм вычитающего счетчика его работу, и поэтому первый после конца периода импульс тактовой частоты .генератора 1 не начинает производить вычитание импульсов из счетчика 8, а перебрасывает триггер 7, что приводит к открытию j,k -входов счетчика 8 и началу вычитания из него числаN /2 . Как только в счетчике 8 установится состояние О, срабатывает блок . 9, он перебрасывает одновременно триггер 10, который в свою очередь закрывает трехвходовый элемент 4,6 и он же открывает двухвходовь{й элемент И 6 и производит за пись чийла в счетчик 8.Цикл вычитания повторяется. Поэтому снова срабатывает блок 9, он перебрасывает триггер 10 в исходное состояние, что приводит к открытию.всех элементов И 6, в результате в триггере 7 снова записывается 1 младшего разряда, а в счетчике 8 число Триггер 7снова не пропускает первый импульс генератора 1 на счетчик 8 и, вычитание начинается с второго импульса. Процесс продолжается циклически до нового значения N. , которое записывается в запоминающий регистр 5 в конце последующего нового периода. Таким образ.ом, каждый импульс типа меандр выходной частоты умножителя получается в результате двух вычитаний числа счетчика 8. 8случае если в младшем разряде О и с учетом единицы младшего разряда регистра 5 на триггере 7, если число содержит дробную часть, т.е. NT- содержит 1 в младшем разряде, то в первом цикле вычитается число. 1-1- ЬЦ./2. а во втором - . При этом выходная частота . умноженного сигнала не уменьшается вдвое и получаемый на выходе умножителя сигнал типа меандр позволяет повысить точность измерения довеличины +0,5 единицы младшего разряда-, т.е. -повышается стабильность показаний и улучшается условия синхронизации при использовании такого умножителя в информационно-измерительных системахФормула изобретения Умножитель частоты, содержащий генератор опорной частоты, выходом подключенный к управляющему входу вычитающего счетчика , выходы которого соединены с входами блока фикса

ции нуля, выход которого подключен к первым входам соответствующих элементов И группы, выходы которых, кроме элемента И группы младшего разряда, соединены с информационными входами вычитающего счетчика, а вторые входы элементов И группы - с выходами регистра, суммирующий счет-i чик, формирователь импульсов, вход которого является входом умножителя, отличающийся тем, что, с целью повышения точности,в него введены делитель частоты и два триггера причём счетный вход первого триггера подключен к выходу блока фиксации нуля, а выход подключен к выходу умножителя и к третьему входу элемента И .группы младшего разряда,, выход которого подключен к раздельному входу второго триггера, выход которого подключён к входам младшего разряда ВЕЛчитающего счетчика, а счетный вход - к выходу генератора опорной частоты и первому входу делителя частоты, второй вход которого подключен к выходу формирователя импульсов, управляющему входу регистра и первому входу суммирующего счетчика, второй вход которого подключен к выходу делителя частоты, а выходы - к информационным регистра.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 498624, кл. G Об G 7/16,

5 22.03.74.

2.Авторское свидетельство СССР № 503238, кл. G 06 f 7/52,. 28.06.74 (прототадт).

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель-нормализатор частотныхСигНАлОВ | 1979 |

|

SU847505A1 |

| Множительно-делительное устройство | 1979 |

|

SU830379A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

Авторы

Даты

1981-01-23—Публикация

1978-10-24—Подача