I Изобретение относится к радиотехнике, в частности к цифровой измерительной технике и может быть применено в цепях преобразовании сигналов для повышения быстродействия в области низких частот. Известен дискретный умножитель частоты импульсов, содержащий устройство, к которому поступают входные сигналы, и генератор зталонного сигнала. Первый счётчик устройства исполь зуется для подсчета числа эталонных сигналов генератора, поступающих в каждый период вход ных сигналов. Оно также содержит устройство для непрерывного преобразования каждого из входных цифровых сигналов счетчика импульсов в отличное от начального преобразованное число. Второй счетчик импульсов используется для подсчета числа эталонных сигналов генерато ра, поступающих в каждый период выходаых сигналов. Компаратором устройства определяется период выходного сигнала при сравнении сиг нала второго счетчика и преобразованного сигнала первого счетчика, хранящегося в устройстве памяти 1. Недостатком этого устройства является неравномерность выходных импульсов. Это объясняется тем, что код преобразоваяного сигнала первого счетчика не является кратным коду периода входного сигнала. Вторым недостатком является то, что код на выходе преобразователя, ОТЛ1ГЧНЫЙ от начального, представляет собой не что иное, как дополнительныйкод, и поэтому, естественно, с увеличением частоты входного сигнала частота выхо|р1ого сигнала будет уменьшаться. Из известных устройств наиболее близким по технически сущности является дискретный улв ожителъ частоты, вьшолненный по двухтактной схеме и содержащий входной формирователь, сооданенный с управляющим триггером, двоичный умножитель, состоящий из счетчика, группы схем совпадения и схемы ИЛИ, два устройства квантования, состоящих из управляющего счетчика, вход которого соединен с выходом ключа, а выход - с входом ус-фойства автоматического изменения частоты квантования, входы которого через делитель частоты импульсов подключены к выходу управляемого генератоpa опорной частоты, две группы схем совпадения со схемами ИЛИ на выходе, ключи, схемы ИЛИ и устройство вычитания, состоящее из триггера и ключа, один вход которого соединен с выходом упомянутого триггера, причем потенциальные входы двух групп схем совпадения подключены к выходам разрядов управляющих счетчиков, а импульсные - к выходам разрядов счетчика двоичного умножителя, входом соединенного с выходом ключа устройства вычитания, второй вход которого и один вход триггера устойства вычитания через одну дополнительную схему ИЛИ и дополнительные ключи соединен с выходом устройства автоматического изменения частоты квантования, а другой вход триггера устройства вычитания подключен к выходам схем ИЛИ двух групп схем совпадения через вторую дополнительную схему ИЛИ и вторые дополнительные ключи, управляющие входы которых, а также управляюище входы первых дополнитель-i ных ключей соединены с выходом управляющего триггера 2.

Недостатком этого технического решения является неравномерность последовательности выходных импульсов и его относительная сложность.

Цель изобретения - расширение частотного диапазона и полу еггае равномерности импульсов выходной последовательности.

Поставленная цель достигается тем, что в дискретный умножитель частоты повторения импульсов, содержащий входной формирователь импульсов, выход которого соединен со входом управляющего триггера, ключи, первый вход каждого из которых соединен с одним из выходов управляющего триггера, два управляющих счетчика им- . пульсов, к первым входам каждого из которых подключен .вьгход соответствующего блока сброса, вход каждого из которых соединен с соответствующим выходом управляющего триггера, ко вторым входам - выходы соответственно,первого и второго клютай, а выходы всех )азрядое управляющих счетчиков импульсов соединены с первыми группами входов соответственно первого и второго блоков совпадения, ко вторым группам входов которых подключены .выходы каждого разряда умножающего счетчика, а к выходам через соответственно третий и четвертый ключи подключены входы элемента ИЛИ, и делитель частоты, вход которого соединен с выходом управляемого генератора опорной частоты, введены дополнительный блок сброса, выход которого подключен ко входу умножающего счетчика импульсов, первый и второй входы соединены с выходами управляющего триггера, а третий - подключен к выходу элемента ИЛИ, при этом вход управляемого генератора опорной частоты соединен с выходом входного формирователя импульсов, выход подключен к одному из входов умножающего счетчика импульсов, а выход делителя частоты через первый и второй ключи соединен со входами соответствующих управляющих счетчиков импульсов.

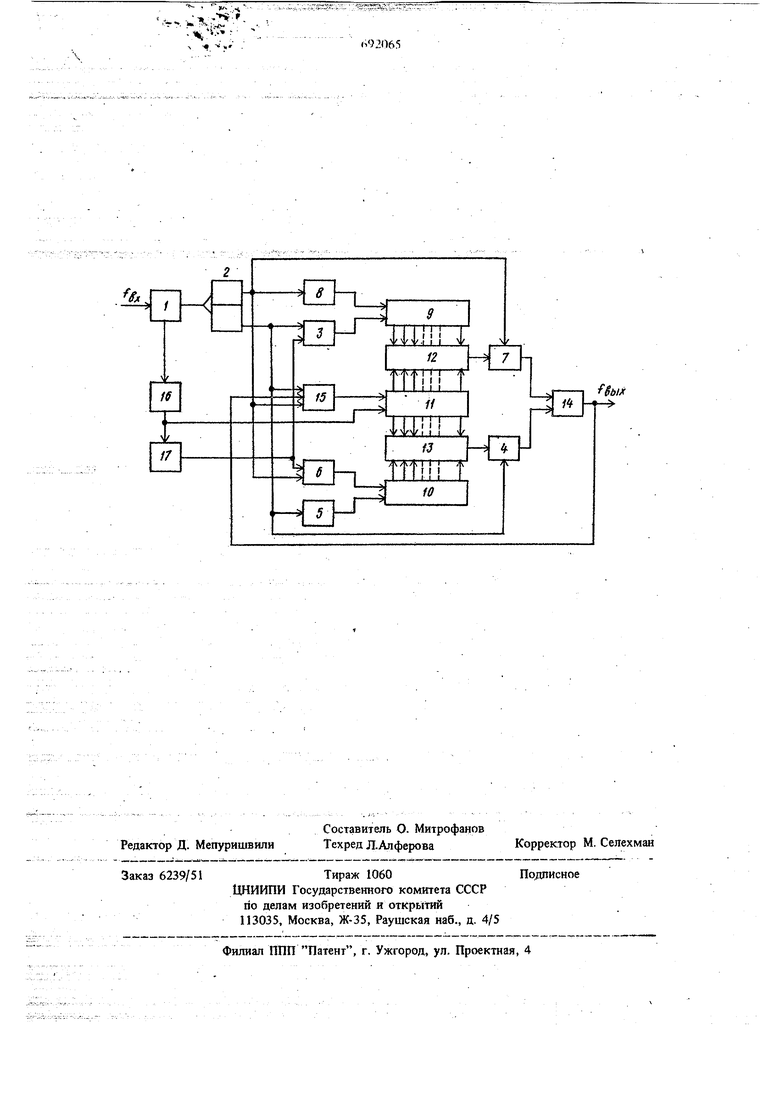

Сущность изобретения поясняется чертежом, где изображена структурная электрическая схема дискретного умножителя частоты повторения импульсов.

Он состоит из формирователя I, на вход которого поступают импульсы входной частоты. Выход формирователя подключен ко входу уп.равляющего триггера 2. Один из потенщтальных выходов триггера 2 управляет работой первого и четвертого ключей 3 и 4 и подключен ко входу пегвого блока сброса 5..Другой потенциальный выход управляющего триггера управляет работой второго и третьего ключей 6 и 7 и подключен ко входу второго блока сброса 8. Все эти устройства управляют работой двухтактного умножителя, который состоит из двух зшравляющих счетчиков 9 и 10 импульсов, умножающего счетчика 11 импульсов и двух блоков совпадения 12 и 13. Выходные сигналы которых через третий и четвертый ключи 4 и 7 поступают на входы элемента ИЛИ 14, выход которого является выходом всего устройства и одновременно подключен ко входу дополнительного блока сброса 15, который устанавливает умножающий счетчик И импульсов в исходное состояние. Все блоки сброса подключены к установочным входам счетчиков импульсов и устанавливают посление в исходное состояние. Выход управляющего генератора опорной частоты 16 подключен ко входу умножающего счетчика 11 импульсов и ко входу делителя 17 частоты. Выход делителя 17 подключен через первый и второй ключи 3 и 6 ко-входам управляющих счетчиков 9, 10 импульсов.

Работает дискретный умножитель тастоты следующим образом.

Входной сигнал поступает на формирователь 1, с выхода которого сформированный сигнал поступает на счетный вход управляющего триггера 2 и на вход управляемого генератора опорной частоты 16, частота которого изменяется пропорционально частоте входных сигналов. С выхода управляемого генератора опорной частоты сигнал в виде опорной частоты поступает на делитель 17 и на вход счетчика И, а частота с выхода делителя 17 через ключи 3, 6 - на вход управляющих (летчиков 9 и 10, в зависимости от состояния управляющего триггера 2. Счетчик 9 и 10 и 11 имеют равное количество разрядов, но поскольку счетчик умножителя П считает импульсы опорной частоты с управляемо,го генератора опорной частоты 16, а управляюцще счетчики 9 .или IО считают импульсы с вы;хода делителя 17, то на умножающем счетчике ТОТ же код числа, что и на управляющем счетчике 9 (или 10) запишется за интервал времени в N раз меньший, чем на управляющем счетчике 9 (или 10), где N коэффициент деления делителя частоты 17, Предположим, что в исходном состоянии управляющий триггер 2 установился в такое состояние, что открыты кл чи 6 и 7. С приходом импульса входной частоты ключи 6, 7 закроются, а ключи 3, 4 откроются. В момент перехода управляющего триггера 2 в новое состояние схема сброса 6 выработает им пульс и установит управляющий счетчик 9 в исхош ое состояние. После открывания ключа 3 на вход -управляюшего счетчика 9 поступит частота управляемого генератора опорной частоты 16, поделенная делителем частоты 17. С приходом следующего импульса входной частоты управляющий триггер 2 изменит свое состояние, блоки сброса 5 и 15 своим импульсом установят управляющий счетчик 10 и умножающий счетчик 11 в исходное состояние, закроются ключи 3, 4 и откроются ключи 6, 7. За время между импульсами входной частоты в управляющем счегшке 9 запишется определенный код, он выполняет в дальнейшем роль оперативного запоминающего устройства, код которого непрерьюно сравнивается с кодом умножающего счетчика 11 с помощью блока совпадения 12. В момент равенства кодов с выхода блока совпадения 12 через ключ 7 и злемент ИЛИ 14 на выход устройства проходит выходной импульс. Од новременно этот импульс поступает на блок сброса 15, который устанавливает умножающий счетчик 11 в исходное состояние. Этот цикл повторяется п раз. В это.же время в управляющий счетчик 10 записывается код. С приходом следующего импульса входной частоты управ1Ляющие счетчики 9 и 10 меняют свои функции и вступает в работу блок совпадения 13. Продесс повторяется. Данное, рещение позволяет расширить частотный диапазон схемь умножения частоты и получить на выходе равномерную последовательность выходных импульсов, что особенно важно для применения данного устройства в качестве синхронизатора. Кроме того, данное изобретение позволяет получить более высокую точность умножения. Это объясняется тем, что опорная частота меняется пропорционально входной частоте и относительная длительность периода опорной частоты на которую возможна ошибка, практически остается постоянной во всем диапазоне умножаемых частот. Это же приводит к тому, . что код двоичного умножителя, записанного в управляющих счетчиках 9, 10 остается практически постоянным во всем диапазоне умножаемых частот. Величина опорной частоты выбирается из заданной точности умножения, а объем счетчиков таким, чтобы они были максимально заполнены, но не переполнились. Данное устройство позволяет при заданной точности су1дественно сократить объемы счетчика. Формула изобретения Дискретный умножитель частоты повторения импульсов, содержащий входной формирователь импульсов, выход которого соедвден со входом управляющего триггера, ключи, первый вход каждого из которых соединен с одним из выходов управляющего триггера, два управляющих счетчика импульсов, к первым входам каждого из которых подключен выход соответствуюп1его блока сброса, вход каждого из которых соединен с соответств5аои1Им выходом управляющеготриггера, ко вторым входам - выходы соответственно первого и второго ключей, а выходы всех разрядов управляющих счетчиков импульсов соединены с первыми группами входов соответственно первого и второго блоков совпадения, ко вто|)ым группам входов которых подключены выходы каждого ргазряда ул-шожающего счетчика, а к выходам через соответственно третий и четвертый ключи подключены входы элемента ИЛИ, и делитель частоты, вход которого соединен с выходом управляющего генератрра опорной частоты, отличающийся тем, что, с целью расширения частотного диапазона и получения равномерности импульсов выходной последовательности, в него введен дополнительный блок сброса, выход которого подключен ко- входу умножающего счетчика импульсов, первый и второй эходы соеддаены с выходами управляющего триггера, а третий - подключен к выходу злемента ИЛИ, при зтом вход управляемого генератора опорной «частоты соеданен с выходом входного формирователя импульсов, выход подключён к одному из входов умножающего счетчика имяульсов, а выход делителя частоты через первый и второй ключи соединен со входами соответствующих управляющих счетчиков импульсов. Источники информации, принятые во внимание при экспертизе 1.Патент США W 3970954, кл. Н 03 В 19/00, 1975. 2.Авторское свидетельство СССР № 375783, кл. Н 03 К 13/20, 1974 (прототип).

.Ч

. V v- -:--. VSHV

- -ч --:ч .

.)2065

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1972 |

|

SU425315A1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1140220A1 |

| Умножитель частоты | 1978 |

|

SU758473A1 |

| Умножитель частоты | 1983 |

|

SU1176439A1 |

| Цифровой умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU824440A1 |

| ДИСКРЕТНЫЙ УМНОЖИТЕЛЬ ЧАСТОТЫ | 1973 |

|

SU375783A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Умножитель частоты периодических импульсов | 1983 |

|

SU1108610A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

febIJi

Авторы

Даты

1979-10-15—Публикация

1977-07-11—Подача