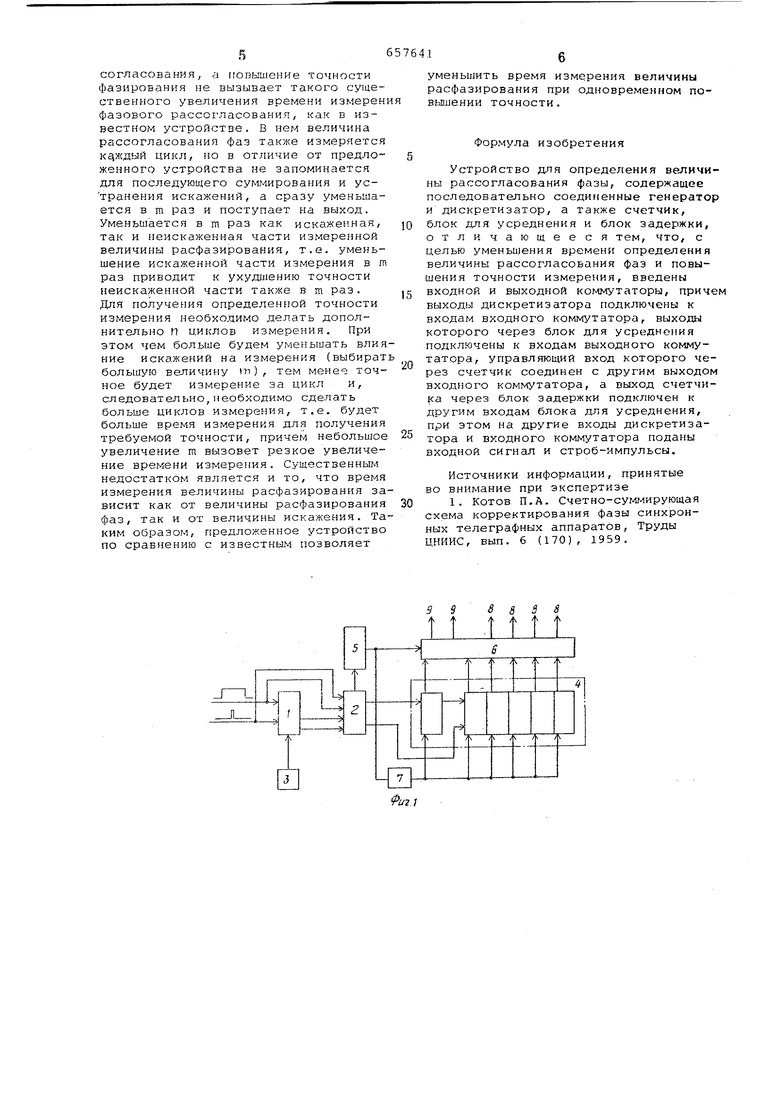

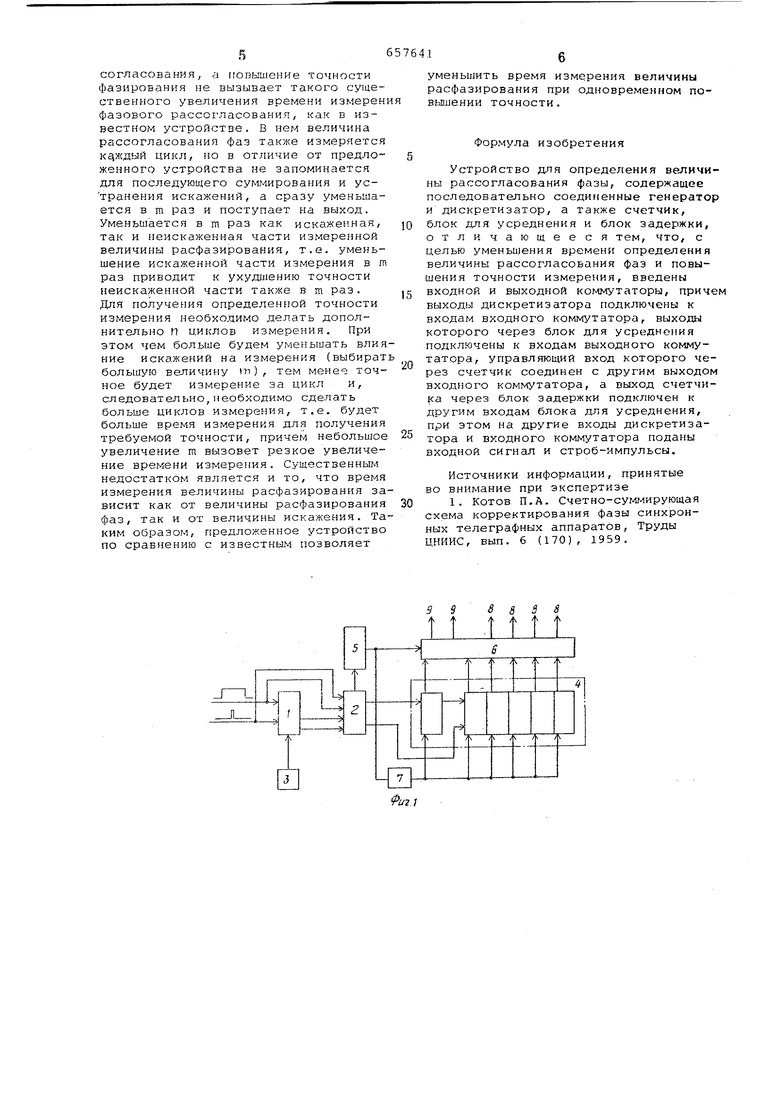

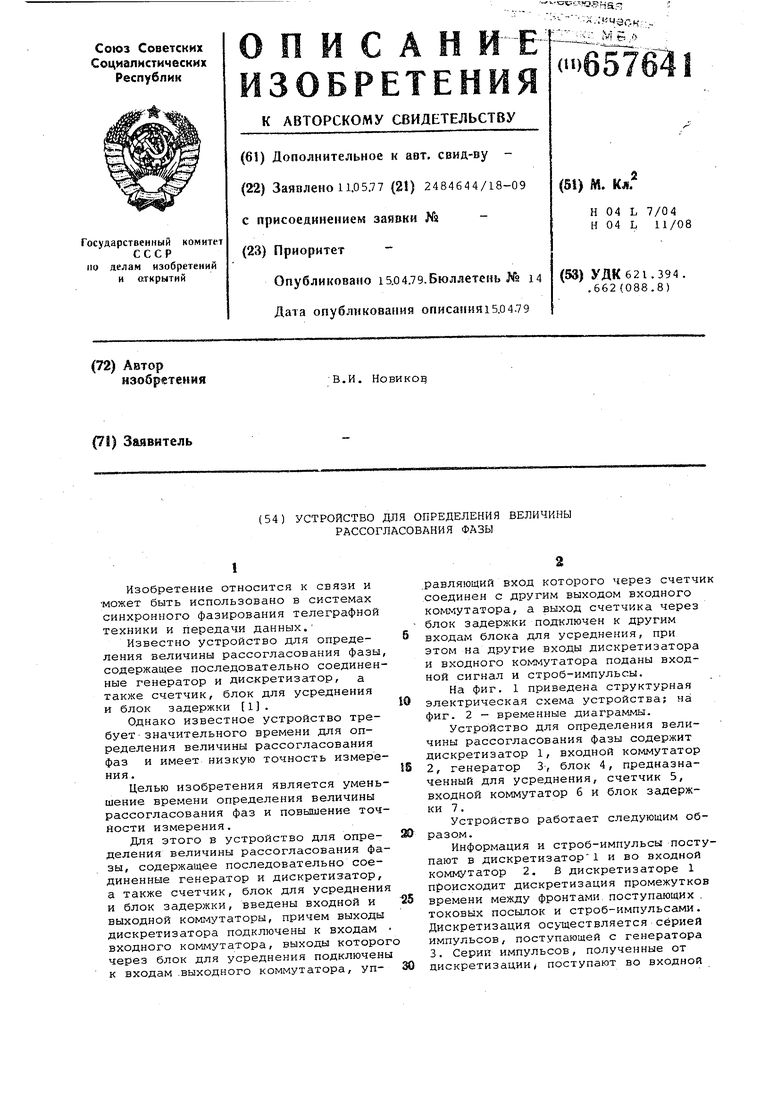

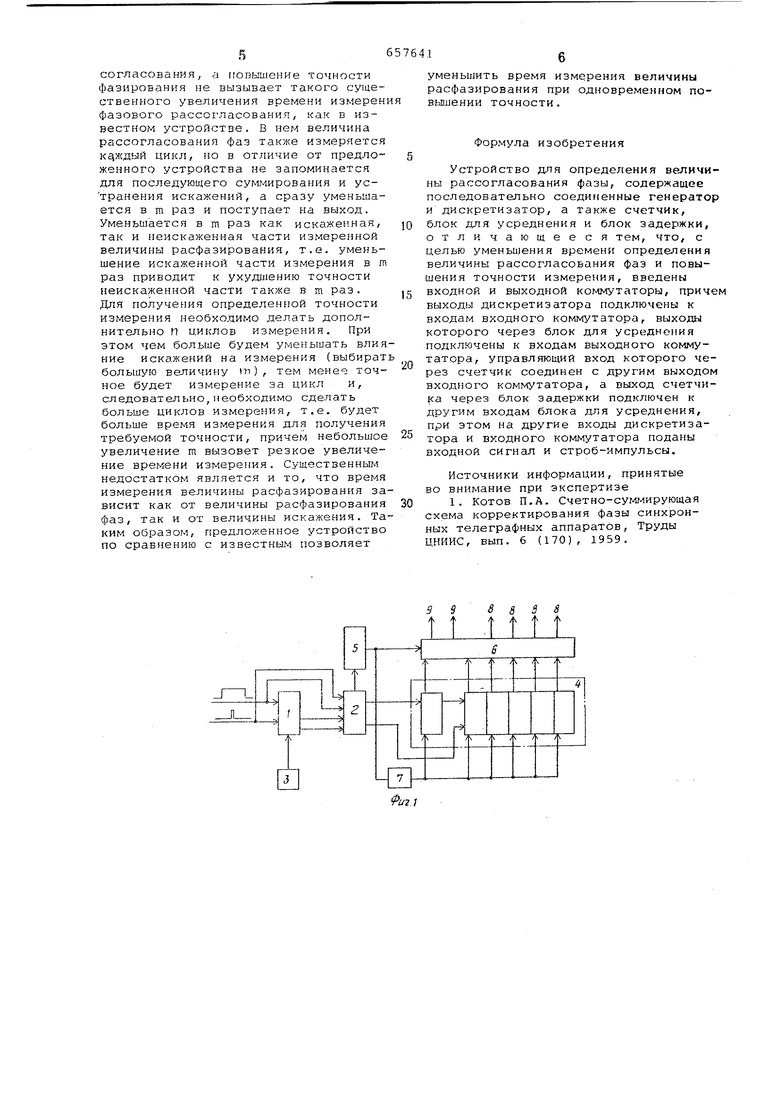

KONw/iyTaTop 2 no двум входам. По первому входу поступает серия импульсов полученная от дискретизации промежутка времени Г от переднего фрон та до строб-импульса, а по второму входу поступает серия им11ульсов, полученная от дискретизации промежутка времени С от заднего фронта до строб-импульса. При наличии преобладаний импульсы дискретизации могут поступать во входной коммутатор 2 одновременно по двум входам. Входной коммутатор 2 коммутирует эти серии дискретизации на счетный вход первого разряда. На время, когда импульсы дискретизации появляются одновременно на обоих Входах, коммутация осуществляется на дополнительный счетный вход второго разряда. Этим обеспечивается подсчет импульсов дискретизации, появляющихся одновременно по двум входам входного коммутатора 2. Тем самым исключаем резуль таты измерения. При отсутствии.фазового рассогласования ( + - TO , где Т - длительность элементарной посылки) на счетные входы блока усреднения 4 поступят импульсы дискретизации под действием которых блок 4 примет 2 N состояний {N - коэффициент деле ния делителя формирователя строб-импульсов и соответствует количеству импульсов, полученных от дискретизации элементарной токовой посылки). При опережении строб-импульсов по фа зе ( Cg - TQ ) на счетные входы бло ка 4 поступают импульсы дискретизаци под действием которых блок 4 (счетчик) примет количество состояний мен ше 2N(), а при отставании( блок 4 примет количество состояний больше 2N{2N-f4N). Изменение состояни блока 4 (счетчика) при поступлении на его счетные входы импульсов дискретизации, а также соответствие меж ду сосггоянием блока 4 и двоичным кодом на выходах 8 выходного коммутато ра б поясняется диаграммой, изображенной на фиг. 2, Из диаграммы видно, что по мере поступления импульсов на входы блока 4 (см.. фиг. 2 б) состояния его изменяются (см.фиг.2в) У блока 4 может быть 2N различных состояний. При отсутствии фазово рассогласования блок 4 примет 2N раз личных состояний и с пocтvплeниeм 2N импульса 3 блоке 4 установится состо яние (О . . ..0000 ) .На выходах 8 выходно го коммутатора 6 код величины рассог ласования будет отсутствовать.При от ставании количество импульсов,поступивших на счетный вход, будет больше 2N. С поступлением на счетный вход 2N импульсов установится состояние 0.. 0000, а при дальнейшем поступлении импульсов на счетный вход состоя ние блока 4 будет повторяться и к моменту появления сигнала на выходе счетчика 5 в блоке 4 установится состояние, соответствующее сумме четырех измерений величины расфазирования, Деление на четыре осуществляют путем отбрасывания двух младших разря.цов прямого кода состояния блока 4, т.е. по сигналу со счетчика 5 на выходы 8 выходного коммутатора 6 необходимо скоммутировать прямой код состояния блока 4 без двух младших разрядов, а на выходы 9 - сигнал отставания ( + ) . При оперелсении количество импульсов, поступающих на счетный вход блока 4, будет меньше 2N. К моменту появления сигнала на выходе счетчика 5 в блоке 4 установится состояние, соответствующее сумме четырех измерений величин расфазирования. При этом на выход необходимо скоммутировать обратный код, состояния блока 4 без двух младших разрядов, а на выходы 9 - сигнал опережения (-). На фиг. 2а без скобок показаны обратные двоичные коды, которые кoм iyтиpyет выходной коммутатор б при опережении по фазе, а с скобках - прямые двоичные коды, которые ком1-1утирует выходной Kot-лмутатор б при отставании. Из диаграмм видно, что при отставании с возрастанием двоичного кода состояния счетчика возрастает и двоичный код величины расфазирования, а при опережении - наоборот. Из диаграммы видно, что четырем рядом стоящим состояниям счетчика 5 соответствует один двоичный код расфазирования. После выдачи выходным коммутатором б двоичного кода расфазирования блок 4 приводится в исходное состояние и,тем самым подготавлива.ется к следующему циклу измерения . В предложенном устройстве величина рассогласования, определенная за каждый цикл измерения, является промежуточным результатом измерения и на выход неПоступает. Она запоминается, суммируется между собой за m циклов (4 цикла), и после деления суммы на гп результат деления выдается на выход. Результат деления суммы на кп является средним арифметическим значением величины рассогласования. Предварительный замер за один цикл измерения состоит из искаженной и неискаженной частей, искажение может и отсутствовать. Поэтому получение среднего арифметического значения величины рассогласования за m циклов позволяет исключить искажения противоположных знаков, а остав1ииеся искажения одного знака уменьшить в пч раз. Следовательно, чем больше т циклов замера, тем больше точность, т.е. больше искажений будет взаимно уничтожаться, и оставшиеся искажения одного знака будут уменьшены еще больше. При этом время измерения величины расфазирования не зависит от величины фазового рассогласования, а гговышение точности фазирования не вызывает такого существенного увеличения времени измерен фазового рассогласования, как в известном устройстве. В нем величина рассогласования фаз также измеряется каждый цикл, но в отличие от предложенного устройства не запоминается для последующего суммирования и устранения искажений, а сразу уменьшается в m раз и поступает на выход. Уменьшается в m раз как искаженная, так и неискаженная части измеренной величины расфазирования, т.е. уменьшение искаженной части измерения в m раз приводит к ухудишнию точности неискаженной части также в m раз. Для получения определенной точности измерения необходимо делать дополнительно П циклов измерения. При этом чем больше будем уменьшать влия ние искажений на измерения (выбират большую величину ш), тем менеч точное будет измерение за цикл и, следовательно,необходимо сделать больше циклов измерения, т.е. будет больше время измерения для получения требуемой точности, причем небольшое увеличение m вызовет резкое увеличение времени измерения. Существенным недостатком является и то, что время измерения величины расфазирования за висит как от величины расфазирозания фаз, так и от величины искажения. Та ким образом, предложенное устройство по сравнению с известны. позволяет уменьшить время измерения величины расфазировакия при одновременном повышении точности. Формула изобретения Устройство для определения величины рассогласования фазы, содержащее последовательно соединенные генератор и дискретизатор, а также счетчик, блок для усреднения и блок задержки, отличающееся тем, что, с целью уменьшения времени определения величины рассогласования фаз и повышения точности измерения, введены входной и выходной коммутаторы, причем выходы дискретизатора подключены к входам входного коммутатора, выходы которого через блок для усреднения подключены к входам выходного коммутатора, управляющий вход которого через счетчик соединен с другим выходом входного коммутатора, а выход счетчика через блок задержки подключен к другим входам блока для усреднения, при этом на другие входы дискретизатора и входного коммутатора поданы входной сигнал и строб-импульсы. Источники информации, принятые во внимание при экспертизе 1. Котов П.А. Счетно-суг-5мирующая схема корректирования фазы синхронных телеграфных аппаратов, Труды ЦНКИС, вып. 6 (170) , 1959.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Цифровой фазометр | 1986 |

|

SU1287037A1 |

| Устройство дискретного фазирования | 1980 |

|

SU1016847A1 |

| Устройство для отсчета времени | 1985 |

|

SU1379771A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Устройство управления моментом зажигания | 1981 |

|

SU1013634A1 |

| Устройство для сглаживания периодических случайных сигналов | 1983 |

|

SU1242987A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

9 9 S S 3 S

t 1 . t t

sl

Q Сз О

l() 3() 5() . , / ,

2() : 4( () S() 2fi-(fN-) 2H-2(«N-2) 2HiUN}

2 §

Сэ

СЭ Cj

i2

I I i

§

§

«aca СЭ Q

ci СЭ

c

сэ

§

if

cj iZ

cj Q

j:

Авторы

Даты

1979-04-15—Публикация

1977-05-11—Подача