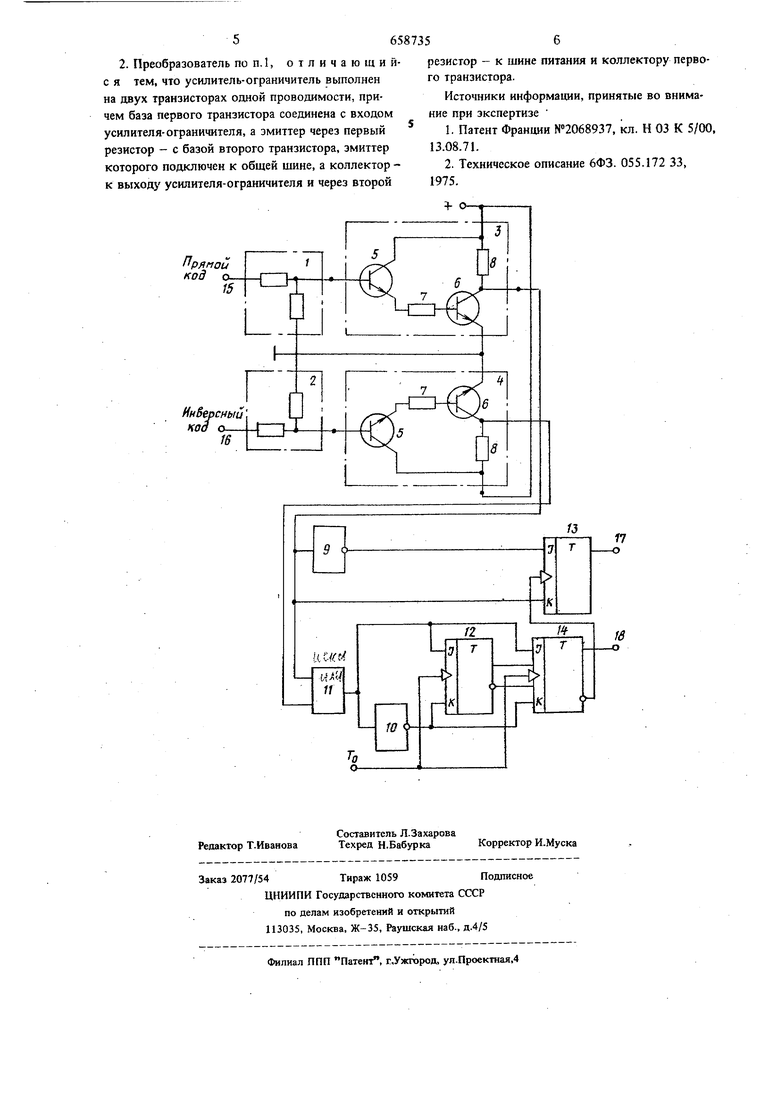

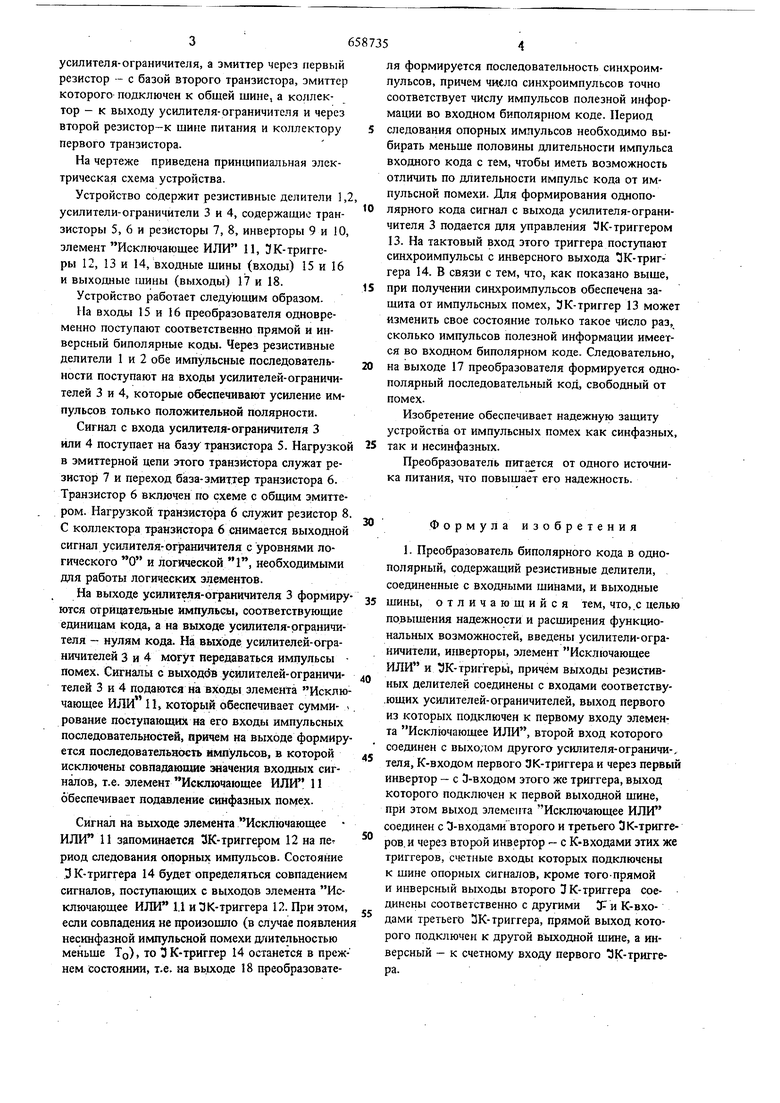

усилителя-ограничителя, а эмиттер через первый резистор - с базой второго транзистора, эмиттер которого подключен к общей шине, а коллектор - к выходу усилителя-ограничителя и через второй резистор-к шине питания и коллектору первого транзистора. На чертеже приведена принципиальная электрическая схема устройства. Устройство содержит резистивные делители 1,2 усилители-ограничители 3 и 4, содержащие транзисторы 5, 6 и резисторы 7, 8, инверторы 9 и 10, элемент Исключаюшее ИЛИ 11, ЭК-триггеры 12, 13 и 14, входные шины (входы) 15 и 16 и выходные шины (выходы) 17 и 18. Устройство работает следуюшим образом. На входы 15 и 16 преобразователя одновременно поступают соответственно прямой и инверсный биполярные коды. Через резистивные делители 1 и 2 обе импульсные последовательности поступают на входы усилителей-ограничителей 3 и 4, которые обеспечивают усиление импульсов только положительной полярности. Сигнал с входа усилителя-ограничителя 3 или 4 поступает на базу транзистора 5. Нагрузкой в змиттерной цепи этого транзистора служат резистор 7 и переход база-змит.тер транзистора 6. Транзистор 6 включен по схеме с общим эмиттером. Нагрузкой транзистора 6 служит резистор 8 С коллектора транзистора 6 снимается выходной сигнал усилителя-ог заничителя с уровнями логического О и логической 1, необходимыми для работы логических элементов. На выходе усилителя-ограничителя 3 формиру ются отрицательные импульсы, соответствующие единицам кода, а на выходе усилителя-ограничителя - нулям кода. На выходе усилителей-ограничителей 3 и 4 могут передаваться импульсы помех. Сигналы с выходов усилителей-ограничителей 3 и 4 подаются на входы элемента Исклю чаюшее или II, который обеспечивает сумми- л рование поступающих на его входы импульсных последовательностей, причем на выходе формиру ется последовательность импульсов, в которой исключены совпадающие жачения входных сигналов, т.е. элемент Исключающее ИЛИ 11 обеспечивает подавление синфазных помех. Сигнал на выходе элемента Исключающее ИЛИ II запоминается Ж-триггером 12 на пег риод следования опорных импульсов. Состояние ЗК-триггера 14 будет определяться совпадением сигналов, поступающих с выходов элемента Исключающее ИЛИ 1.1 и 3 К-триггера 1.. При этом если совпадения не произошло (в случае появлени несинфазной импульсной помехи длительностью меньше TQ), то tJ К-триггер 14 останется в преж нем состоянии, т.е. на выходе 18 преобразовате64 я формируется последовательность синхроимульсов, причем число синхроимпульсов точно соответствует числу импульсов полезной информации во входном биполярном коде. Период следования опорных импульсов необходимо выбирать меньше половины длительности импульса входного кода с тем, чтобы иметь возможность отличить по длительности импульс кода от импульсной помехи. Для формирования однополярного кода сигнал с выхода усилителя-ограничителя 3 подается для управления tIK-триггером 13. На тактовый вход этого триггера поступают синхроимпульсы с инверсного выхода tlK-триггера 14. В связи с тем, что, как показано выше, при получении синхроимпульсов обеспечена защита от импульсных помех, ЭК-триггер 13 может изменить свое состояние только такое число раз, сколько импульсов полезной информации имеется во входном биполярном коде. Следовательно, на выходе 17 преобразователя формируется однополярный последовательный код, свободный от помех. Изобретение обеспечивает надежную защиту устройства от импульсных помех как синфазных, так и несинфазных. Преобразователь питается от одного источника питания, что повышает его надежность. Формула изобретения 1. Преобразователь биполярного кода в однополярный, содержащий резистивные делители, соединенные с входными шинами, и выходные шины, отличающийся тем, что, .с целью повышения надежности и расширения функциональных возможностей, введены усилители-ограничители, инверторы, элемент Исключающее ИЛИ и tIK-триггеры, причем выходы резистивных делителей соединены с входами еоответству.ющих усилителей-ограничителей, выход первого из которых подключен к первому входу элемента Исключающее ИЛИ, второй вход которого соединен с выхо;юм другого усилителя-ограничи-, теля, К-входом первого ЗК-триггера и через первый инвертор - с З-входом этого же триггера, выход которого подключен к первой выходной шине, при этом выход элемента Исключающее ИЛИ соединен с tJ-входами второго и третьего ЗК-триггеров. и через второй инвертор - с К-входами этих же триггеров, cifCTHbie входы которых подключены к шине опорных сигналов, кроме того-прямой и инверсный выходы второго 3 К-триггера соединены соответственно с другими tF и К-входами третьего ЗК-триггера, прямой выход которого подключен к другой выходной шине, а инверсный - к счетному входу первого t) К-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь биполярного кода в однополярный | 1981 |

|

SU1058050A1 |

| Преобразователь биполярного кода в однополярный | 1981 |

|

SU1003334A1 |

| ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНОГО КОДА В ОДНОПОЛЯРНЫЙ | 2002 |

|

RU2227367C2 |

| Преобразователь биполярного кода в однополярный | 1984 |

|

SU1228287A1 |

| Преобразователь биполярного кода в однополярный | 1986 |

|

SU1383504A1 |

| Устройство для преобразования последовательного кода в параллельный | 1986 |

|

SU1361725A1 |

| ПРЕОБРАЗОВАТЕЛЬ ОДНОПОЛЯРНЫХ СИГНАЛОВ В РАЗНОПОЛЯРНЫЕ | 2007 |

|

RU2329593C1 |

| Преобразователь биполярного кода в однополярный | 1989 |

|

SU1649668A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

Авторы

Даты

1979-04-25—Публикация

1976-12-30—Подача