И

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2018180C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| Устройство для магнитной записи-воспроизведения речевых сигналов | 1990 |

|

SU1739384A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Компаратор | 1988 |

|

SU1631512A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

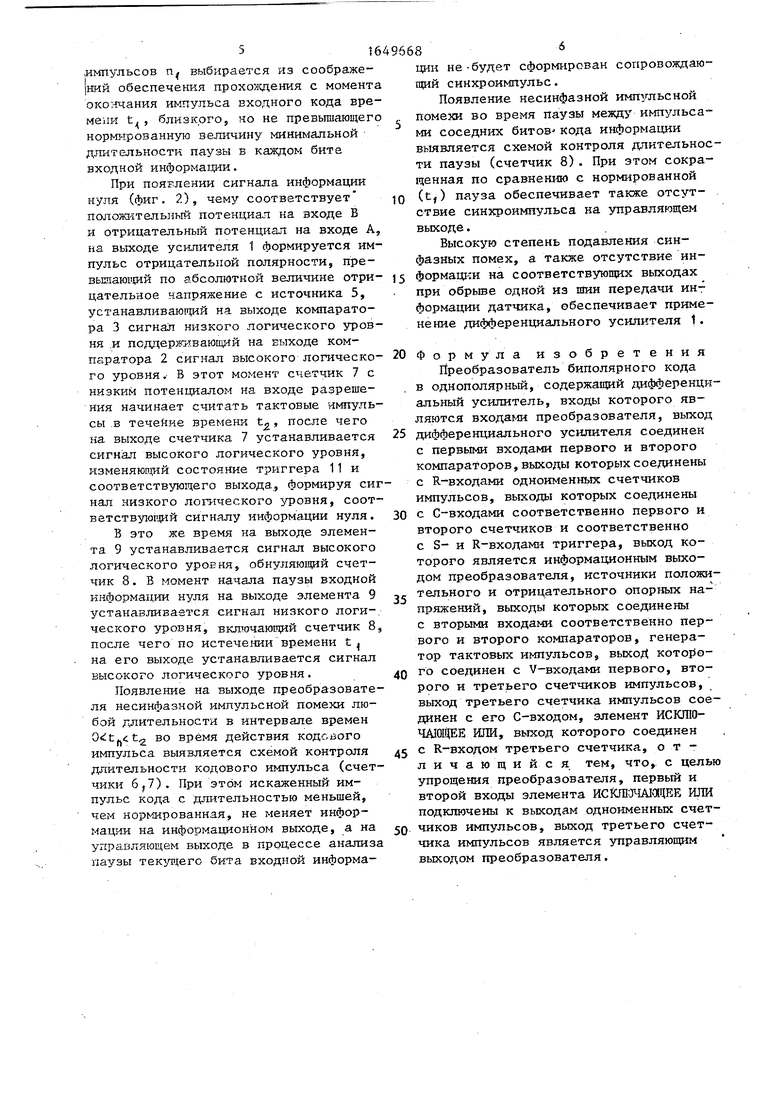

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах приема дискретной информации. Целью изобретения является упрощение преобразователя. Преобразователь содержит дифференциальный усилитель 1, компараторы 2,3, источники 4,5 положительного и отрицательного опорных напряжений, счетчики 6-8 импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, генератор 10 тактовых импульсов и триггер 11. 1 ил.

i

СО

О

о

00

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах приема дискретной информации.

Целью изобретения является упрощение преобразователя,

На чертеже представлена функцио- нальная схема преобразователя.

Преобразователь биполярного кода з однополярный содержит дифференциал ный усилитель 1, компараторы 2,3, источники 4,5 положительного и отрицательного опорных напряженийs счетчяки 6 - 8 импульсов, элемент ИСКЛЮЧАЮ- f5 во тактовых импульсов п75 считаемых ЩЕЕ ИЛИ 9, генератор 10 тактовых импульсов и триггер 11.

Преобразователь работает следующие образом,

В отсутствие входной информация, 20 когда нл входных шинах имеется нулевой потенциал, на выходе усилителя также присутствует нулевой потенциал. При этом сигналы с источников 4,5 обеспечивают формирование на выходах 5 компараторов 2,3 сигналов высокого логического уровня. Эти сигналы высокого уровня поступают на входы начальной установки R счетчиков 6,7, на

счетчиком 69 выбирается из соображен обеспечения прохождения времени с с момента появления информационной еди ницы, близкого, нс не превышающего нормирование величину минимальной длительности действия импухаса вход кода Длительности тактовь

импульсов выбирается л ч соотношения л .. л- А

VT«,

где с - длительность дэис вия импульса входного кода.

По сигналу высокого логического уровня с выхода счетчк а Ъ триггер меняет свое состояние и на информаци онном выходе преобразователя формиру

выходе которых устанавливаются сигна- gg ется сигнал высокого логического уровня, еоотзетствугсыщй сигналу единицы о

И это же время на выходе элемеша } устанавливается сигнал высокого логилы низкого логического уровня, обеспечивающие сохранение на выходе триггера 11 сигнала низкого логического уровня.

Сигналы низкого логического уровня с четкого урсмн,, ос „; ля жчй счетчик 8, с выходов счетчиков 6,7 устанавливают Состояния выходов компарау/щг 3 и также на выходе племента 9 сигнал нис- кого логического уровня,При этом счетчик 8 с низким потенциалом на входе разрешения начинает считать пасту- 40 пающие на него с генератора 10 тактовые -импульсы. По истечении времени Тт, где п - коххячество тактовых импульсов, Тт - период следования

счетчика 7 в процессе водг/ейстьия им- пульса информации едини, т;- „не меняются ,

По окончании дейстьи -уа входах А и В импульссв информации „единицы и начале П4узы до следующего-..-1тд входной информации и выхода ус.-ч гителя присутствует т -левой гстенииал, a i:a выходе компаргчора 2 формируется cnrs.aji

тактовых импульсов, на выходе счетчи- 45 высокого логического уровня, обнуляю- ка 8 устанавливается сигнал высоко- щий счетчик 6. го логического уровня, поддерживающий это состояние через вход разрешения счета..

При появлении сигнала информации единицыtчему соответствует положительный потенциал на входной шине А ч отрицательный потенциал на входной шине В, на выходе усилителя 1 в результате суммирования входных сигналов , формируется импульс положительной полярности s равный амплитуде входных сигналов. Этот импульс, ппевмшающий сигнал положительного кэгшяясекик с ис50

Состояния выходов компаратора 3, триггера 11 и счеттакр 7 не меняются.

При этом на выхопе элемента 9 ус- танавливае ся ci-тьал Ь ЕКОГО логического УГ СЕЧЯ И СЧеТЧИК 3 НЈ.ЧИНЈ -:Т

считан/ jUKTOBLpie ьыпульсы

-

По иетечеьяи времени t,. Tw

выходе счетчика 8 и управляющем выходе преобразовате i (.ЗЬЕЮД синхроимпульсов) устанавоггвяется сигнал высокого логического уровья которь й поддерживается в счетчике 8 через вход разрешения счета. Кс )Г о

точника 4, устанавливает на выходе компаратора 2 сигнал низкого логического уровня и поддерживает на выходе компаратора 3 сигнал высокого логического уровня. В это же время счетчик 6 с низким потешщалок на входе резрешения. начинает считать гтоступаю- |щке на него с генератсра 10 тактовые импульсы. По истечении времени t - ng TT из выходе счетчика б устанавливается сигнал высокого логического уровня,, поддерживающий это состояние через вход разрешения счета, Коли аство тактовых импульсов п75 считаемых

счетчиком 69 выбирается из соображени обеспечения прохождения времени с с момента появления информационной единицы, близкого, нс не превышающего нормирование величину минимальной длительности действия импухаса вход- кода Длительности тактовь.

импульсов выбирается л ч соотношения л .. л- А

VT«,

где с - длительность дэист вия импульса входного кода.

По сигналу высокого логического уровня с выхода счетчк а Ъ триггер . меняет свое состояние и на информационном выходе преобразователя формируня, еоотзетствугсыщй сигналу единицы о

И это же время на выходе элемеша } устанавливается сигнал высокого логивысокого логического уровня, обнуляю- щий счетчик 6.

Состояния выходов компаратора 3, триггера 11 и счеттакр 7 не меняются.

При этом на выхопе элемента 9 ус- танавливае ся ci-тьал Ь ЕКОГО логического УГ СЕЧЯ И СЧеТЧИК 3 НЈ.ЧИНЈ -:Т

считан/ jUKTOBLpie ьыпульсы

-

По иетечеьяи времени t,. Tw

выходе счетчика 8 и управляющем выходе преобразовате i (.ЗЬЕЮД синхроимпульсов) устанавоггвяется сигнал высокого логического уровья которь й поддерживается в счетчике 8 через вход разрешения счета. Кс )Г о

импульсов П{ выбирается из соображений обеспечения прохождения с момента око-мания импульса входного кода времени t, близкого, чо не превышающего нормированную величину минимальной длительности паузы в каждом бите входной информации.

При поярлении сигнала информации нуля (фиг. 2), чему соответствует положительный потенциал на входе В и отрицательный потенциал на входе А, на выходе усилителя 1 Формируется импульс отрицательной полярности, превышающий по абсолютной величине отри- цательное напряжение с источника 5, устанавливающий на выходе компаратора 3 сигнал низкого логического уровня и поддерживающий на ныходе компаратора 2 сигнал высокого логическо- го уровня. В этот момент счетчик 7 с низким потенциалом на входе разрешения начинает считать тактовые импульсы в течейие времени t, , после чего на выходе счетчика 7 устанавливается сигнал высокого логического уровня, изменяющий состояние триггера 11 и соответствующего выхода, формируя сигнал низкого логического уровня, соответствующий сигналу информации нуля.

В это же время на выходе элемента 9 устанавливается сигнал высокого логического уровня, обнуляющий счетчик 8. В момент начала паузы входной информации нуля на выходе элемента 9 устанавливается сигнал низкого логического уровня, включающий счетчик 8S после чего по истечении времени t на его выходе устанавливается сигнал высокого логического уровня.

Появление на выходе преобразователя несинфазной импульсной помехи любой длительности в интервале времен ( во время действия кодового импульса выявляется схемой контроля длительности кодового импульса (счетчики ). При этом искаженный импульс кода с длительностью меньшей, чем нормированная, не меняет информации на информационном выходе, а на управляющем выходе в процессе анализа паузы текущего бита входной информа

Q 5 0 5 0

О

5 0

5

ции не -будет сформирован сопровождающий синхроимпульс.

Появление несинфазной импульсной помехи во время паузы между импульсами соседних битов- кода информации выявляется схемой контроля длительности паузы (счетчик 8). При этом сокращенная по сравнению с нормированной (tf) пауза обеспечивает также отсутствие синхроимпульса на управляющем выходе.

Высокую степень подавления синфазных помех, а также отсутствие информации на соответствующих выходах при обрыве одной из шин передачи информации датчика, обеспечивает применение дифференциального усилителя 1.

Формула изобретения

Преобразователь биполярного кода в однополярный, содержащий дифференциальный усилитель, входы которого являются входами преобразователя, выход дифференциального усилителя соединен с первыми входами первого и второго компараторов, выходы которых соединены с R-входами одноименных счетчиков импульсов, выходы которых соединены с С-входами соответственно первого и второго счетчиков и соответственно с S- и R-входами триггера, выход которого является информационным выходом преобразователя, источники положительного и отрицательного опорных напряжений, выходы которых соединены с вторыми входами соответственно первого и второго компараторов, генератор тактовых импульсов, выход котор о- го соединен с V-входами первого, второго и третьего счетчиков импульсов, выход третьего счетчика импульсов соединен с его С-входом, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с R-входом третьего счетчика, отличающийся тем, что, с целью упрощения преобразователя, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам одноименных счетчиков импульсов, выход третьего счетчика импульсов является управляющим выходом преобразователя.

| Преобразователь биполярного кода в однополярный | 1988 |

|

SU1552378A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1989-03-20—Подача