1

Изобретение относится к передаче данных может использоваться в различных радиотехнических устройствах.

Известно устройство синхронизации, содержащее последовательно соединенные блок управления, делитель частоты, блок выделения зоны и первый усилитель, а также второй усреднитель, триггер, два ключа, фазовый дискриминатор и формирователь фронтов, выход которого подключен к другому входу блока выделения зоны .

Однако в известном устройстве при кратковременных пропаданиях сигнала могут появиться ошибки синхронизации типа «вставки и «выпадения за счет безпорядочного переключения шага коррекции под действием шумов, что снижает помехоустойчивость устройства.

Цель изобретения - повышение помехоустойчивости.

Для этого в устройство синхронизации, содержащее последовательно соединенные блок управления, делитель частоты, блок выделения зоны и первый усреднитель, а также второй усреднитель, триггер, два ключа фазовый дискриминатор и формирователь фронтов, выход которого подключен к другому входу блока выделения зоны, введены последовательно соединенные блок когерентной свертки, анализатор, элемент ИЛИ,

блок включения коррекции и последовательно соединенные переключатель режимов работы и фазовый демодулятор, выходы которого соответственно подключены к входу формирователя фронтов и к другому входу анализатора, другой выход которого подключен к другому входу элемента ИЛИ, причем выход формирователя фронтов подключен к входу фазового дискриминатора, выходы которого, подключены через второй усреднитель к второму и третьему входам блока включения коррекции, а через первый и второй ключ - к чхгтвертому и пятому входам блока включения коррекции, выходы которого подключены к входам блока управления, при этом выход делителя частоты подключен к другому входу фазового дискриминатора, выходы первого усреднителя через триггер подключены соответственно к другим входам первого и второго ключей, причем другой выход блока когерентной свертки

.подкл очен к выходу переключателя режимов работы.

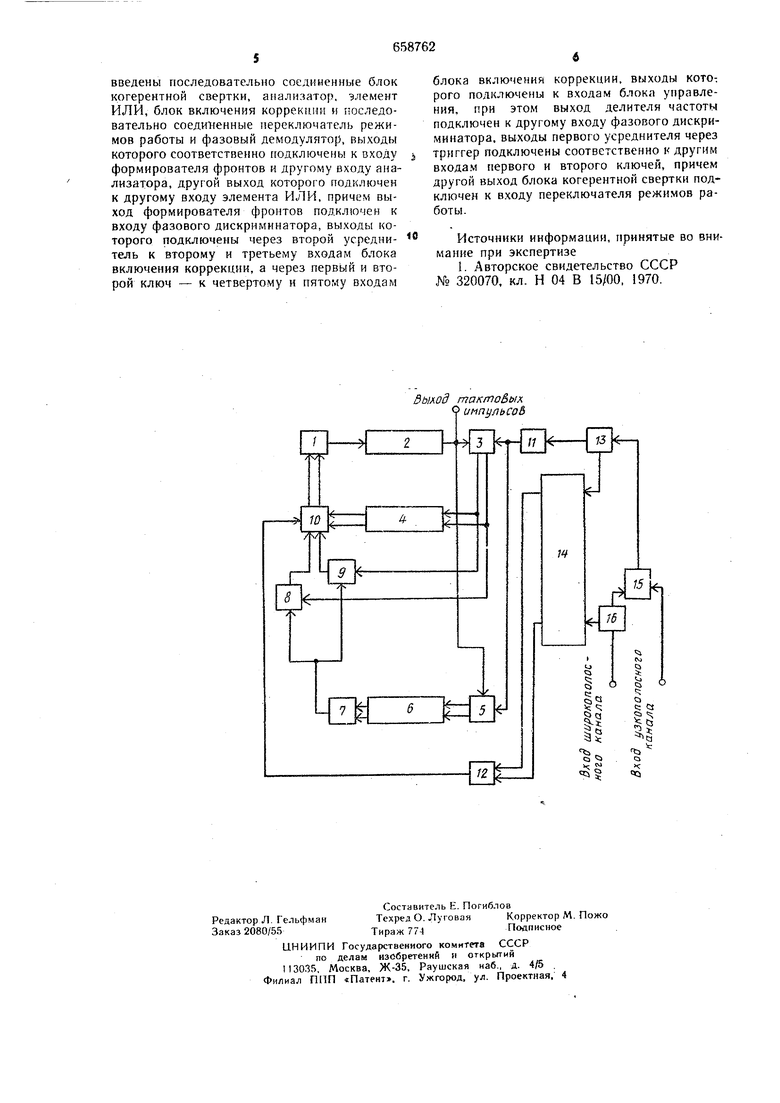

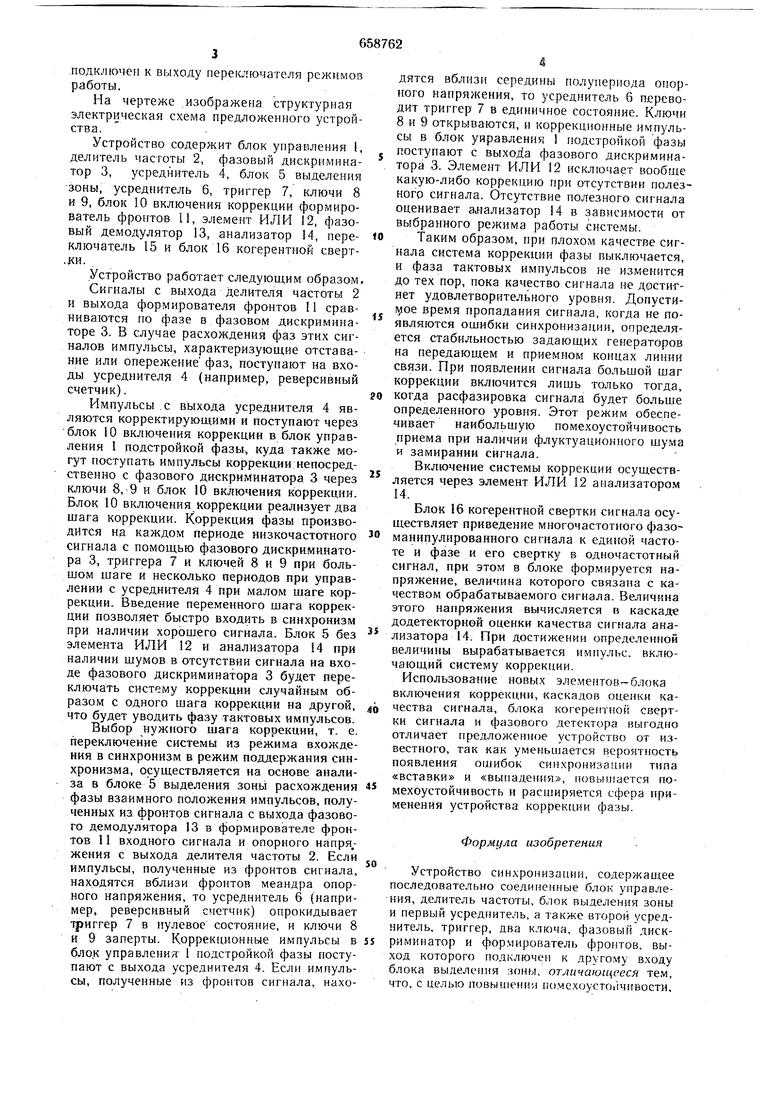

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит блок управления , делитель частоты 2, фазовый дискриминатор 3, усреднитель 4, блок 5 выделения зоны, усреднитель 6, триггер 7, ключи 8 и 9, блок 10 включения коррекции формирователь фронтов 11, элемент ИЛИ 12, фазовый демодулятор 13, анализатор 14, переключатель 15 и блок 16 когерентной сверт,ки.

Устройство работает следующим образом. Сигналы с выхода делителя частоты 2 и выхода формирователя фронтов П сравниваются но фазе в фазовом дискриминаторе 3. В случае расхождения фаз этих сигналов импульсы, характеризующие отставание или опережение фаз, поступают на входы усреднителя 4 (например, реверсивный счетчик).

Импульсы .с выхода усреднителя 4 являются корректирующими и поступают через блок 10 включения коррекции в блок управления 1 подстройкой фазы, куда также могут поступать импульсы коррекции непосредственно с фазового дискриминатора 3 через ключи 8, 9 и блок 10 включения коррекции. Блок 10 включения коррекции реализует два шага коррекции. Коррекция фазы производится на каждом периоде низкочастотного сигнала с помощью фазового дискриминатора 3, триггера 7 и ключей 8 и 9 при большом шаге и несколько периодов при управлении с усреднителя 4 при малом шаге коррекции. Введение переменного шага коррекции позволяет быстро входить в синхронизм при наличии хорошего сигнала. Блок 5 без элемента ИЛИ 12 и анализатора 14 при наличии шумов в отсутствии сигнала на входе фазового дискриминатора 3 будет переключать систему коррекции случайным образом с одного шага коррекции на другой, что будет уводить фазу тактовых импульсов. Выбор нужного шага коррекции, т. е. переключение системы из режима вхождения в синхронизм в режим поддержания синхронизма, осуществляется на основе анализа в блоке 5 выделения зонь расхождения фазы взаимного положения импульсов, полученных из фронтов сигнала с выхода фазового демодулятора 13 в формирователе фронтов 11 входного сигнала и опорного напря,жения с выхода делителя частоты 2. Если импульсы, полученные из фронтов сигнала, находятся вблизи фронтов меандра опорного напряжения, то усреднитель 6 (например, реверсивный счетчик) опрокидывает триггер 7 в нулевое состояние, и ключи 8 и 9 заперты. Коррекционные импульсы в блок управления- 1 подстройкой фазы поступают с выхода усреднителя 4. Если нмнульсы, полученные из фронтов сигнала, находятся вблизи середины полупериода опорного напряжения, то усреднитель 6 аереводит триггер 7 в единичное состояние. Ключи 8 и 9 открываются, и коррекционные импульсы в блок уйравления подстройкой фазы поступают с выхода фазового дискриминатора 3. Элемент ИЛИ 12 исключает вообще какую-либо коррекцию при отсутствии полезного сигнала. Отсутствие полезного сигнала оценивает а,нализатор 14 в зависимости от выбранного режима работы системы.

Таким образом, при плохом качестве сигнала система коррекции фазы выключается, и фаза тактовых импульсов не изменится до тех пор, пока качество сигнала не достигнет удовлетворительного уровня. Допустиivjoe время пропадания сигнала, когда не появляются ошибки синхронизации, определяется стабильностью задающих генераторов на передающем и приемном концах линия связи. При появлении сигна аа большой шаг коррекции включится лишь только тогда, когда расфазировка сигнала будет больше определенного уровня. Этот режим обеспечивает наибольшую помехоустойчивость приема при наличии флуктуационного шума и замирании сигнала.

Включение системы коррекции осуществляется через элемент ИЛИ 12 анализатором 14.

Блок 16 когерентной свертки сигнала осуществляет приведение многочастотиого фазоманипулироваиного сигнала к единой частоте и фазе и его свертку в одночастотный сигнал, при этом в блоке формируется напряжение, величина которого связана с качеством обрабатываемого сигнала. Величина этого напряжения вычисляется в каскаде додетекторной оценки качества сигнала анализатора 14. При достижении определенной величины вырабатывается импульс, включающий систему коррекции.

Использование новых элементов-блока включения коррекции, каскадов оценки качества сигнала, блока когерентной свертки сигнала и фазового детектора выгодно отличает предложенное устройство от известного, так как уменьшается вероятность появления ошибок синхронизации типа «вставки и «выпадения, повышается помехоустойчивость и расширяется сфера применения устройства коррек 1ии фазы.

Формула изобретения

Устройство синхронизации, содержап ее последовательно соединенные блок управления, делитель частоты, блок выделения зоны и первый усред1штель, а также второй усреднитель, триггер, два ключа, фазовый дискриминатор и фор.мирователь фронтов, выход которого подключен к другому входу блока выделения зоны, отличающееся тем, что, с целью повышении помехоустойчивости.

введены последовательно соединенные блок когерентной свертки, анализатор, элемент ИЛИ, блок включения коррекции и последовательно соединенные переключатель режимов работы и фазовый демодулятор, выходы которого соответственно подключены к входу формирователя фронтов и другому входу анализатора, другой выход которого подключен к другому входу элемента ИЛИ, причем выход формирователя фронтов подключен к входу фазового дискриминатора, выходы которого подключены через второй усреднитель к второму и третьему входам блока включения коррекции, а через первый и второй ключ - к четвертому и пятому входам

блока включения коррекции, выходы кото-: рого подключены к входам блока управления, при этом выход делителя частоты подключен к другому входу фазового дискриминатора, выходы первого усреднителя через триггер подключены соответственно к другим входам первого и второго ключей, причем другой выход блока когерентной свертки подключен к входу переключателя режимов работы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 320070, кл. Н 04 В 15/00, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой демодулятор сигналов с относительной фазовой модуляцией | 1981 |

|

SU985970A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Двухступенчатый регенератор | 1978 |

|

SU726668A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ | 1973 |

|

SU375772A1 |

| Устройство синхронизации | 1981 |

|

SU1125759A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU882012A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

дьмд тактоВы

Авторы

Даты

1979-04-25—Публикация

1977-05-06—Подача