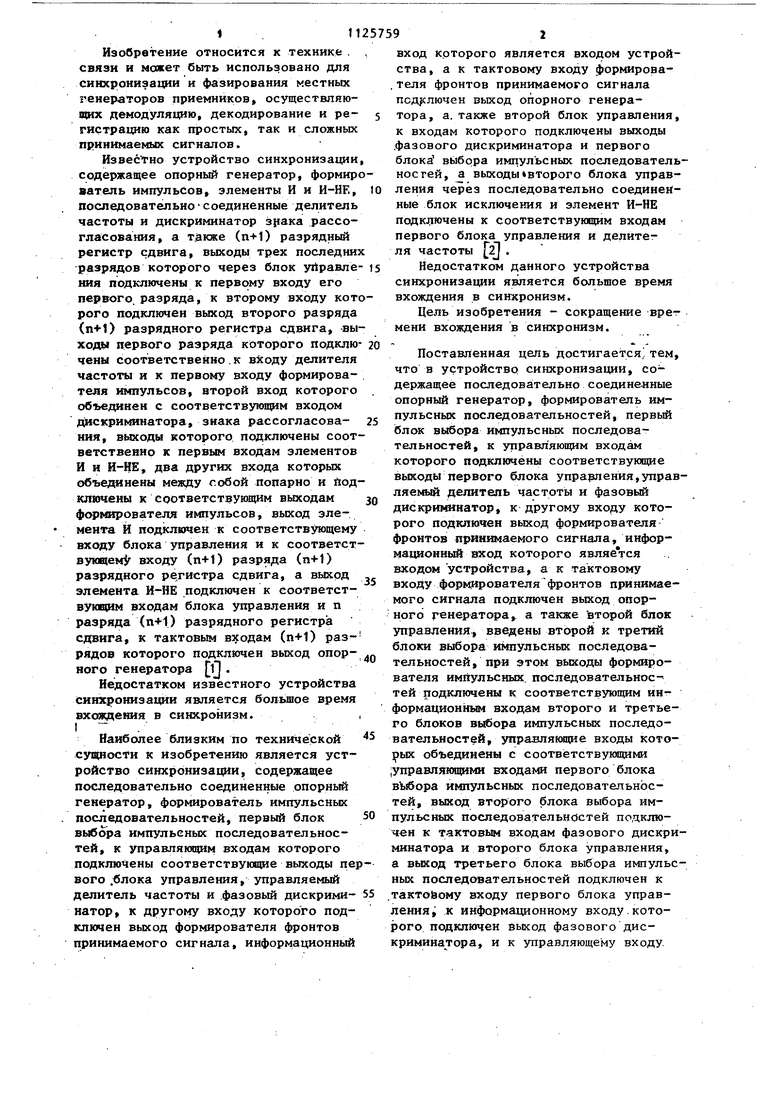

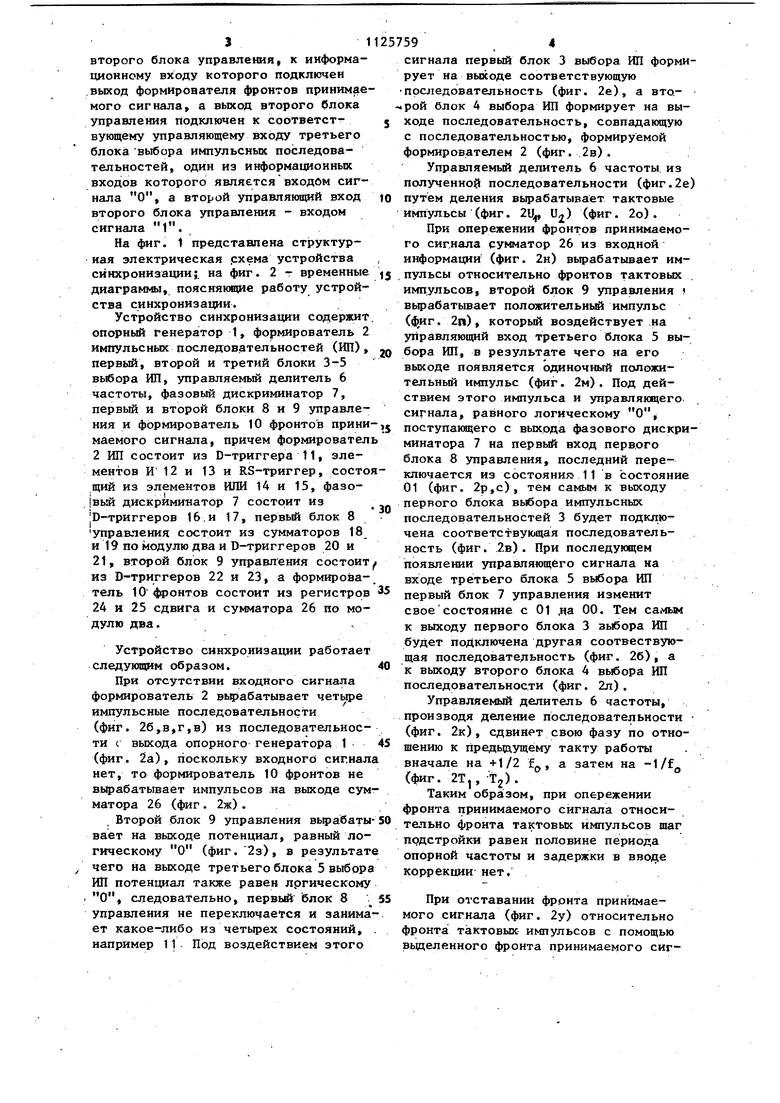

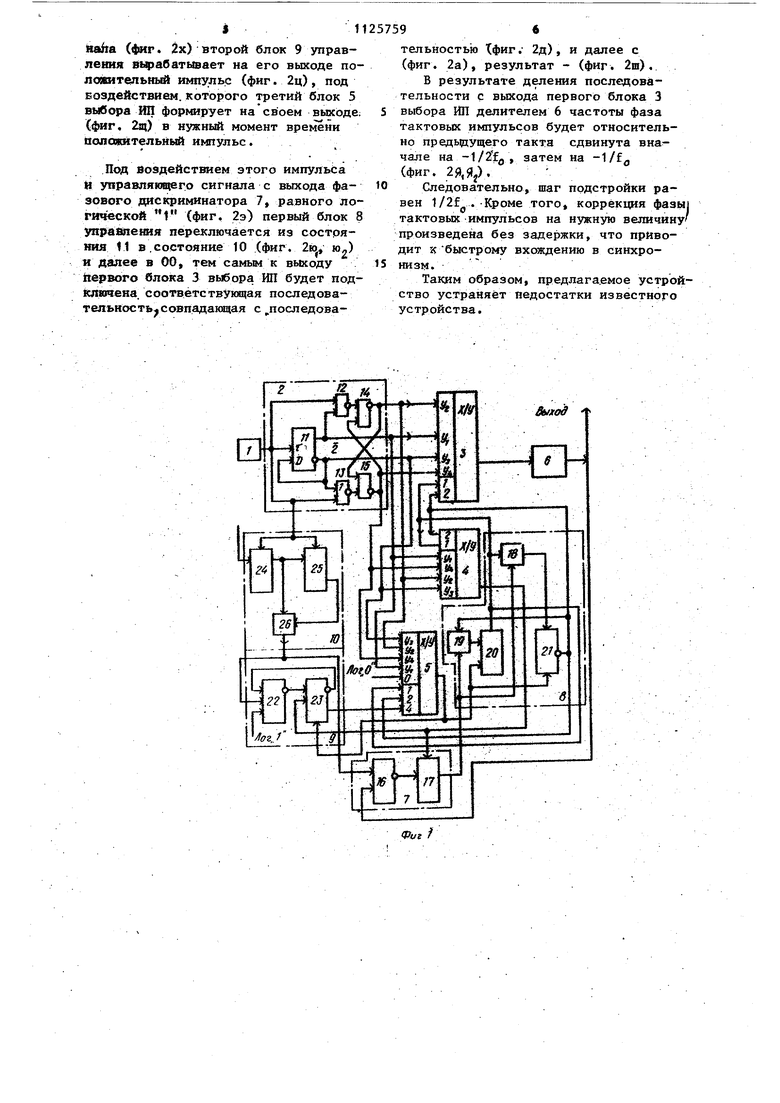

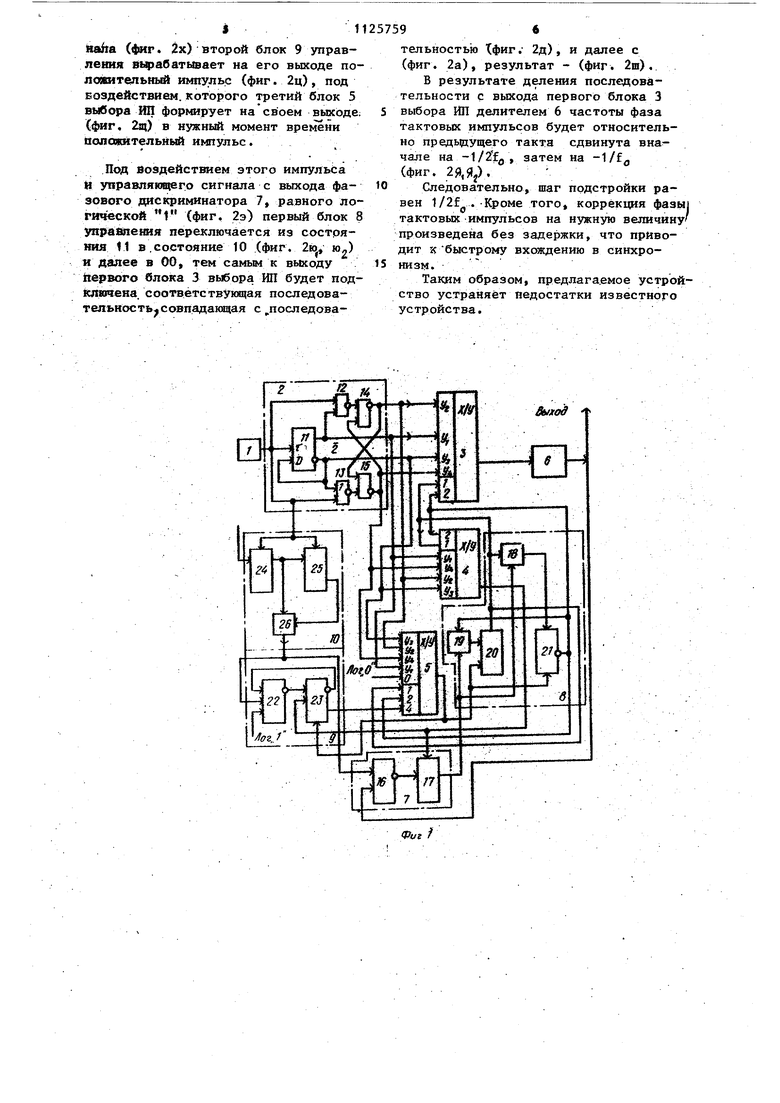

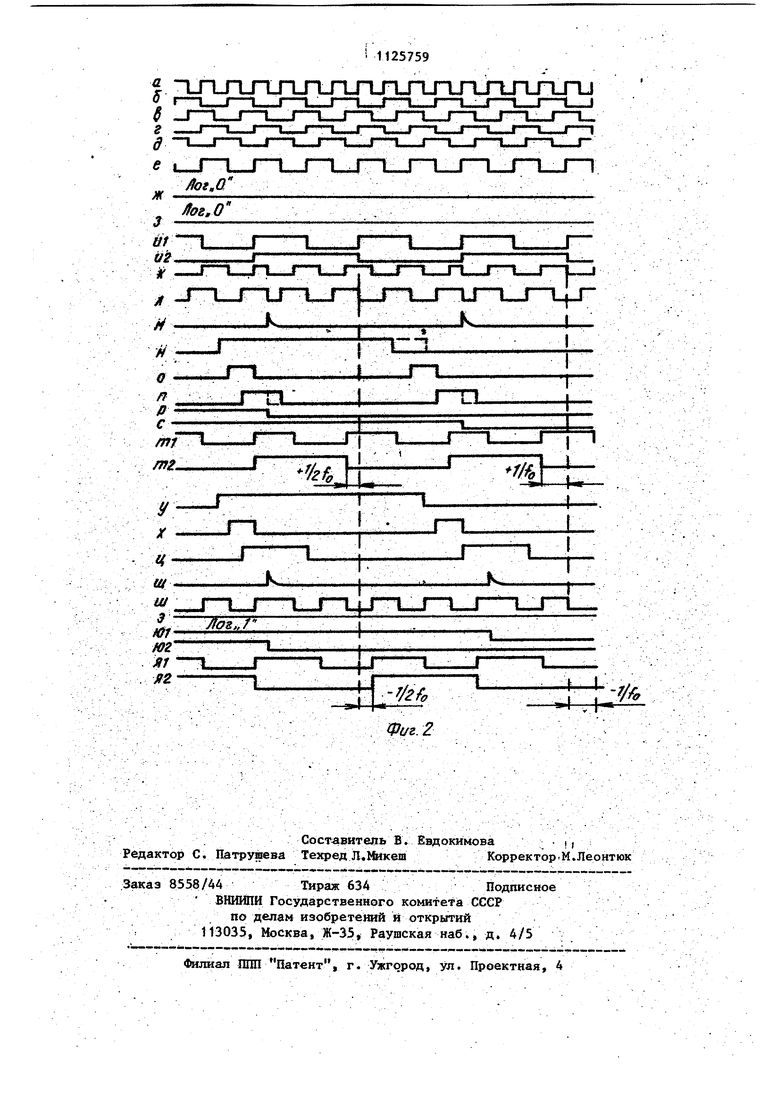

. 11 Изобретение относится к технике . связи и может быть использовано для синхронизации и фазирования местных генераторов приемников, осуществляющих демодуляцию, декодирование и регистрацию как простых, так и сложных принимаемых сигналов. Известно устройство синхронизации содержащее опорный генератор, формиро ватель импульсов, элементы И и И-НЕ, последовательносоединенные делитель частоты и дискриминатор зрака рассогласования, а тзкже (п+1) разрядный регистр сдвига, выходы трех последних разрядов которого через блок уйравлеиия подключены к первому входу его первого разряда, к второму входу кото рого подключен выход второго разряда (п+О разрядного регистра сдвига, -выходы первого разряда которого подключены соответственно.к входу делителя частоты и к первому входу формирователя импульсов, второй вход которого объеданен с соответствующим входом даcкpи вIнaтopa, знака рассогласоваНИН, выходы которого подключены соответственно к первым входам элементов И и И-НЕ, два других входа которых объединены между собой попарно и йодключены к соответствующим выходам формирователя импульсов, выход элемента И подключен к соответствующему входу блока управления и к соответствующем г входу (п+1) разряда (п+1) разрядного регистра сдвига, а выход элемента И-НЕ подключен к соответствующим входам блока управления и п разряда (п+1) разрядного регистра сдвига, к тактовьм входам (n-fl) разрядов которого подключен выход опорного генератора l Недостатком известного устройства синхронизации является большое время вхождения в синхронизм. Наиболее близким по технической сущности к изобретению является устройство синхронизации, содержащее последовательно соединенные опорный генератор, формирователь импульсных последовательностей, первый блок выбора импульсных последовательностей, к управляющим входам которого подключены соответствующие выходы пер вого .5лока управления, управляемый делитель частоты и .фазовый дискриминатор, к другому входу которого подклкмен выход формирователя фронтов принимаемого сигнала, информационный 9 вход которого является входом устройства, а к тактовому входу формирователя фронтов принимаемого сигнала псд;слючен выход опорного генератора, а. также второй блок управления, к входам которого подключены выходы .фазового дискриминатора и первого блока выбора импульсных последовательностей, а выходы второго блока управления через последовательно соединекные блок исключения и элемент И-НЕ подключены к соответствующим входам первого блока управления и делителя частоты 2 . Недостатком данного устройства синхронизации является большое время вхождения в синхронизм. Цель изобретения - сокращение -врет мени вхождения в синхронизм. Поставленная цель достигается) тем, что в устройство синхронизации, содержащее последовательно соединенные опорный генератор, формирователь импульсных последовательностей, первый блок выбора импульсных последовательностей, к управляющим входам которого подключены соответствующие выходы первого блока упраэления,управляемьяй делитель частоты и фазовый дискрш шнатор, к другому входу которого подключен выход формирователя фронтов принимаемого сигнала, информационнь } вход которого являеЧ-ся входом устройства, а к тактовому входу формирователяфронтов принимаемого сигнала подключен выход опорного генератора, а также второй блок управления, введены второй и третий блоки выбора импульсных последовательностей, при этом выходы формирователя импульсных, последовательное-тей подключены к соответствующим информационные входам второго и третьего блоков импульсных последовательностей, управляю1ще входы которых объединены с соответствующими ;управляющими вxoдa e первого блока Bbt6opa импульсных последовательностей, выход второго блока выбора импульсных последовательностей подключен к тактовым входам фазового дискриминатора и второго блока управления, а вьссод третьего блока выбора импульсных последовательностей подключен к тактойому входу первого блока управления к информационному входу.которого, подключен выход фазового дискриминатора, и к управляющему входу. ционному входу которого подключен .выход формирователя фронтов принимаемого сигнала, а выход второго блока управления подключен к соответствующему управляющему входу третьего блока выбора импульсных последовательностей, один из информационных входов которого является входом сигнала О, а второй управляющий вход второго блока управления - входом сигнала 1. На фиг. 1 представлена структурная электрическая .схема устройства синхронизации;, на фиг. 2 - временные диаграммы, поясняюнше работу устройства синхронизации. Устройство синхронизации содержит опорный генератор 1, формирователь 2 импульсных последовательностей (ИП), первый, второй и третий блоки 3-5 выбора ИП, управляемый делитель 6 частоты, фазовый дискриминатор 7, первый и второй блоки 8 и 9 управлеНИН и формирователь 10 фронтов прини маемого сигнала, причем формировател 2 Ш1 состоит из D-триггера 11, элементов И 12 и 13 и RS-триггер, состо щий из элементов ИЛИ 14 и 15, фазо вый дискриминатор 7 сострит из |В-триггеров 16.и 17, первый блок 8 управления состоит из сумматоров 18 и 19 по модулю два и D-триггеров 20 и 21, второй блок 9 управления состоит из В триггеров 22 и 23, а формирователь 10 фронтов состоит из регистров 24 и 25 сдвига и сумматора 26 по модулю два. Устройство синхронизации работает следующим образом. При отсутствии входного сигнала формирователь 2 вьфабатывает четыре импульсные последовательности (фиг. 26,в,г,в) из последовательности с выхода опорного- генератора 1 (фиг. 2а), поскольку входного сигнал нет, то формирователь 10 фронтов не вырабатывает импульсов .на выходе сум матора 26 (фиг. 2ж) . Второй блок 9 управления вьфабаты вает на выходе потенциал, равный логическому О (фиг. 2з), в результат чего на выходе третьего блока 5 выбора ИП потенциал также равен лргическому О, следовательно, первь блок 8 управления не переключается и занима ет какое-либо из четырех состояний, например 11 Под воздействием этого рует на выходе соответствующую последовательность (фиг. 2е), а второй блок 4 выбора ИП формирует на выходе последовательность, совпадающую с последовательностью, формируемой формирователем 2 (фиг. 2в). Управляемый делитель 6 частоты, из полученной последовательности (фиг.2е) путем деления вырабатывает тактовые импульсы (фиг. и) (фиг. 2о) . При опережении фронтов принимаемого сигнала сумматор 26 из входной информации (фиг. 2н) вырабатывает импульсы относительно фронтов тактовых . импульсов, второй блок 9 управления ) вырабатывает положительнь импульс (. 2п), который воздействует на управляющий вход третьего блока 5 выбора ИП, в результате чего на его выходе появляется одиночный положительный импульс (фиг. 2м). Под действием этого импульса и управляющего, сигнала, равного логическому О, поступакицего с выхода фазового дискриминатора 7 на первый вход перв.ого блока 8 управления, последний переключается из состояния 11 в состояние 01 (фиг. 2р,с), тем самым к выходу первого блока выбора импульсных последовательностей 3 будет подключена соответствующая последовательность (фиг. .2в). При последующем появлении управляющего сигнала на входе третьего блока 5 выбора Ш1 первый блок 7 управления изменит своесостояние с 01 ,на 00. Тем самьм к выходу первого блока 3 выбора Ш1 будет подключена другая соотвествующая последовательность (фиг, 2б), а к выходу второго блока 4 выбора ИП последовательности (фиг. 2л). Управляемый делитель 6 частоты, производя деление последовательности (фиг. 2к), сдвинет свою фазу по отношению к предьщущему такту работы вначале на +1/2 f , а затем на -l/f (фиг. 2Т,, Tj). Таким , при опережении фронта принимаемого сигнала относительно фронта тактовых импульсов шаг подстройки равен половине периода опорной частоты и задержки в вводе коррекции нет. При отставании фронта принимаемого сигнала (фиг. 2у) относительно фронта тактовых импульсов с помощью вьщеленного фронта принимаемого сиг .1

Haha (фиг. 2x) второй блок 9 управления В1фабатывает на его выходе положительный импульс (фиг. 2ц), под воздействием.которого третий блок 5 выбора ИП формирует насвоем выходе. (фиг. bi) в нужный момент времени полодкйтельНый импульс.

Под воздействием этого импульса В управляющего сигнала с выхода фазового дискриминатора 7, равного логической 1 (фиг, 2э) первый блок 8 упраепения переключается из состояния 11 в.состояние 10 (фиг. 2ю ю,) и далее в 00, тем самым к выходу первого блока 3 выбора ИП будет подключена, с оответствуннцая последовательность, совпадакяцая с ,последова25759«

тельностью Тфиг. 2д), и далее с (фиг. 2а), результат - (фиг. 2ш).

В результате деления последовательности с выхода первого блока 3 5 выбора ЙП делителем 6 частоты фаза тактовых импульсов будет относительно предьдущего такта сдвинута вна чале на -l/2fo, затем на -1/f (Фиг. 2й,Яр.

Следовательно, шаг подстройки равен 1/2f..Кроме того коррекция фазы| тактовых импульсов на нужную величину/ произведена без задержки, что приводит Xбыстрому вхождению в синхро15 низм.

Таким образом, предлагаемое устройство устраняет недостатки известного устройства.

TJTJTJTXlJTJTJTJTJ-l

of,e

ж Лог.О

1125759 -7/2 fa

Фш.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1981 |

|

SU1159173A1 |

| Способ синхронизации и устройстводля ЕгО ОСущЕСТВлЕНия | 1979 |

|

SU803113A1 |

| Устройство синхронизации импульсных приемников | 1976 |

|

SU605327A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство для синхронизации двоичных сигналов в каналах с постоянными преобладаниями | 1981 |

|

SU1125760A2 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

УСТРОЙСТВО СИНХРОйИЗ/ЩИИ, содержащее последовательно соедине.нные опорньй генератор, формирователь импульсных последовательйостей, первый блок выбора импульсных поспедо-V вательностей, к управлякдрм входам которого подключены соответствующие вьБсоды первого, блока управления, управляемый делитель частоты и фазо вый дискриминатор, к другому входу , которого подключен РЫХОД формирователя фронтов принимаемого сигнала, : ииформационнь1й вход которого, явяяется входом устройства, а к тактовому входу формирователя фронтов прииш;1аемого сигнала подключен выход оЯор Врго генератора, а также второй блок управления, о т л а ю щ е вС я тем.что, с целью сокращения врёиекй вхоясдения в синхронизм, введены вто рой и третий блоки вьбора ИмпульснызЕ последовательностей, при этом выходы формирователя импульсных последовательностей подключены к соответствующим информационным входам второго и третьего блоков выбора импульсных последовательностей, управляющее входы которых объединены с соответствукщими управлягацими входами первого блока выбора импульсных последовательностей, выход второго блока импульсных последовательностей подключен к тактовым входам, фазового дискриминатора и второго блока упрайления, а выход третьего блока вьйора импульсньк последовательнострй подключен к тактовому входу пер- I вого блока управления к инфор1ма194онному входу которого подключен выход фазового дискрЙ1 0{натора|И к первому управляющему вхедчу второго блока управления, к информационному, входу которого подключен выход формирователя фронтов принимаемого сигнала, а выход второго блока управления под- ключей к соответствующему управляющему входу третьего блока выбора импульсных последовательностей, один, 01 из ицформащюнных входов которого является входом сигнала О, а второй управляшций вход второго блока управления - входом сигнала 1.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство синхронизации | 1977 |

|

SU694982A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ синхронизации и устройстводля ЕгО ОСущЕСТВлЕНия | 1979 |

|

SU803113A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-23—Публикация

1981-03-05—Подача