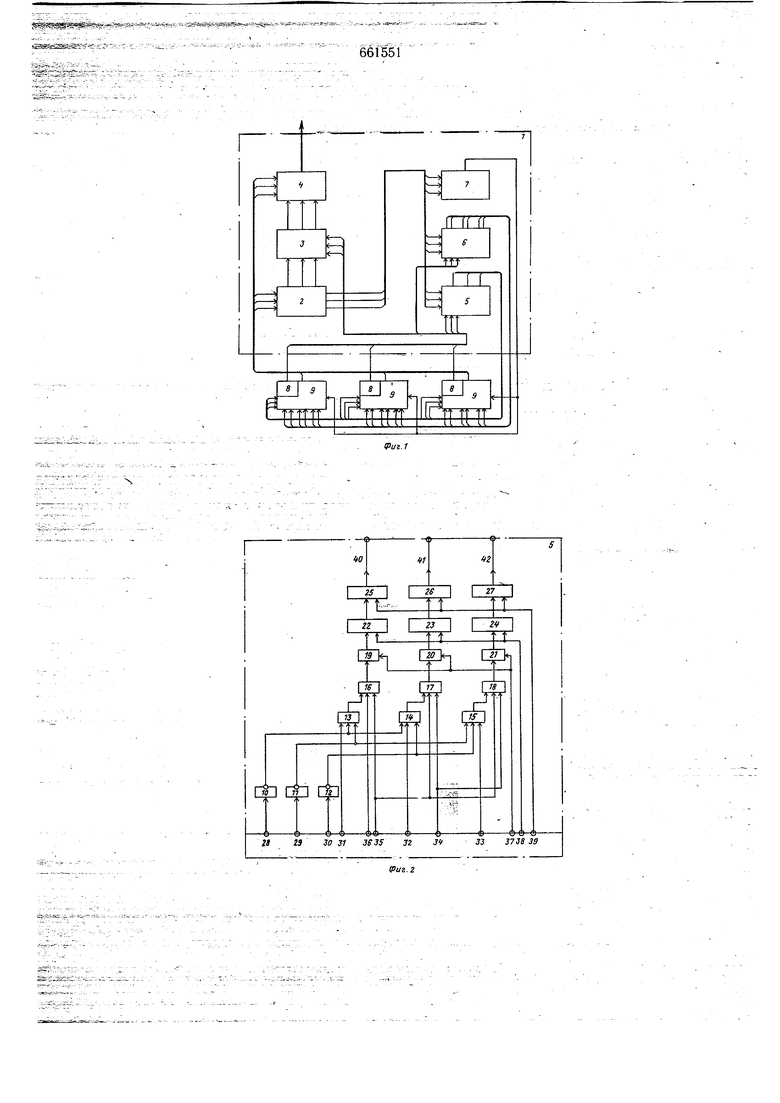

i- ципиальная схема блока фиксации состояния каналов; на фиг. 3 приведены принципиаль ные схемы анализаторов систем контроля .-:.: и мажоритарного блока сравнения. На фиг. 1 приняты следующие обозна:чения: устройство 1 для переключения каналов вычислительной системы, мажоритарный блок 2 сравнения, блок 3 анализа, ком-- мутатор 4 каналов, блок 5 фиксации состоя-.с-.ния каналов, анализатор 6 состояния сиетем контроля, анализатор 7 состояния мажоритарного блока, системы контроля, анализатор 7 состояния мажоритарного блока, системы 8 контроля каналов, каналы 9 вычислите/тьной системы. Устройство 1 для переключения каналов включает мажоритарный блок 2 сравнения, блок,3 анализа, коммутатор 4 каналов, блок 5 фиксации состояния каналов и анализаторы 6 и 7 состояния систем контроля и мажбрйтарного блока 2. Мажоритарный блок 2 сравнения осуществляет сравнение результатов, поступающих из отдельных каналов 9 и вырабатывает три сигнала сравнения. Блок 3 анализа по сигналам с выхода блока 2 и систем 6 контроля вырабатывает сигналы для управления коммутатором 4 каналов. Коммутатор 4 каналов подключает выходы одного из каналов 9 к выходам вычислительной системы по сигналам с блока 3 анализа. Блок 5 фи1 сации состояния каналов производитфиксацию не.;.:Исправного канала, подсчет количества с боев (отказов) каждого канала за установленный промежуток времени и выдачу информации в неисправный канал для его самодиагностики. В анализаторе 6 состояния систем контроля устанавливается факт ошибки в работе систем 8 контроля каналов, а также устанавливается хакрактер ошибки (необнаружение сборя в канале или ложное срабатывание (систем контроля). В анализаторе 7 состояния мажоритарного блока обнаруживается ошибка в работе схем сравнения мажоритарного блока 2. Функциональная схема блока 5 фиксации состояния каналов на фиг. 2 содержит: логические элементы 10-21 блока, счетчики 22-24, вентили 25-27, выходы 28-30 систем контроля каналов, инверсные выходы 31-33 мажоритарного блока сравнения 2, прямые выходы 34-36 мажоритарного блока сравнения 2, вход 37 первого синхронизируюшего сигнала (занесения информации о состоянии канала на входы счетчиков 22-24), вход 38 второго синхронизирующего сигнала (установки в исходное состояние счетчиков 2224), вход 39 третьего синхронизирующего сигнала, выходы 40-42 блока состояния каналов. Элементы 10-21 входят в анализатор состояния каналов; элементы 22-27 объединяются в схему счетчиков числа сбоев ка- налов. Функциональные схемы анализаторов систем 6 контроля и мажоритарного блока 7 на фиг. 3 содержат: - логические элементы 43-58, выходы 59-64 анализатора 6 состояния систем контроля, выход 65 анализатора 7 состояния мажоритарного блока. Элементы 43-54 входят в анализатор 6 состояния систем контроля, § элементы 5558 - в анализатор 7 состояний мажоритарного блока. Устройство для переключения каналов вычислительной системы работает следую-- . Ш.ИМ образом. При исправной работе всех каналов 9 коммутатор 4 выдает на выход вычислительной системы результат, полученный в первом канале. Одновременно прямые и инверсные сигналы с выхода мажоритарного блока 2 сравнения по шинам 31-36 поступают в блок 5 фиксации состояния каналов на элементы ИЛИ 13-15 и элементы И 16-17. На выходах элементов И 16-17 отсутствуют сигналы неисправности каналов. По сигналу от таймера, поступающему с выхода 37 на элементы И 19-21, производится опрос состояния каналов. При этом на выходы счетчиков 22-24, предварительно установленных в исходное состояние сигналом по входу 38, сигналы не поступают и счетчики и остаются в исходном состоянии, соответствующем отсутствию сбоев (отказов в каналах 9. При подаче сигнала на вход 39 через вентили 25-27 информация об отсутствии сбрев в каналах поступает по шинам 40-42 и на дополнительные входы каналов. . В случае сбоя (отказа) одного или нескольких каналов 9 коммутатор 4 по сигналам с выхода мажоритарного блока 2 сравнения и блока 3 анализа .подключает к выходу . первый по порядку исправный канал. Одновременно сигналы с выходов 31-36 мажоритарного блока 2 сравнения и выходов 28-30 схем 8 контроля каналов, инвертируемые с помощью элементов НЕ 10-12, поступают в блок 5 фиксации состояния, каналов. На выходах элементов И 16-18 формируются сигналы неисправностей соответствующих каналов. По сигналу с входа 37 производится фиксация состояния каналов в счетчиках путем занесения « 1 в счетчик, соответствующий неисправному каналу. По сигналу с входа 39 открываются вентили 25-27 и содержимое С11етчиков 22-24 передается в каналы 9 для проведения их диагностики и восстановления. Одновременно с работой бло ка 5 сигналы с выходов мажоритарного блока 2 сравнения по шинам 31-36 поступают в анализаторы состояния систем 6 контроля и мажоритарного блока 7. При этом в

момент поступления синхронизирующего сигнала на вход 39 на выходных шинах 59-65 анализаторов 6 и 7 сигналы отсутствуют.

В случае сбоя (отказа) одного или нескольких каналов 9 сигналы с выходов 31-36 мажоритарного блока 2 сравнения и выходов 28-30 схем 8 контроля каналов поступают на элементы анализатора 6 состояния систем контроля иэлементы анализатора 7 состояния мажоритарного блока. На выходах этих схем в момент поступления сйнхронизирующего сигнала на шине 39 формируются сигналы состояния систем 8 контроля каналов и мажоритарного блока 2 сравнения.

На выходах 59, 61, 63 формируются сигналы необнаружения сбоев (отказов) системами 8 контроля каналов. На выходах 60, 62,. 64 формируются сигналы ложного срабатывания систем 8 контроля каналов. На выходе 65 формируется сигнал неправильной работы мажоритарного блока 2 сравнения.

Логика формирования сигналов на выходах 59-65 ясна из схемы, приведенной на фиг. 3. Например, сигнал необнаружения сбоя (отказа) в первом канале формируется на выходе 59 при наличии сигнала совпадения результатов во втором и третьем каналах вычислительной системы (сигнал на шине 31), отсутствии совпадения результатов в первом и втором каналах вычислительной системы (сигнал на шине 33 отсутствует) и отсутствии сигнала с выхода Системы контроля первого канала (сигнала на шине 30). Сигнал ложного срабатывания системы контроля, первого канала формируется на шине 60 при наличии сигнала совпадения результатов в перйом и втором каналах вычислительной системы (сигнала на шине 33) или сигнала совпадения результатов в первом и третьем каналах (сигнала на шине 32) и наличии сигнала с выхода системы контроля первого канала (сигналы на шине 30). По такой желогике вырабатываются сигналы необнаружения-сбоев (отказов) и ложного срабатывания систем контроля второго и третьего каналов на выходах 61, 63 и 62, 64 соответственно.

Сигнал неправильной работы схем сравнения на выходе 65 формируется приналичии любых только.двух из трех возможных сигналов совпадения результатов в каналах вычислительной системы (сигналов на шинах 31-33).

Сигналы с выходов 59-65 поступают на дополнительные входы каналов вычислительной системы одновременно с сигналами из

блока 5. Эта информация позваляет судить о состояний систем контроля каналов 6 и схем сравнения мажоритарного блока 2 сравнения и может быть использована для более достоверного определения состояния каналов (с учетом возможных ошибок в работе, их систем контроля).

Одновременно с восстановлением каналов продолжается процесс функционирования вычислительной системы по решению задач.

Использование блока 5 фиксации состояния каналов в уст-ройстве для переключения каналов вычислительной системы позволяет

5 отключить неисправный канал и перевести его в режим восстановления без нарушения нормального функционирования вычислительной системы. Этим обеспечивается повышение надежности вычислительной системы. Использование анализаторов состояния систем контроля и мажоритарного блока позволяет повысить достоверность результатов, выдаваемь1х вычислительной системой5 Технико-экономический эффект от применения данного изобретения заключается в предотвращении отказов системы за счет своевременного обнаружения и устранения отказов в каналах.

30

Формула изобретения

1.Устройство для переключения каналов вычислительной системы по авторскому свидетельству № 383047, отличающееся тем, что, с целью расширения функциональных возможностейустройства оно содержит анализатор состояния мажоритарного блока сравнения, анализатор состояния систем контроля и блок фиксации состояния каналов, первые входы которых соединены с контрольными выходами каналов, вторые входы -- с выходами мажоритарного блока сравнения, а выходы - с дополнительными входам.и каналов.

2.Устройство по. П.1, отличающееся тем, что блок фиксации состояния каналов содержит счетчики сбоев и анализатор состояния каналов, выходы которого соединены с входами соответствующих-счетчиков сбоев.

Источники информации, во внимание при экспертизе

1. Авторское свидетельство СССР № 383047, кл. G 06 F 9/00, от. 05.02.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1982 |

|

SU1086432A2 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2003 |

|

RU2264648C2 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2011 |

|

RU2481619C1 |

Авторы

Даты

1979-05-05—Публикация

1976-04-26—Подача