Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем.

Известно устройство резервирования [1], состоящее из К блоков каналов коммутации, К блоков управления коммутаторами, мажоритарного элемента, блока анализа, управляющего блока, генератора тактовых импульсов, блока установки начального состояния.

Недостатком данного устройства резервирования является невозможность многократного переключения между каналами в условиях возможных сбоев.

Наиболее близким к заявляемому устройству является устройство резервирования (прототип), используемое в резервированной двухпроцессорной вычислительной системе [2] и содержащее два идентичных канала и схему сравнения. Каждый канал содержит элемент ИЛИ, выход которого подключен к первому входу триггера и первому входу временного анализатора исправности, вход которого подключен к выходу импульсного генератора, а выход к первому входу счетчика сбоев и второму входу триггера, выход которого подключен к первому входу элемента ИЛИ-НЕ, первый выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, второй выход счетчика сбоев первого канала подключен к первому входу схемы сравнения, второй выход счетчика сбоев второго канала подключен ко второму входу схемы сравнения, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выход элемента ИЛИ-НЕ первого канала является первым выходом устройства резервирования и подключен к коммутатору первого канала, выход элемента ИЛИ-НЕ второго канала является вторым выходом устройства резервирования, предназначенным для управления коммутатором второго канала, первый вход элемента ИЛИ является входом устройства резервирования и подключен к выходу процессора, второй вход элемента ИЛИ является вторым входом устройства резервирования и подключен к выходу схемы начальной установки.

Недостатком прототипа является сложность увеличения числа переключений между каналами. Так, например, для двухразрядной схемы сравнения максимальное число переключений между каналами составляет 7. Увеличение числа переключений может быть обеспечено только за счет увеличения разрядности счетчиков сбоев, усложнения схемы сравнения и увеличения числа линий от схемы сравнения, предназначенных для связи со счетчиками сбоев основного и резервного каналов. В прототипе, при двухразрядных счетчиках сбоев, от каждого канала для связи со схемой сравнения требуются по две линии. При трехразрядных счетчиках сбоев - по три линии и т.д. Увеличение числа межканальных связей от схемы сравнения и усложнение схемы сравнения приводят к усложнению устройства резервирования и снижению надежности.

Техническим результатом заявляемого изобретения является расширение функциональных возможностей, упрощение и повышение надежности устройства резервирования.

Технический результат достигается тем, что в устройство резервирования, содержащее два идентичных канала, каждый из которых содержит элемент ИЛИ, первый вход которого соединен с первым входом счетчика сбоев, является первым входом канала устройства резервирования и подключен к выходу схемы начальной установки, второй вход является вторым входом канала устройства резервирования и подключен к выходу процессора; выход импульсного генератора через временной анализатор исправности подключен к второму входу счетчика сбоев; выход элемента ИЛИ подключен к второму входу временного анализатора исправности, введены второй элемент ИЛИ, триггер, а в каждый канал введен третий элемент ИЛИ; в каждом канале выход счетчика сбоев подключен к первому входу третьего элемента ИЛИ, выход которого является выходом канала устройства резервирования, соединенным с входом коммутатора соответствующего канала, первый вход импульсного генератора подключен к выходу схемы начальной установки, а второй - к выходу процессора; также в устройстве резервирования первый вход второго элемента ИЛИ подключен к выходу временного анализатора исправности первого канала, второй вход второго элемента ИЛИ подключен к выходу временного анализатора исправности второго канала, выход второго элемента ИЛИ подключен к первому входу триггера, второй вход которого соединен со схемой начальной установки первого канала; первый выход триггера подключен к второму входу третьего элемента ИЛИ первого канала, а второй выход триггера подключен к второму входу третьего элемента ИЛИ второго канала.

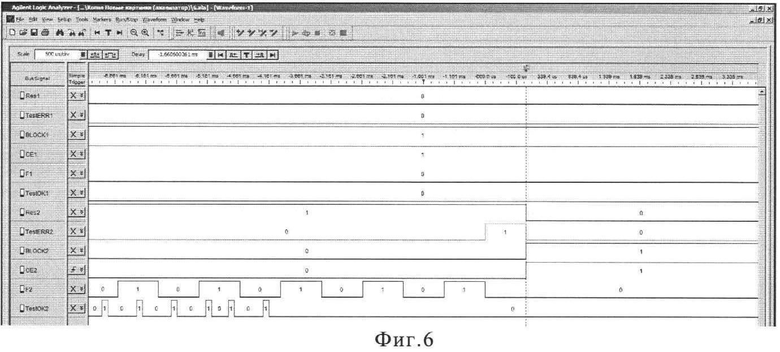

На фиг.1 приведена структурная схема предлагаемого устройства.

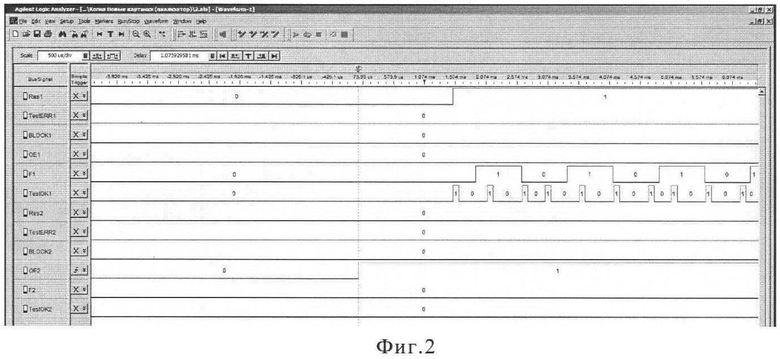

На фиг.2 приведена диаграмма работы устройства в отсутствии сбоев (работает первый канал).

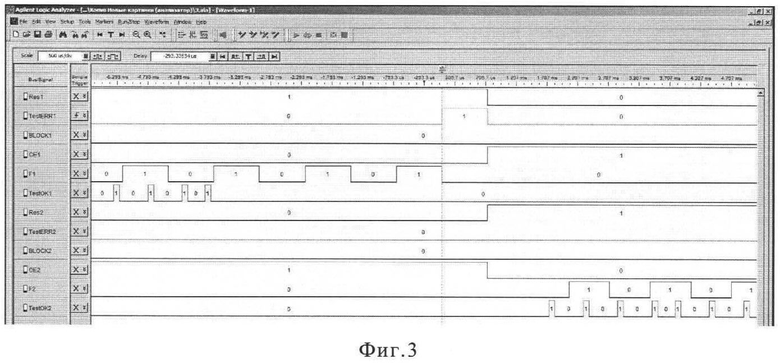

На фиг.3 приведена диаграмма работы устройства при сбое на первом канале и переходе на второй канал.

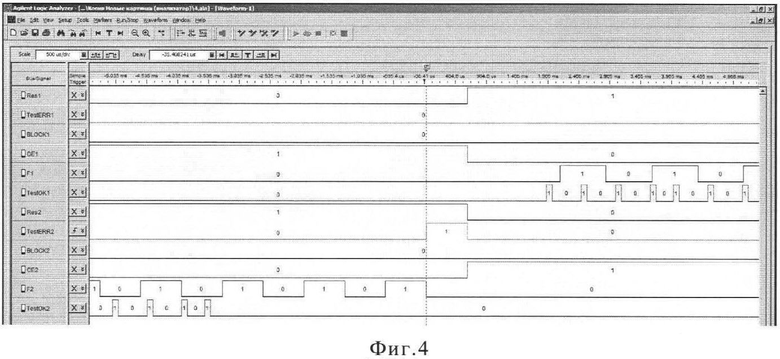

На фиг.4 приведена диаграмма работы устройства при сбое на втором канале и переходе на первый канал.

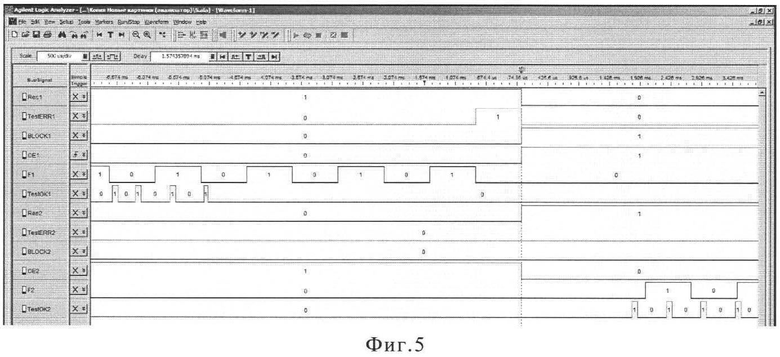

На фиг.5 приведена диаграмма работы устройства при последнем (4) сбое на первом канале и переходе на второй канал (блокировка первого канала, сформировался сигнал BLOCK 1).

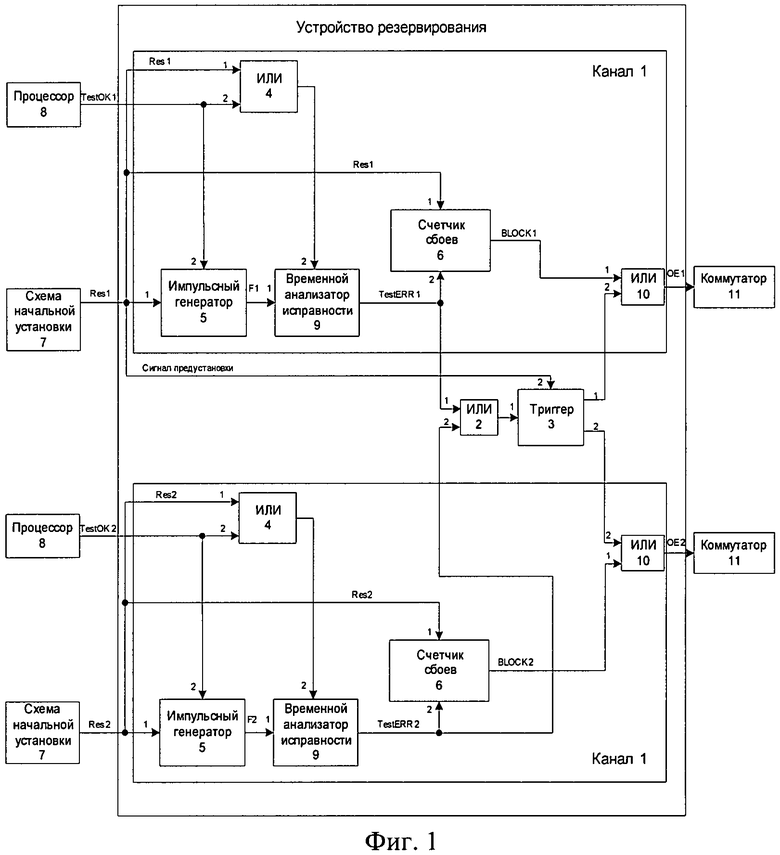

На фиг.6 приведена диаграмма работы устройства при последнем (4) сбое на втором канале (блокировка второго канала, сформировался сигнал BLOCK 2).

Устройство резервирования, представленное на фиг.1, содержит два идентичных канала 1, элемент ИЛИ 2, триггер 3. В каждом канале первый вход элемента ИЛИ 4 является первым входом устройства резервирования и соединен с первым входом импульсного генератора 5, счетчика сбоев 6 и выходом схемы начальной установки 7; второй вход элемента ИЛИ 4 является вторым входом устройства резервирования и соединен со вторым входом импульсного генератора 5 и выходом процессора 8; выход импульсного генератора 5 соединен с первым входом временного анализатора исправности 9, второй вход которого соединен с выходом элемента ИЛИ 4; выход счетчика сбоев 6 соединен с первым входом элемента ИЛИ 10, выход которого является выходом канала и подключен к входу коммутатора 11; также в устройстве резервирования первый вход элемента ИЛИ 2 соединен с выходом временного анализатора исправности 9 и вторым входом счетчика сбоев 6 первого канала, а второй вход - с выходом временного анализатора исправности 9 и вторым входом счетчика сбоев 6 второго канала; выход элемента ИЛИ 2 соединен с первым входом триггера 3, второй вход которого соединен с выходом схемы начальной установки 7, подключенной к первому каналу; первый выход триггера 3 соединен с вторым входом третьего элемента ИЛИ 10 первого канала, а второй выход - с вторым входом третьего элемента ИЛИ 10 второго канала.

Временные диаграммы, представленные на фиг.2-6, поясняют работу устройства.

Устройство работает следующим образом: переключение на резервный канал осуществляется по факту отказа канала или сбоя.

Информация о количестве сбоев используется только для формирования сигналов на блокирование обоих каналов при достижении заранее выбранного числа переключений.

В каждом канале в исходном состоянии, при низком уровне сигнала RES схемы начальной установки 7, импульсный генератор 5, временной анализатор исправности 9, счетчик сбоев 6 заблокированы, а триггер 3 сигналом схемы начальной установки 7 установлен в состояние, при котором элемент 10 открывает коммутатор 11 первого канала и разрешает его работу.

При изменении сигнала Res из логического нуля в логическую единицу разрешается работа импульсного генератора 5, временного анализатора исправности 9, счетчика сбоев 6. Первым сигналом исправности TestOK, поступающим с процессора 8, разблокируется по выходу импульсный генератор 5 и импульсы с его выхода начинают поступать на вход временного анализатора исправности 9. В случае работоспособности процессора формируется последовательность импульсов TestOK, которые обнуляют (устанавливают в исходное состояние) временной анализатор исправности 9 устройства резервирования. При этом сигналы с импульсного генератора 5 на счетчик сбоев 6 не поступают, и работа осуществляется на первом канале.

Если от процессора 8, в случае неисправности, не поступят сигналы TestOK, то временной анализатор исправности 9 не сбросится, заполнится и сформирует импульс (сигнал ошибки), который поступает на счетчик сбоев 6, увеличивая его значение на единицу, и на триггер 3, переключая его в противоположное состояние. При этом начинает работать резервный канал. При последующих сбоях, переключения между каналами повторяются аналогично.

В рассмотренном устройстве число требуемых переключений определяется разрядностью счетчика сбоев 6, что достаточно просто реализуется. При этом число межканальных связей не зависит от выбранного числа переключений (две линии).

Для выбора требуемого числа переключений в счетчиках сбоев предусмотрена блокировка изменения состояния после поступления требуемого числа импульсов. Переход счетчиков сбоев в последнее состояние принимается за отказ каналов и, следовательно, за отказ системы. Следует отметить, что необходимость ограничения числа переключений между каналами обусловлена требованиями по установлению критерия отказа системы.

Увеличение числа переключений между каналами позволяет расширить область применения резервированных вычислительных систем в условиях возможных многочисленных сбоев. Причинами сбоев могут быть различные факторы (электромагнитные помехи, радиационные воздействия различного происхождения, электрические наводки и т.д.).

Литература

1. Устройство резервирования. - Патент на изобретение RU 02207616, G06F 11\20 от 15.06.2001.

2. Резервированная двухпроцессорная вычислительная система. - Патент на изобретение RU 2264648, G06F 11/20 от 02.12.03 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2460121C1 |

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2003 |

|

RU2264648C2 |

| Самодиагностируемая бортовая вычислительная система с резервированием замещением | 2017 |

|

RU2657166C1 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| Многоканальная самодиагностируемая вычислительная система с резервированием замещением и способ повышения ее отказоустойчивости (варианты) | 2016 |

|

RU2634189C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем. Технический результат заключается в расширении функциональных возможностей, упрощении и повышении надежности устройства резервирования. Такой результат достигается за счет того, что в устройство резервирования, содержащее два идентичных канала, каждый из которых содержит элемент ИЛИ, счетчик сбоев, импульсный генератор, временной анализатор исправности, введены второй элемент ИЛИ, триггер, а в каждый канал введен третий элемент ИЛИ. 6 ил.

Устройство резервирования, содержащее два идентичных канала, каждый из которых содержит элемент ИЛИ, первый вход которого соединен с первым входом счетчика сбоев, является первым входом канала устройства резервирования и подключен к выходу схемы начальной установки, второй вход является вторым входом канала устройства резервирования и подключен к выходу процессора; выход импульсного генератора через временной анализатор исправности подключен к второму входу счетчика сбоев; выход элемента ИЛИ подключен к второму входу временного анализатора исправности, отличающееся тем, что в него введены второй элемент ИЛИ, триггер, а в каждый канал введен третий элемент ИЛИ; в каждом канале выход счетчика сбоев подключен к первому входу третьего элемента ИЛИ, выход которого является выходом канала устройства резервирования, соединенным с входом коммутатора соответствующего канала, первый вход импульсного генератора подключен к выходу схемы начальной установки, а второй - к выходу процессора; также в устройстве резервирования первый вход второго элемента ИЛИ подключен к выходу временного анализатора исправности первого канала, второй вход второго элемента ИЛИ подключен к выходу временного анализатора исправности второго канала, выход второго элемента ИЛИ подключен к первому входу триггера, второй вход которого соединен со схемой начальной установки первого канала; первый выход триггера подключен к второму входу третьего элемента ИЛИ первого канала, а второй выход триггера подключен к второму входу третьего элемента ИЛИ второго канала.

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2003 |

|

RU2264648C2 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| US 4797884 А, 10.01.1989 | |||

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| US 5491787 A, 13.02.1996 | |||

| US 6327670 B1, 04.12.2001 | |||

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| US 4872106 A, 03.10.1989. | |||

Авторы

Даты

2013-05-10—Публикация

2011-12-28—Подача