Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем.

Известна двухпроцессорная вычислительная система [1], содержащая два процессора и двухканальное устройство управления, передающее в процессоры управляющие и разрешающие сигналы. В соответствии с этими сигналами один из процессоров используется в качестве главного, а второй - в качестве подчиненного. Выбор процессора осуществляет главная схема управления. Если позиционные сигналы имеют определенное значение в течение установленного времени, взводится триггер. Двухканальное устройство управления анализирует сигналы от двух главных схем управления и автоматически назначает главный и подчиненный процессоры.

Недостаток системы в том, что используется статический сигнал готовности для выбора процессора (при «зависании» программы процессора сигнал сохраняется). При выборе основного и дублирующего процессора не используется информация о количестве сбоев каждого процессора.

Известна система с резервным процессором для управления технологическим процессом [2]. Система содержит первичный процессор для управления технологическим процессом через совокупность устройств ввода/вывода. Первичный процессор содержит центральный процессор и запоминающее устройство (ЗУ) и функционирует в соответствии с прикладной программой. ЗУ хранит запись о текущем состоянии системы с параметрами текущей операции, необходимыми для работы прикладной программы. Резервный процессор содержит ЗУ и может находиться либо в активном режиме, либо в резервном режиме. В активном режиме он полностью заменяет первичный процессор. В резервном режиме он периодически записывает в буфер ЗУ информацию о текущем состоянии, поступающую через двухпортовое ЗУ от первичного процессора. При этом запись проверяется на отсутствие ошибок. Блок управления первичного процессора работает независимо от данных о состоянии системы. Он может вырабатывать сигнал неисправности и переводить резервный процессор в активный режим.

Недостаток системы в том, что при выходе двухпортового ЗУ из строя резервный процессор не получит данных. Возможен только однократный переход «первичный-вторичный».

Известна устойчивая к отказам вычислительная система (прототип) с двумя процессорами, попеременно выполняющими функции главного и подчиненного процессоров [3]. Вычислительная система состоит из двух процессоров (каналов), схемы начальной установки, подключенной к входу процессора каждого канала, системного генератора, выход которого подключен к входу процессора каждого канала и схемы управления. Каждый процессор может работать в автономном режиме главного процессора и в режиме подчиненного процессора, контролирующего работу другого процессора. Работа в режиме главного процессора заключается в обычном выполнении инструкций и функции ввода/вывода; в подчиненном режиме процессор выполняет те же инструкции, что и главный процессор, только все линии, по которым осуществляется вывод данных, отключены. Кроме того, в подчиненном режиме схема сравнения, встроенная в процессор, сверяет результаты выходных данных обоих процессоров. Схема управления через определенные интервалы времени осуществляет переключение режимов работы процессоров для контроля процессорами друг друга. Если возникает несоответствие, то подчиненный процессор сигнализирует схеме управления об ошибке. Схема управления пытается восстановить синхронность работы процессоров, вызывая в обоих процессорах внешнее прерывание. Если же процессор вышел из строя и был в это время подчиненным процессором, то в таком случае схема будет работать без подчиненного процессора в течение времени, равного периоду переключения режимов работы процессоров. Затем неисправный процессор будет переведен в режим главного, а исправный - в режим подчиненного, где неисправность главного процессора уже будет обнаружена.

Недостаток системы в том, что при отказе системного генератора, который является общим для двух процессоров, отказывает вся система. В случае использования отдельных генераторов для каждого процессора возникнет рассинхронизация. Рассинхронизация также может наступить при неодновременном поступлении входных данных от приемных устройств.

Технический результат - повышение надежности системы за счет периодического решения диагностической задачи в каждом канале, временного анализа исправности, определения числа сбоев и выбора канала по сравнению с накопленной информации о количестве сбоев в каждом канале.

Технический результат достигается тем, что в резервированную двухпроцессорную вычислительную систему, содержащую два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу коммутатора, системный генератор, выход которого подключен к первому входу процессора первого канала, схему начальной установки, выход которой подключен ко второму входу процессора первого канала, в первый и второй каналы введены импульсный генератор, элемент ИЛИ, временной анализатор исправности, счетчик сбоев, триггер, элемент ИЛИ-НЕ, выход которого подключен ко второму входу коммутатора, второй выход процессора через элемент ИЛИ подключен к первому входу триггера и ко второму входу временного анализатора исправности, выход триггера подключен к первому входу элемента ИЛИ-НЕ, второй вход процессора соединен со вторым входом элемента ИЛИ и вторым входом счетчика сбоев, выход импульсного генератора через временной анализатор исправности подключен к первому входу счетчика сбоев и ко второму входу триггера, второй выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, а также введены системный генератор, выход которого подключен к первому входу процессора второго канала, схема начальной установки, выход которой подключен ко второму входу процессора второго канала и схема сравнения, первый вход которой подключен к первому выходу счетчика сбоев первого канала, второй вход схемы сравнения подключен к первому выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выходы коммутаторов соединены и являются выходом системы.

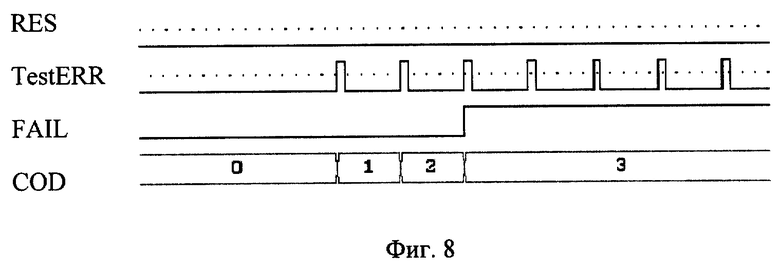

На фиг.1 приведена структурная схема предлагаемой системы.

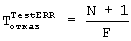

На фиг.2 приведена временная диаграмма работы системы после выхода из начального состояния.

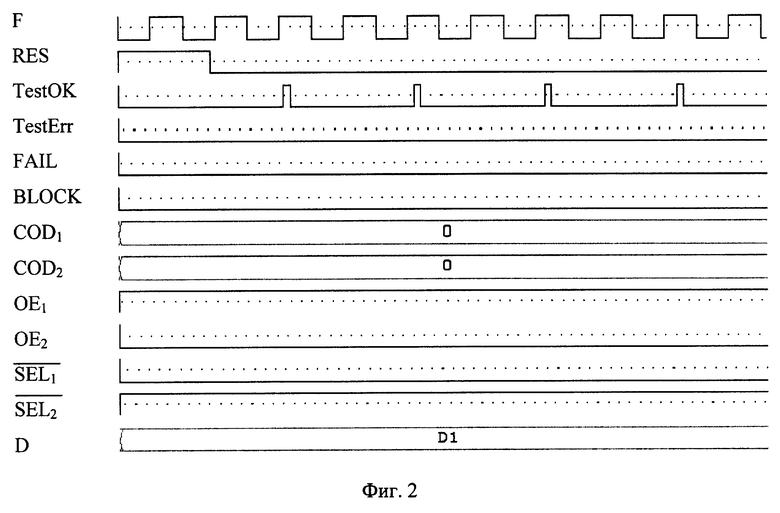

На фиг.3 приведена временная диаграмма работы системы при сбое в процессоре 5 первого канала 1.

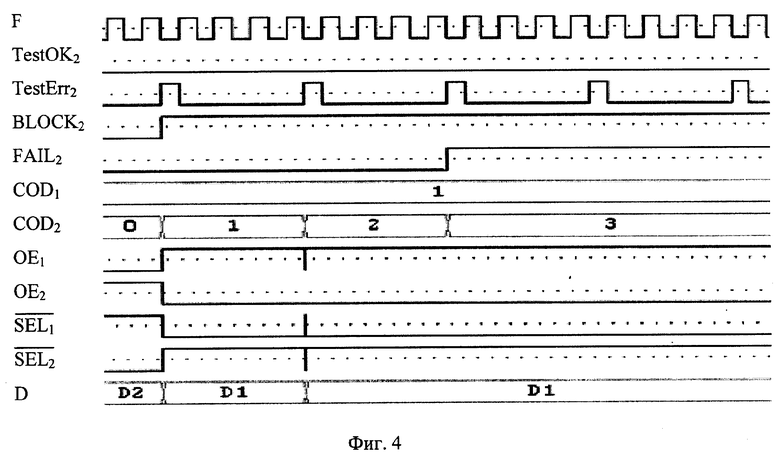

На фиг.4. приведена временная диаграмма работы системы при отказе процессора 5 второго канала 1.

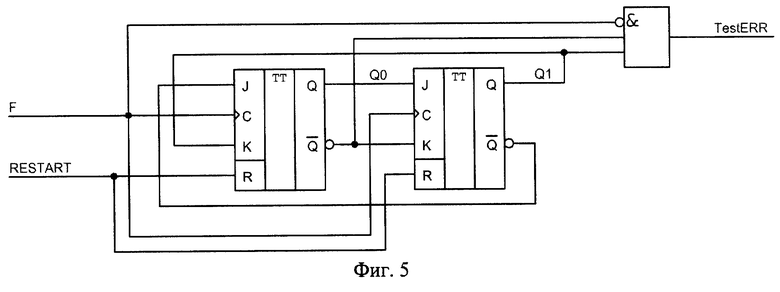

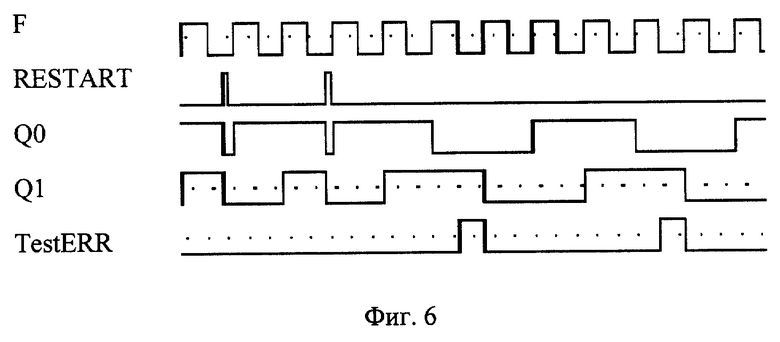

На фиг.5 приведен пример реализации временного анализатора исправности 8.

На фиг.6 - его временная диаграмма.

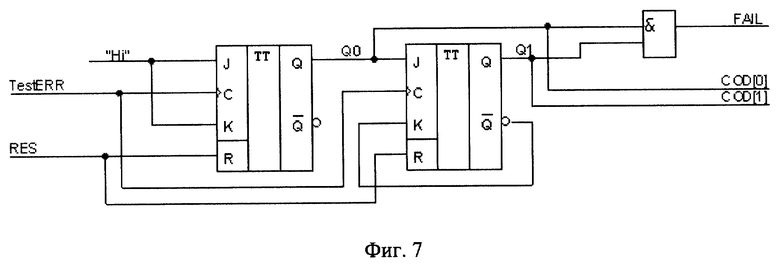

На фиг.7 приведен пример реализации счетчика сбоев 10.

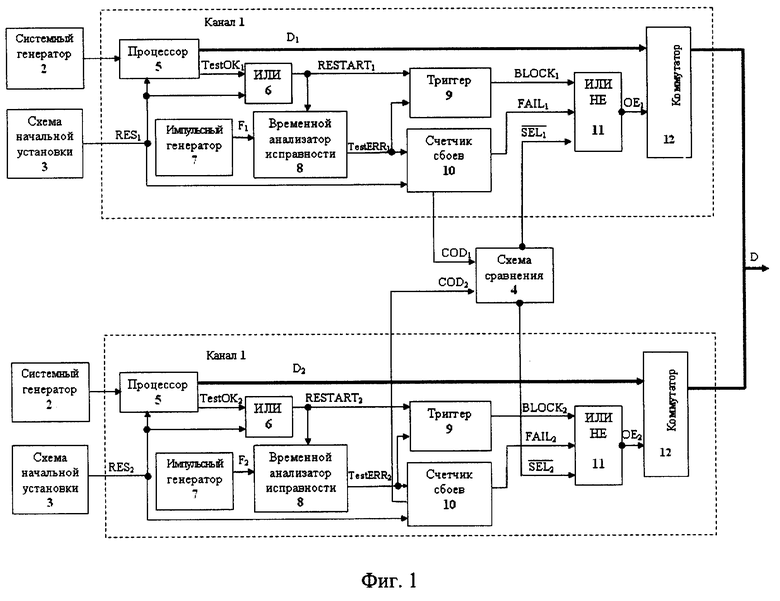

На фиг.8 - его временная диаграмма.

Резервированная двухпроцессорная вычислительная система, показанная на фиг.1, содержит два идентичных канала 1, два идентичных системных генератора 2, две идентичные схемы начальной установки 3 и схему сравнения 4. Каждый канал 1 содержит процессор 5, подключенный к элементу ИЛИ 6, импульсный генератор 7, подключенный к временному анализатору исправности 8, который подключен к триггеру 9 и счетчику сбоев 10, элемент ИЛИ-НЕ 11, подключенный к коммутатору 12, кроме того, процессор 5 подключен к коммутатору 12, элемент ИЛИ 6 подключен к временному анализатору исправности 8 и триггеру 9, к элементу ИЛИ-НЕ 11 подключены триггер 9, счетчик сбоев 10 и схема сравнения 4. К схеме сравнения 4 подключены счетчики сбоев 10 каждого канала 1. Также в системе соответствующий системный генератор 2 подключен к процессору 5 соответствующего канала 1, соответствующая схема начальной установки 3 подключена к процессору 5, элементу ИЛИ 6 и счетчику сбоев 10 соответствующего канала 1. Выходы коммутаторов 12 каждого канала 1 соединены и являются выходом системы.

Система работает следующим образом.

Перед началом работы для каждого канала 1 соответствующей схемой начальной установки 3 формируется сигнал сброса, поступающий на процессор 5, счетчик сбоев 10 и через элемент ИЛИ 6 на временной анализатор исправности 8 и триггер 9. Во время работы процессор 5 периодически формирует сигнал исправности, который через элемент ИЛИ 6 поступает на временной анализатор исправности 8 и триггер 9. В случае отсутствия сигнала исправности от процессора 5 в течение определенного интервала времени временной анализатор исправности 8 формирует импульс, поступающий на счетчик сбоев 10 и триггер 9. Каждый канал 1 выдает параллельный код количества сбоев процессора 5 с выхода счетчика сбоев 10 на схему сравнения 4 и принимает от нее сигнал выбора канала, выдает данные на выход канала через коммутатор 12 при наличии сигнала разрешения, формируемого элементом ИЛИ-НЕ 11 по сигналам от триггера 9, счетчика сбоев 10 и схемы сравнения 4.

После прохождения сигнала RES от схемы начальной установки 3 в процессоре 5 каждого канала одновременно с основной задачей периодически выполняется диагностическая задача, которая в случае успешного ее выполнения формирует короткий импульс исправности TestOK, поступающий через элемент ИЛИ 6 на временной анализатор исправности 8 и триггер 9.

Импульсный генератор 7 служит для тактирования временного анализатора исправности 8, не требует стабильной частоты и может быть выполнен как релаксационная схема на логическом элементе.

Временной анализатор исправности 8 представляет собой счетчик импульсов, поступающих от импульсного генератора 7. Сброс счетчика происходит по сигналу исправности от процессора 5 или сигналу сброса схемы начальной установки 3. На фиг.5 приведен пример реализации временного анализатора исправности на счетчике в коде Грея по модулю четыре; на фиг.6 - его временная диаграмма. Сигнал RESTART формируется элементом ИЛИ 6 из сигналов TestOK процессора 5 и RES схемы начальной установки 3.

Для известного периода Т диагностической задачи, который определяется инерционностью управляемого объекта, частота F импульсного генератора 7 определяются из соотношения

где N - максимальное число импульсов до заполнения счетчика временного анализатора исправности (на фиг.5 и 6 принято N=3).

Для расширения функциональных возможностей импульсный генератор 7 может быть выполнен перестраиваемым, например, с помощью управляемого делителя частоты.

Сбоем процессора 5 считается отсутствие импульса исправности в интервале времени

При отказе процессора 5 импульсы TestERR от временного анализа неисправности 8 будут идти с периодом

Триггер 9 служит для блокировки прохождения данных из канала сигналом BLOCK в случае прихода от временного анализатора исправности 8 импульса TestERR. При поступлении сигнала RESTART от элемента ИЛИ 6 триггер 9 разблокирует канал.

Счетчик сбоев 10 выставляет код COD количества сбоев канала и представляет собой счетчик импульсов TestERR, поступающих от временного анализатора исправности 8. Обнуление счетчика происходит по сигналу сброса RES схемы начальной установки 3. В случае прихода от временного анализатора исправности М импульсов TestOK счетчик сбоев блокирует канал сигналом FAIL. Поступление в счетчик сбоев М импульсов считается отказом канала. На фиг.7 приведен пример реализации счетчика сбоев при М=3; на фиг.8 - его временная диаграмма.

Схема сравнения 4 - комбинационная схема по сравнению кодов COD1 и COD2 из счетчика сбоев 10 двух каналов 1 формирует сигналы выбора  и

и  для каждого канала 1. Схема сравнения 4 может быть реализована на ИС КР1533СП1.

для каждого канала 1. Схема сравнения 4 может быть реализована на ИС КР1533СП1.

Коммутатор 12 представляют собой формирователь с тремя состояниями на выходе и может быть выполнен на ИС КР1533АП(3,4), КР1534АП (3-5).

Исходное состояние системы (см. фиг.2) устанавливается сигналом RES схемы начальной установки 3, поступающим на процессор 5, счетчик сбоев 10 (устанавливает код COD количества сбоев в «0» и сигнал отказа FAIL в '0') и через элемент ИЛИ 6 на временной анализатор исправности 8 и триггер 9 (устанавливает сигнал блокировки канала BLOCK в '0'). Во время окончания сигнала RES периодически в процессоре 5 каждого канала запускается диагностическая (контрольная) задача с заранее известным интервалом времени для ее решения. При нормальной работе процессора, т.е. получении правильного результата диагностической задачи в течение фиксированного интервала времени, процессор 5 каждого канала 1 формирует сигналы исправности TestOK, которые через элемент ИЛИ 6 поступают на сброс временного анализатора исправности 8 и на сброс триггера 9. Частота импульсного генератора 7 выбирается таким образом, чтобы за время решения диагностической задачи на временной анализатор исправности не могло поступить импульсов больше N-1, где N - максимальное число импульсов до заполнения счетчика временного анализатора. Таким образом, если диагностические задачи периодически решаются обоими процессорами и формируются сигналы исправности, то не происходит заполнение счетчика временного анализатора и на выходе временного анализатора исправности 8 не формируется сигнал сбоя TestERR. Схема сравнения 4, анализируя коды COD1 и COD2 количества сбоев от каждого канала 1 (все они равны нулю), выбирает первый канал 1 сигналами  (равен '0') и

(равен '0') и  (равен '1'), поступающими на элемент ИЛИ-НЕ 11 соответствующих каналов 1. В первом канале 1 сигнал OE1 от элемента ИЛИ-НЕ 11 поступает на коммутатор 12 и, таким образом, на выходной шине устройства находятся данные/команды от процессора 5 первого канала 1.

(равен '1'), поступающими на элемент ИЛИ-НЕ 11 соответствующих каналов 1. В первом канале 1 сигнал OE1 от элемента ИЛИ-НЕ 11 поступает на коммутатор 12 и, таким образом, на выходной шине устройства находятся данные/команды от процессора 5 первого канала 1.

В случае сбоя в работе любого процессора 5, например первого канала 1 (см. фиг.3), диагностическая задача не может быть решена в заданном интервале времени и, следовательно, сигнал исправности TestOK1 от процессора 5 через выбранный интервал времени не поступит на временной анализатор исправности 8. При этом счетчик импульсов временного анализатора исправности 8 в процессе заполнения сформирует сигнал TestERR1, который поступит на счетчик сбоев 10, увеличивая его значение (COD1) на единицу, триггер 9, который установит сигнал блокировки BLOCK1 в '1' (до прихода следующего импульса исправности TestOK1 от процессора 5), запрещая прохождение данных от процессора первого канала 1. Схема сравнения 4, анализируя коды COD1 (равен '1') и COD2 (равен '0') ошибок от счетчика сбоев 10 каждого канала 1, сигналами  (равен '1') и

(равен '1') и  (равен '0'), поступающими на элемент ИЛИ-НЕ 11 соответствующих каналов 1, выбирает второй канал 1. Во втором канале 1 сигнал ОЕ2 от элемента ИЛИ-НЕ 11 поступает на коммутатор 12 и, таким образом, на выходной шине устройства находятся данные/команды от процессора 5 второго канала 1.

(равен '0'), поступающими на элемент ИЛИ-НЕ 11 соответствующих каналов 1, выбирает второй канал 1. Во втором канале 1 сигнал ОЕ2 от элемента ИЛИ-НЕ 11 поступает на коммутатор 12 и, таким образом, на выходной шине устройства находятся данные/команды от процессора 5 второго канала 1.

В случае отказа в работе любого процессора 5, например второго канала 1 (см. фиг.4), сигнал исправности TestOK2 перестает поступать на временной анализатор исправности 8, счетчик импульсов которого в процессе заполнения формирует периодически импульсы TestERR2, которые поступают на счетчик сбоев 10, который, достигая максимального значения (равного трем), формирует сигнал отказа FAIL2, триггер 9, который устанавливает сигнал блокировки BLOCK в '1'. Схема сравнения 4, анализируя коды COD1 (равен '1') и COD2 (равен '3') ошибок от счетчика сбоев 10 каждого канала 1, сигналами  (равен '0') и

(равен '0') и  (равен '1'), поступающими на элемент ИЛИ-НЕ 11 соответствующих каналов 1, выбирает первый канал 1. В первом канале 1 сигнал OE1 от элемента ИЛИ-НЕ 11 поступает на коммутатор 12 и, таким образом, на выходной шине устройства находятся данные/команды от процессора 5 первого канала 1.

(равен '1'), поступающими на элемент ИЛИ-НЕ 11 соответствующих каналов 1, выбирает первый канал 1. В первом канале 1 сигнал OE1 от элемента ИЛИ-НЕ 11 поступает на коммутатор 12 и, таким образом, на выходной шине устройства находятся данные/команды от процессора 5 первого канала 1.

Источники информации

1. Патент 87333685, Япония, МКИ G 06 F 11/20, 1987 г.

2. Патент 4872106, США, МКИ G 06 F 15/00, 1989 г.

3. Патент 94296302, США, МКИ G 06 F 11/00, 1994 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ ДВУХПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2460121C1 |

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2011 |

|

RU2481619C1 |

| Самодиагностируемая бортовая вычислительная система с резервированием замещением | 2017 |

|

RU2657166C1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| МЕТОД РЕЗЕРВИРОВАНИЯ КАНАЛОВ КОНСТРУКТИВНО-ФУНКЦИОНАЛЬНЫХ МОДУЛЕЙ БОРТОВЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЕЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ НА ОСНОВЕ ИНТЕЛЛЕКТУАЛЬНОЙ ДИАГНОСТИЧЕСКОЙ СИСТЕМЫ В УСЛОВИЯХ ИНТЕГРИРОВАННОЙ МОДУЛЬНОЙ АВИОНИКИ | 2021 |

|

RU2778366C1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1594543A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем. Техническим результатом является повышение надежности системы. Устройство содержит схему сравнения, два системных генератора, две схемы начальной установки, два идентичных канала, каждый из которых состоит из процессора, коммутатора, схемы ИЛИ, счетчика сбоев, импульсного генератора, временного анализатора исправности, триггера, схемы ИЛИ-НЕ, выходы коммутаторов обоих каналов объединены и являются выходом устройства. 8 ил.

Резервированная двухпроцессорная вычислительная система, содержащая два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу коммутатора, системный генератор, выход которого подключен к первому входу процессора первого канала, схему начальной установки, выход которой подключен ко второму входу процессора первого канала, отличающаяся тем, что в первый и второй каналы введены импульсный генератор, элемент ИЛИ, временной анализатор исправности, счетчик сбоев, триггер, элемент ИЛИ-НЕ, выход которого подключен ко второму входу коммутатора, второй выход процессора через элемент ИЛИ подключен к первому входу триггера и ко второму входу временного анализатора исправности, выход триггера подключен к первому входу элемента ИЛИ-НЕ, второй вход процессора соединен со вторым входом элемента ИЛИ и вторым входом счетчика сбоев, выход импульсного генератора через временной анализатор исправности подключен к первому входу счетчика сбоев и ко второму входу триггера, второй выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, а также введены системный генератор, выход которого подключен к первому входу процессора второго канала, схема начальной установки, выход которой подключен ко второму входу процессора второго канала, и схема сравнения, первый вход которой подключен к первому выходу счетчика сбоев первого канала, второй вход схемы сравнения подключен к первому выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выходы коммутаторов соединены и являются выходом системы.

| US 5491787 А, 13.02.1996 | |||

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| US 4872106 А, 03.10.1989 | |||

| US 5136704 A, 04.08.1992. | |||

Авторы

Даты

2005-11-20—Публикация

2003-12-02—Подача