(54) УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| Устройство для передачи телеизмерений с адаптивной коммутацией | 1984 |

|

SU1267459A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1667249A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

1

Изобретение отнсхзится к технике аналого-цифрового преобразования и может быть использовано при передаче аналоговых сигналов по дискретным каналам связи.

Известно устройство кодирования адаптацией по разрядности, в котором число разрядов кодового слова меняется в соответствии с измеренным сродним значением кодового сигнала ij.

Недостатком такого устройства является неспособность слежения за быстроменяющимися, например экспоненциально, входными сигналами,а также избыточност при кодировании сигналов, обусловленной отличием текущего значения сигнала от измеренного среднего уровня.

Наиболее близким по технической сущности к заявляемому изобретению является аналого-цифровой преобразователь, содержащий блок сравнения, логическое устройство, cocTosnaee из элементов И и коммутатора, блок памяти, дифроаналоговый преобразователь и генератор импульсов 2 .

Недостатеом такся о устройства являе- ся избыточность в дискретном представлении малых входньсс сигналов, выражающвн яся в том, что в этсм случае старшие разряды равны нулю и передача их по каналу связи нецелесообразна.

Целью изобретения является устране- нение избыточности при кодировании

входных сигналов.

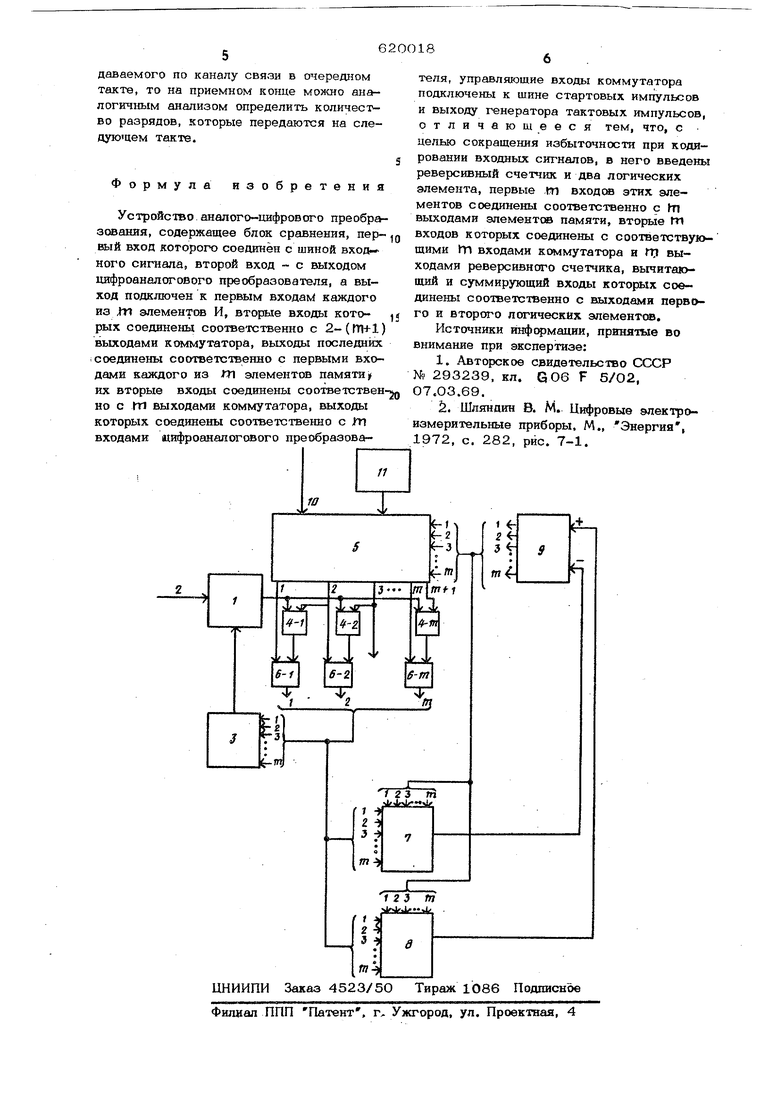

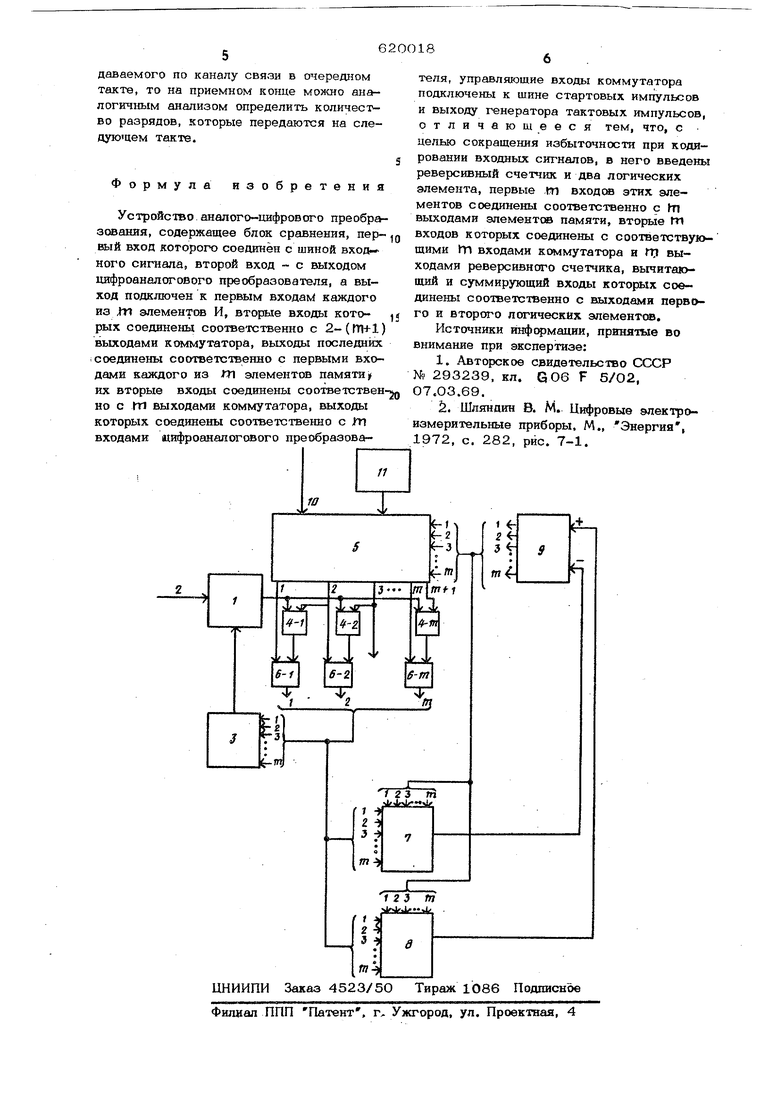

Указанная цель достигается тем, что в предлагаемое устройство, содержащее блок сравнения, первый вход которого соединен с шиной входного сигнала,

второй вход - с выходом цифроаналогового преобразователя, а выход подключен к первым входам каждого из Ш , элементов И, вторые входы которых соединены соответственно с выходами с

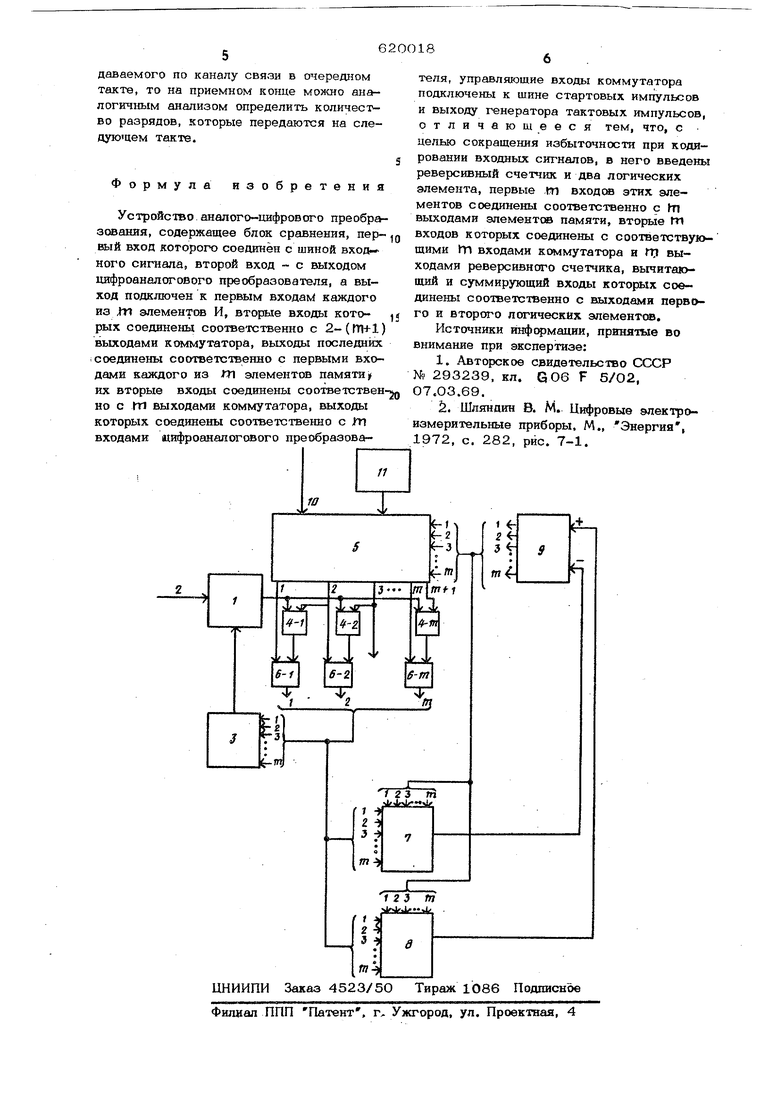

2 - (m+l) коммутатора, выходы последних соединены соответственно с первыми входами каждого из -ГП элементов памяти, их вторые входы соединены соответственно с W выходами коммутатора, выходы которых соединены соответст венно с ГС входами цифроаналогового преобразователя, управляющие входы ком мутатора подк цочены к шине стартовых импульсов и выходу генератора тактовых импульсов, дополнительно введены ревер сивный счетч.ик и два логических элемен та, первые .|Т1 входов этих элементов сое динены соответственно с ГП выходами элементов памяти, вторые ,1г входов которых соед1шены с соответствующими входами коммутатора и m выходами ре версивного счетчика, вычитающий и суммирующий входы которых соединены со01 етственно с выходами первого и второго- логических элементов. На чертеже дана структурна электри ческая схема предлагаемого устройства алаяого-иифров ого преобразова1«ля. Устройство содержит блох 1 сравнени первый вход которого соединен с шиной 2 входного сигнала, второй вход о выходом цифроаналогового преобразоватеня 3, выход подзсяючен к первым входам каждого из элементов И 4, вторые входы которых соедине1Ш1 соответственно с выходами с 2 - (-Тп -f 1} коммутато ра 5, а выходы элвменто В И 4 соединены с первыми входами каждого из элементов памяти 6, их вторые входы соединены соотйетственно с Ш выходами коммутатора 5, а выходы элементов на,яти 6 - соотБетс1Бенно с входами цифр аналогового преобразователя 3 и с первыми входами логических элементов 7 и 8, вторые ;ГП входы последних соединены соотзетственио с Ш входами коммутатора 5 и с выходами реверсивного счетчика 9, а .выходы логических элементов 7 и. 8, соединены соответственно с вычитающим и суммирующим входами реверсивного счетчика 9, управляющие вхо ды коммутатора 5 соединены с шиной 1О стартовых импульсов и выходом генератора 11 тактовых импульс.ов. Устройство работает следующим образом. Стартовый импульс, поступающий на управляющий вход коммутатора 5, переписывает содержимое реверсивного счвтчика 9, KOTOpiDe а исходном состоянии равно нулю, в счетчих коммутатора, Тшстовые импульсы, поступающие на управляющий вход коммутатора 5, с выхода генератора 11 тактовых импульсов появляются поочередно на одном из (ти-1) выходов коммутатора 5, начиная с ( 1 +1), где i - содержимое реверсивного счетчика 5, т.е. первый импульс появляется на ( i +1)-ом выходе, второй- на {i +2)-ом и т. д. При помощи этих импульсов преобразуется входная аналоговая величина методом порааряд ного кодирования в двоичное (JT1 - i )разрядное число благодаря применению элементов И 4, элементов памяти 6, цнфроаналогавого преобразователя 3 и блока 1 сравнения. По окончании такта преобразования начинается анализ полученного двоичного чибла. /1ля,этой цели используются логические элементы 7 и 8, ко входам которых подключены выходы элементов памяти б и выходы реверсивного счетчика 9, Логический элемент 8 выполняет логическую функцию 1-Ц где - содержимое ( i +1)-г6 разряда в двоичном представлении преобразуе мого напряжения, 1 - число, записанное в реверсив«« ном счетчике 9. На выходе логического элемента 9 появляется сигнал, равный единице в том случае, если ( и ) (старщий) разряд равен нулю. Сигнал с выхода логического элемента 8 поступает на вход сложения реверсивного счетчика 9 и увеличивает его содержимое на единицу, благодаря этому в очередном такте преобразования число разрядов уменьшается на единицу. Логический элемент 7 выполняет логическую функцию , к i-n где X j. - содержимое К -го разряда aatv ичного числа; 3 - чкспо, записанное в реверснвном счетчике 9; m - максимальное число разрядов двоичного числа; П - логическое произведение. Следовательно, если во всех разрядах, начиная с (й+1), содержатся единицы, то на выходе логического элемента 7 появляется сигнал/который подает ся на вход вычитания реверсивного счетчика 9, и в очередном такте npeia6paзования число разрядов.увеличивается на единицу, что позволяет преобразовать сигнал вдвое болыие предыдущего по абсолютной величине, т.е. предлагаемое устройство следит за экспоненциально быстрыми изменениями сигнала. В канал связи поступают не все 1И peasрядов, а только (m-i) разрядов, поскольку первые Л разрядов отключаются и их содержимое равно нулю. Так как изменение числа разрядов происходит на основании анализа двоичного числа, иере-т

даваемого по каналу связи в очередном такте, то на приемном конце моясно аналогичным анализом определить количество разрядов, которые передаются на следующем такте.

Формула изобретения

Устройство аналого-цифрового преобразования, содержащее блок сравнения, первый вход которого соединён с шиной входного сигнала, второй вход с выходом цифроаналогового преобразователя, а выход подключен к первым входам каждого из jn элементов И, вторые входы которых соединены соответственно с 2- (ГГН-1) выходами коммутатора, выходы последних i соединены соответственно с первыми входами каждого из fn элементов памяти jf их вторые входы соединены соответственно с tn выходами коммутатора, выходы которых соединены соответственно с Л1 входами мифроаналогового преобразователя, управляющие входы коммутатора подключены к шине стартовых импульсов и выходу генератора тактовых импульсов, отличающееся тем, что, с целью сокращения избыточности при кодировании входных сигналов, в него введены реверсивный счетчик и два логических элемента, первые ,|Т) входов этих элементов соединены соответственно с hn выходами элементда памяти, вторые fn входов которых соединены с соответствующими Гп входами коммутатора и nj выходами реверсивного счетчика, вычитающий и суммирующий входы которых соединены соответственно с выходами первого и второго логических элементов.

Источники инфс мации, пртсятые во внимание при экспертизе:

S. Шлянпин В. М. Цифровые электроизмерительные приборы, М., Энергия, 1972, с. 282, рис. 7-1.

Авторы

Даты

1978-08-15—Публикация

1976-11-09—Подача