. 1 : Предложенное устройство относится к области регулирования сигналов и может быть Использовано в каналах воспроизведения цифровых сейсморазведочных станций и устройствах визуализации обработанной информации с целью сжатия динамического диапазона сигна лов, представленных в цифровом.виде, В известном регуляторе циф ровая автоматическая регулировка амплитуд применяется для сжатия динамического диапазона сигналов, что обеспечиёает возможность визуального просмотра информации 1, При машинной обработке используется нормирование по среднему значению модуля входного сигнала в некотором окне, Однако конструкция известного регулятора очень сложна из-за необходимости использования промежуточной памяти большого объема, в которой следует разместить выборки (около 200 выборок) в, предеДругое известное устройство регулировки амплитуд характеризуется мень шим объемом оборудования, обеспечивает избирательное сжатие динамического ддаапазоиа сигналов и в то же время позволяет избежать серьезных искажеНИИ сйгналй, й6 в.недоетаточной степе ни, и форма/представления информации на выходе - аналоговая |2, Н&иболёё близкийкданнЪму изобретению по технической сущности является цифровой автоматический регулятор амплитуд сейсми еской I станции 3, содержйадий накопитель, сумматор, арифметические блоки, регистр кода порядка и регистр:результата, принцип действия которого основан на умножении сейсмических колебаний на специальный множитель, величина которого изменяется, в зает1симости от амплитуда колебаний на выходе регулятора, Устройст- во сконструировано так, что на основании выходных данных.и информации от предыдущих регулировок оно определяет, находится ли выходной сигнал внутри заданного интервала алшлитуд, Есэти на выходе регулятора наблюдается высокий уровень,то множитель уменьшается, а если низкий - то увеличивается. Таким o6pia3 ом, устройств о осуществляет регулировку амплитуд через петлю обратной связи,поддерживающей уровень колебаний на выходе в цифр-эвом виде в установленных пределах подобно- тому, как это осуществляется в аналоговых

662909

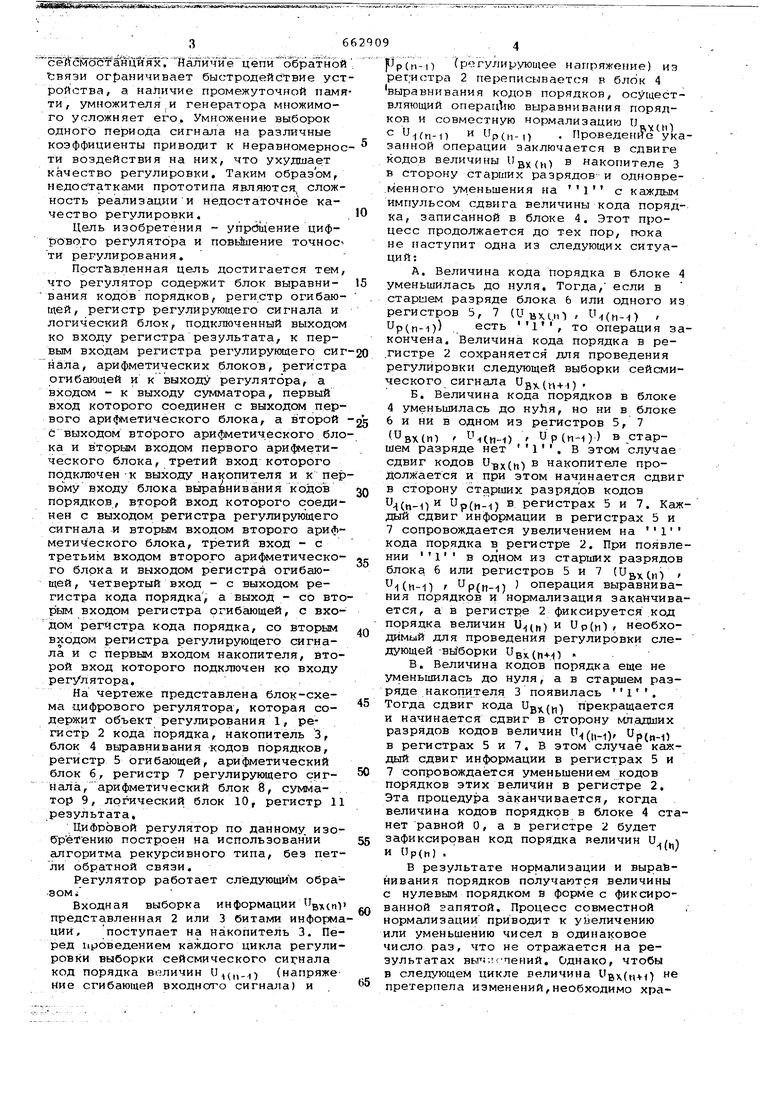

3 certSf ocTaHuftHx, KaHHVife цепй°Ъбратн6й йвязи ограничивает быстродействие уст ройства, а наличие промежуточной памя ти, умножителями генератора множимого усложняет его. Умножение выборок одного периода сигнала на различные коэффициенты приводит к неравномерное ти воздействия на них, что ухудшает качество регулировки. Таким образом, недосгтатками прототипа являются, сложность реализации и недостаточное качество регулировки. Цель изобретения - упрс щение цифрового регулятора и повьшение точное ти регулирования. Поставленная цель достигается тем что регулятор содержит блок выравнивания кодовпорядков, регистр огибающей, регистр регулирующего сигнала и логический блок, подключенный выходом ко входу регистра результата, к первым входам регистра регулирующего сиг нала, арифметических блоков, регистра огибающей и к выходу регулятора, а входом - к выходу сумматора, первый вход которого соединен с выходом первого ари етического блока, а второй с выходом второго арифметического бло ка и вторым входом первого арифметического блока, третий вход которого подключен-к выходу накопителя и к пер вому входу блока выравнивания кодов порядков, второй вход которого соединен с выходом регистра регулирукнцего сигнала и вторьзм входом второго арифметического блока, третий вход - с третьим входом второго арифметического блока и выходом регистра огибающей , четвертый вход - с выходом регистра кода порядка, а выход - со вто рым входом регистра огибающей, с вхо дом регистра кода порядка, со вторым входом регистра регулирующего сигнала и с первым входом накопителя, второй вход которого подключен ко входу регулятора, На чертеже представлена блок-схема -цифрового регулятора, которая содержит объект регулирования 1, регистр 2 кода порядка, накопитель 3, блок 4 выравнивания кодов порядков, регистр 5 огибающей, арифметический блок 6, регистр 7 регулирующего сигнала,арифметический блок 8, сумматор 9, логический блок 10, регистр 1 результата. Цифровой регулятор по данному, изо брёТению построен на использовании алгоритма рекурсивного типа, без пет ли обратной связи. Регулятор работает следующим обра Входная выборка информации вткп) представленная 2 или 3 битами информ ции, поступает на накопитель 3. Пе ред проведением каждого цикла регули ровки выборки сейсмического сигнала код порядка величин П,,.) (напряже ние сгибающей входного сигнала) и PV(-i) (р- гулирующее напряжение) из регистра 2 переписывается в блок 4 выравнивания кодов порядков, осугцествляющий операц1 1ю выравнивания порядков и совместную нормализацию П (,N с и(„., и UP(H.,) . Проведение указанной операции заключается в сдвиге кодов величины Ig, в накопителе 3 в сторону старших разрядов- и одновре.менного ум.еньшения на с каждым импульсом сдвига величины кода поряд-. Ка, записанной в блоке 4. Этот процесс продолжается до тех пор, пока не наступит одна из следующих ситуаций:А, Величина кода порядка в блоке 4 уменьшилась до нуля. Тогда, если в старшем разряде блока 6 или одного из регистров 5, 7 (U щхиО , U-((n--i) / Up(n-i)) .. есть Ч, то операция закончена. Величина кода порядка в ре.гистре 2 сохраняете для проведения регулировки cлeдs oщeй выборки сейсмического сигнала Ugxln-t--) Б, Величина кода порядков в блоке 4 уменьшилась до ну)1Я, но ни в блоке 6 и ни в одном из регистров 5, 7 (п) f HH-I) Up(n-i)) в старВ этом случае шем разряде нет сдвиг кодов U-BxCn) накопителе продолжается и при этом начинается сдвиг в сторону старших разрядов кодов и()И Up(.) в регистрах 5 и 7, Каждый сдвиг информации в регистрах 5 и 7 сопровождается увеличением на кода порядка в регистре 2, При появлении ч в одном из старших разрядов блока 6 или регистров 5 и 7 (Ug(f,) , -l(n-l) f p(n--i) операция выравнивания порядков и нормализация заканчивается, а в регистре 2 фиксируется код порядка величин U(f,) Up(n), необходимый для проведения регулировки следующей -выборки UBx.(n-.i1 В, Величина кодов порядка еще не уменьшилась до нуля, а в старшем разряде накопителя 3 появилась . Тогда сдвиг кода Ug( прекращается и начинается сдвиг в сторону младших разрядов кодов величин П(,н)/ Upf.) в регистрах 5 и 7, В этом случае каждый сдвиг информации в регистрах 5 и 7 сопровождается уменьшением кодов порядков этих величин в регистре 2, Эта процедура заканчивается, когда величина кодов порядков в блоке 4 станет равной О, а в регистре 2 будет зафиксирован код порядка величин U,/. и Up(H) . В результате нормализации и выравнивания порядков получаются величины с нулевым порядком в форме с фиксированной запятой. Процесс совместной нормализации приводит к увеличению или уменьшению чисел в одинаковое число раз, что не отражается на результатах ,; -пений. Однако, чтобы в следующем цикле величина texCu-n) претерпела изменений,необходимо хранить порядок величии , и Up(n)B ре гистре 2 кода порядка. По okoH4aHHH процедуры выравнивания порядков и нормсшизаиии код величины UBx(h) переписывается из накопителя 3 в первый арифметический блок 6, а обратный код величины огибающей из регистра 5 во второй арифметический блок 8. Вычисление разности кодов величин ицу(,) - U() производится в сумматоре 9, куда они поступают по команде из логического блока io и бло ков 6 и 8. Полученная разность переписывается из блока 10 в блок 8, где производится операция умножения ее на величину дЪ/Т , В целях упрощения в предлагаемом регуляторе выбор постоянной времени Т производится таким образом, чтобы соотношение A-tfe было кратно 2. Подобный выбор 4i/t упрощает его физическое задание, которое сводится к подаче потенциала n(i-t/f) из блока 10 по определенной шине, соответствующей выбранной величине , равной 4, В, 16 или 32 мс, в блок 8. При перезаписи разности UgxCn) Ui(nTi) из сумматора 9 в блок 8 логический блок 10 анализирует ее величину и, если Ugy( U(f, , то в блок 8 записывается прямой код разности, а при Ug((,) и („) - обратный код разности. Величина,полученная в результате приращение огибающей ди(,) переписывается из блока 8 в ари етичэский блок 6,а по окончании перезапи си код огибающей сейсмического сигнала переносится из регистра 5 в блок 8 Вычисление суммы и(„) Ди(,) про изводится в сумматоре 9, а результат вычислений - Б-регистр 5 и блок 6, Од новременно осуществляется перезапись обратных кодов Up(n-1)йз регистра V в блок 8. Таким образом, в блоках б и 8 будут находить.ся код П.,) и обрат ный код Up(n-i) . Нахождение величин 4i.Up(h) и Пр(ц) осуществляется подобно ди( и и() . Анализ разности, вычис ленной в сумматоре 9, производится блоком 10. Результат вычислений Upj, переписы вается с выходов сумматора 9 блоком 10 в блок 8 и в регистр 7. Для вычисления операции деления ко ды выборки иg,(j,-) сейсмического сигнала переписываются в блок б. Фактически операция деления заменена суммированием по модулю 2 прямого и обратного кодов Ug(j,-) и и р(1 и выполняется в сумматоре 9. Результат деления пере писывается блоком 10 в регистр резуль тата 11 и представляет собой отрегулированное значение выборки UbbixCn) сейсмического сигнала в цифровом виде Одновременно с пересаписью информации в регистр 11 блок 10 выдает сигнал в объект регулирования 1, разрешая выдачу новой порции информации, т.е. следующей выборки + i) Эффект от использования данного изобретения заключается в сокращении оборудования, в осуществлении возможности визуализации информации на лю- . бой стадии обработки и повышения точности регулирования в каналах воспроизведения цифровых станций за счет индивидуальной регулировки в каждом канале. Формула изобретения Цифровой регулятор, содержащий накопитель, сумматор, ари 1метические блоки, регистр кода порядка и регистр результата, отлич ающийс я тем, что, с целью упрощения регулятора и повышения точности регулирования, он содержит блок выравнивания кодов порядков, регистр огибающей, регистр регулирующего сигнала и логический блок, подключенный выходом ко входу регистра результата, к первым входам регистра регулирующего сигнала, арифметических блоков, регистра огибающей и к выходу регулятора, а входом к выходу сумматора, первый вход которого соединен с выходом первого арифметического блока, а второй - с выходом второго арифметического блока и вторым входом первого арифметического блока, третий вход которого подключен к выходу накопителя и к первому входу блока выравнивания кодов порядков, второй вход которого соединен с выходом регистра регулирующего сигнала и вторым входом второго арифметического блока, третий вход ,- с третьим входот второго арифметического блока и выходом регистра огибающей, четвертый вход - с выходом регистра кода порядка, а выход - со вторым входом регистра огибающей, с входом регистра кода порядка, со вторым входом регистра регулирующего сигнала и с первым входом накопителя, второй вход которого подключен ко входу регулятора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 300859, кл, GOI V 1/2, 1969. г. Патент США № 3872465; кл. 340-347, 1975. 3. Цифровой регулятор сейсморазвеочной станции ДРЗ IV , США,фирма ТехЬз nnstrument , 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой автоматический регулятор амплитуд сейсмических сигналов | 1976 |

|

SU610035A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Цифровой измеритель параметров случайных процессов с распределением Накагами | 2020 |

|

RU2742695C1 |

| Цифровой измеритель фазовых флуктуаций сигналов | 1986 |

|

SU1368805A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Устройство для адаптивного сжатия информации | 1986 |

|

SU1383428A1 |

| Сейсмостанция | 1987 |

|

SU1430924A1 |

| Цифровой измеритель скорости перемещения | 1983 |

|

SU1165997A2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| Цифровой калибратор фазы | 1986 |

|

SU1352402A1 |

Авторы

Даты

1979-05-15—Публикация

1977-01-03—Подача