(54) ЦИФРОВОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

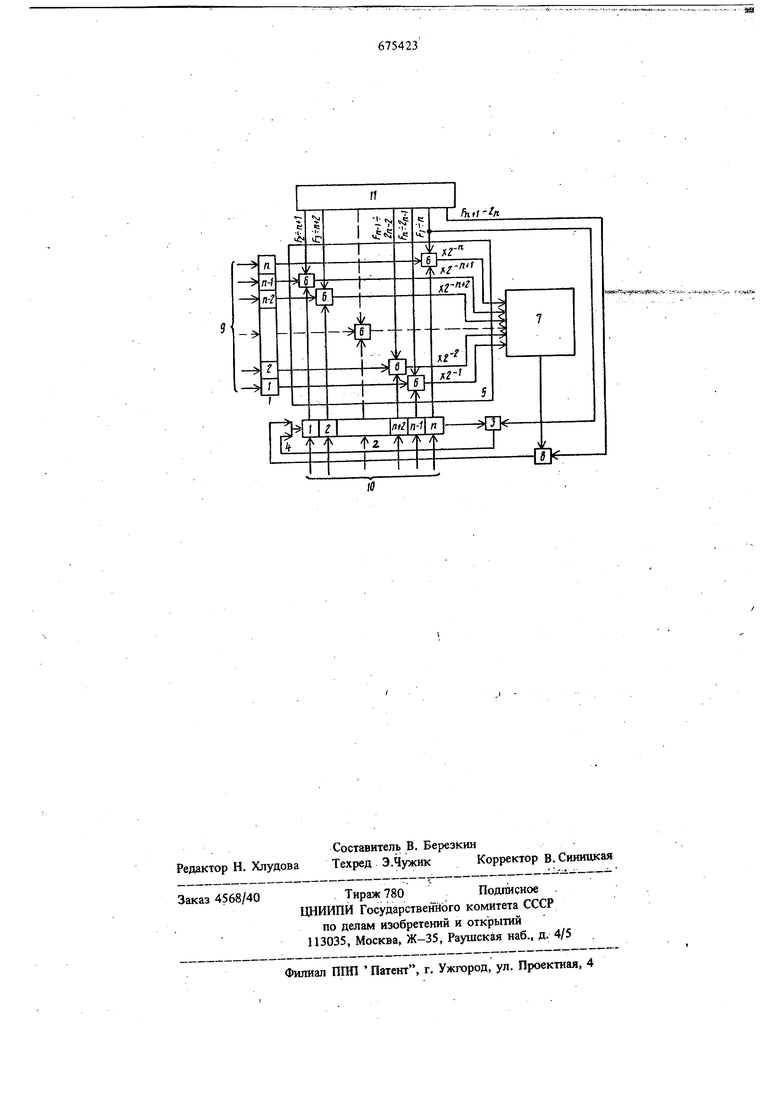

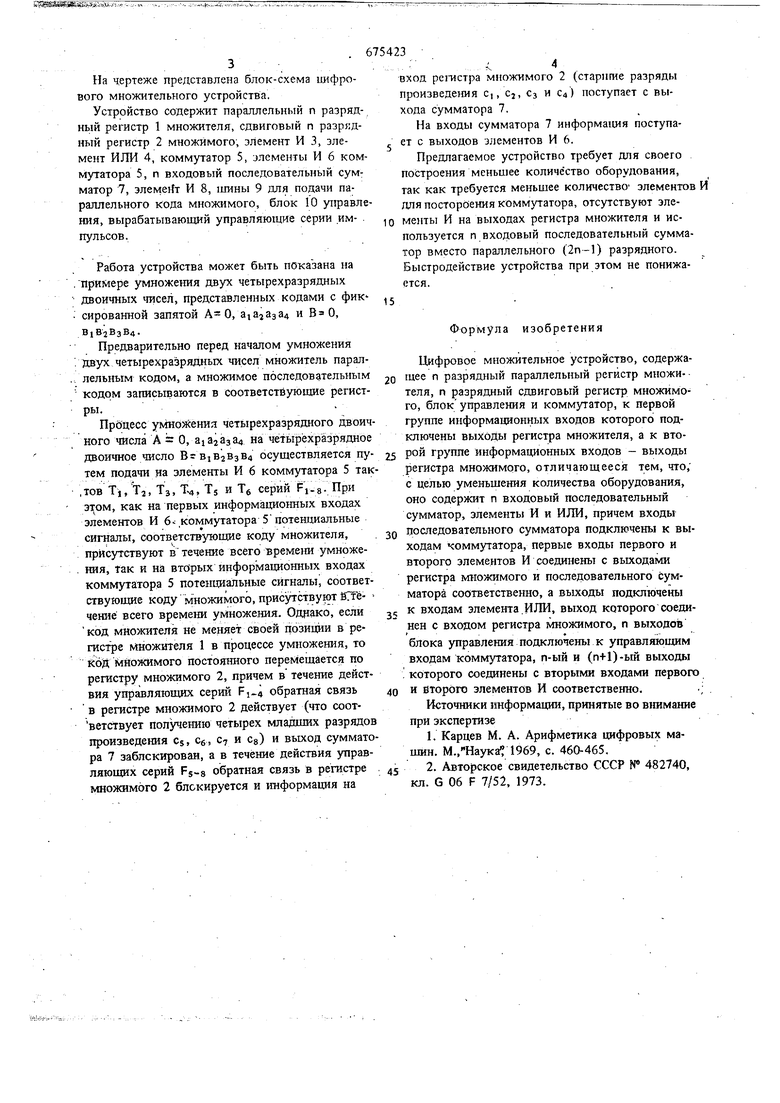

На чертеже представлена блок-схема икфрового множительного устройства.

Устройство содержит параллельный п разрядный регистр 1 множителя, сдвиговый п разркдный регистр 2 множимого, элемент И 3, элемент ИЛИ 4, коммутатор 5, элементы И 6 коммутатора 5, п входовый последовательный сумматор 7, элемент И 8, шины 9 для подачи параллельного кода множимого, блок 10 управления, вырабатывающий управляющие серии импульсов.

Работа устройства может быть показана на /примере умножения двух четырехразрядных

двоичных чисел, представленных кодами с фик . сированной запятой , а1а2аза4 и ,

В1В2ВзВ4Предварительно перед началом умножения .двух четырехразрядных чисел множитель парал. лельным кодом, а множимое последовательным кодом записываются в соответствующие регистры.

ПрЬ;цесс умножения четырехразрядного двоичного числа А О, aiajasai на четырёхразрядное двоичное число BcBjB2B3B4 осуществляется путем подачи на элементы И 6 коммутатора 5 так,тов TI, tj, Тз, Т.4, TS и Тб серий F1-8. При , как на первых информационных входах элементов И 6с коммутатора 5потенциальные сигналы, соответствующие коду множителя, присутствуют втечение всего времени умноже. ния, так и на вторых )ормационных входах коммутатора 5 потенциальные сигналы, соответствующие коду множимого, присутствуют Ое- чение всего времени умножения. Одрако, если код множителя не меняет своей позиции в регистре множителя 1 в процессе умножения, то код множимого постоянного перемещается по регистру множимого 2, причем в течение действия управляющих серий обратная связь в регистре множимого 2 действует (что соответствует получеюно четырех младщих разрядов произведения Cs, Cg, с и Св) и выход сумматора 7 забпскирован, а в течение действия управляющих серий FS-S обратная связь в регистре множимого 2 блокируется и информация на

вход решстра множимого 2 (старпгие разряды произведения С|, Cj, Сз и с) поступает с выхода сумматора 7.

На входы сумматора 7 информация поступает с выходов элементов И 6.

Предлагаемое устройство требует для своего построения меньшее количество оборудования, так как требуется меньщее количество элементов И для посторбения коммутатора, отсутствуют злеме}1ты И на выходах регистра множителя и используется п входовый последовательный сумматор вместо параллельного (2п-1) разрядного. Быстродействие устройства при этом не понижается.

Формула изобретения

Цифровое множительное устройство, содержаtuee п разрядный параллельный регистр множи- теля, п разрядный сдвиговый регистр множимого, блок управления и коммутатор, к первой группе информационных входов которого подключены выходы регистра множителя, а к второй группе информационных входов - выходы регистра множимого, отличающееся тем, что; с целью уменьшения количества оборудования, оно содержит п входовый последовательный сумматор, элементы И и И.ПИ, причем входы

последовательного сумматора подключены к выходам коммутатора, первые входы первого и второго элементов И соединены с выходами регистра множимого и последовательного сумматора соответственно, а выходы подключены

к входам элемента ИЛИ, выход которого соединен с входом регистра множимого, п выходов блока управления подключены к управляющим входам коммутатора, п-ый и (п+1)-ый выходы которого соеданены с вторыми входами первого

и второго элементов И соответственно..;

Источники информации, принятые во В1шмание при экспертизе

1. Карцев М. А. Арифметика цифровых мащин. М.,Наука 1969, с. 460-465.

2. Авторское свидетельство СССР N 482740, кл. G 06 F 7/52, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Множительно-сдвиговое устройство | 1982 |

|

SU1013951A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

Авторы

Даты

1979-07-25—Публикация

1977-07-05—Подача