00

ш

СП

Изобретение относится к .вычислительной технике, в частности преназначено для выполнения операций умножения и- сдвига в быстродействующих цифровых вычислительных машинах. .

Известно множительно-сдвиговое устройство, содержащее генератор произведений, преобразователь константы сдвига в параллельный однопозиционный код, сумматоры множительного устройства, регистр множителя. Оно выполняет операции умножения и сдвига на п разрядов tl Недостатком такого устройства является малое быстродействие.

Наиболее близким к изобретению по технической сущности является множительно-сдвиговое устройство, содержащее блок последовательно-параллельного умножения с параллельной обработкой п-разрядных групп множимого и т-разрядных групп множителя, счетчик тактов, генератор кратных множимых, преобразователь двоичного кода константы сдвига в однопозициоиный код регистра множителя, схему суммирования частичных произведений. Оно производит выполнение операций умножения и сдвига с требуемым быстродействием 2 .

Недостатком известного устройства является пониженная надежность вследствие низкой степени унификации из-за наличия повыиленной номенклатуры элементов схемы преобразования константы сдвига в однопозиционный Код; сложности схемной реализации из-за большого числа элементов, и связей по тракту формирования однопоз {ционного кода.

Целью изобретения является повышение надежности за счет увеличения степени унификации устройства и упрощение схемной реализации при одновременном сохранении быстродействия., Поставленная цель достигается тем, что множительное-сдвиговое устройство, содержащее блок последовательно-параллельного умножения, коммутатор множимого и счетчик, причем первая группа входов коммутатора множимого подключена к группе входов ввода множимого /устройства, выходы коммутатора множимого подключены ко входам блока последовательно-параллельного умножения соответственно, группа выходов которого подключена- к группе выходов устройства, содержит постоянный запоминающий элемент, первая группа адресных входов которого подключена ко входам ввода кода константы устройства соответственно, вторая группа адресных входов постоянногр запоминающего элемента подключена к вьтходам счетчика соответственно, счетный вход которого соединен с управляющим входом устройства, группа выходов постоянного запоминающего элемента подключена ко второй группе входов коммутатора множимого.

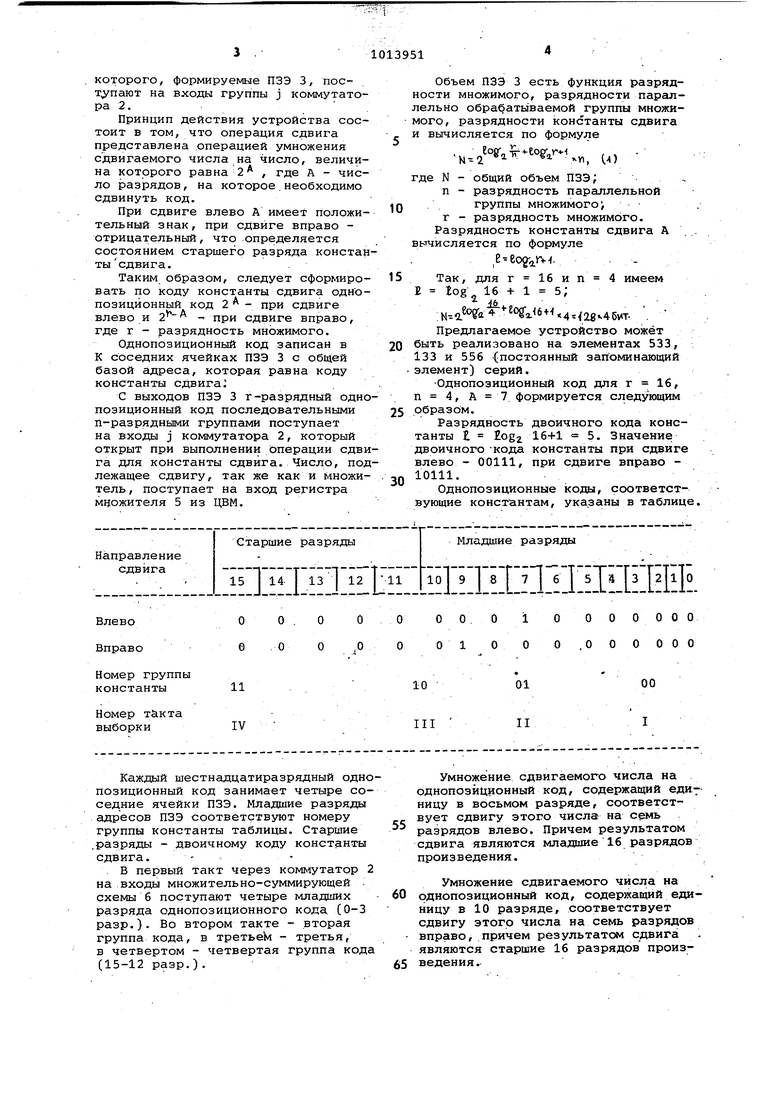

На чертеже изображена схема множительно-сдвигового устройства.

Устройство содержит блок 1 последовательно-параллельного умножения с параллельной обработкой п-разрядных последовательных групп множимого и т-разрядных параллельных групп q-разрядного множителя, коммутатор множимого 2f постоянный запоминающий элемент 3 ГПЗЭ) и счетчик 4, представляющий собой стандартный комбинационный элемент со счетным входом. Блок 1 последовательно-параллельного умножения состоит из регистра 5. множителя, построенного по последовательно-параллельному принципу, и последовательнпараллельной множительно-суммирующей схемы б.

Сдвигаемое число хранится в регистре множителя 5 в виде двоичного q-разрядного кода, на выходах регисра формируется параллельный т-разрядный код, поступающий на входы д, множительно-суммирующей схемы 6, на группу входов с этой же схемы поданы выходы коммутатора 2. На входь1 i группы коммутатора 2 поступают последовательные п-разрядные группы множимого на входы группы j - п-разрядные последовательные . группы однопозиционного кода с выхода постоянного запоминающего элемента (ПЗЭ) 3.

Постоянный запоминающий элемент 3 представляет собой модуль ПЗУ и имеет группы адресных входов а, b и одну группу выходов.

На первую группу адресных входов а поступает параллельный -разрядный код константы сдвига из устройства управления ЦВМ. На вторую группу входов b поступает параллельный К-разрядный код номера группы однопозицчонного кода с выхода счетчика 4. Наличие номера группы обусловлено принципом действия устройства в целом, т.е. необходимостью преобразования кода множимого в последовательные п-разрядные группы.

Так, при разрядности множимого, равной: 16, и п 4,. количество групп равно 4, а К 2, т.е. счетчик может быть двухразрядным. На счетный вход СК-счетчика 4. поступает сигнал +1 из устройства управления ЦВМ.

Назначение ПЗЭ 3 - преобразование константы сдвига в однопозиционный код, последовательные группы

которого, формируемые ПЗЭ 3, поступают на входы группы j коммутатора 2.

Принцип действия устройства состоит в том, что операция сдвига представлена операцией умножения сдвигаемого числа на число, величина которого равна 2 , где А - число разрядов, на которое.необходимо сдвинуть код.

При сдвиге влево А имеет положительный знак, при сдвиге вправо отрицательный, что определяется состоянием старшего разряда константы сдвига.

Таким образом, следует сформировать по коду константы сдвига однопозиционный код 2 - при сдвиге влево и 2 -при сдвиге вправо, где г - разрядность множимого.

Однопозиционный код записан в К соседних ячейках ПЗЭ 3 с общей базой адреса, которая равна коду константы сдвига:.

С выходов ПЗЭ 3 г-разрядный однопозиционный код последовательными п-разрядными группами поступает на входы j коммутатора 2, который открыт при выполнении операции сдвига для константы сдвига. Число, подлежащее сдвигу, так же как и множитель, поступает на вход регистра множителя 5 из ЦВМ.

Объем ПЗЭ 3 есть функция разрядности множимого, разрядности парашлельно обрабатываемой группы множимого, разрядности константы сдвига и вычисляется по формуле

.,...,, t,, где N - общий объем ПЗЭ;

п - разрядность параллельной

группы множимого; г - разрядность множимого. Разрядность константы сдвига А вычисляется по формуле

,Eeog-,(. . Так, для имеем Е tog 16 + 1 5;

;N--a4a 6H,4,2ev46v.T. .

Предлагаемое устройство может быть реализовано на элементах 533, 133 и 556 -(постоянный запоминающий .злемент) серий.

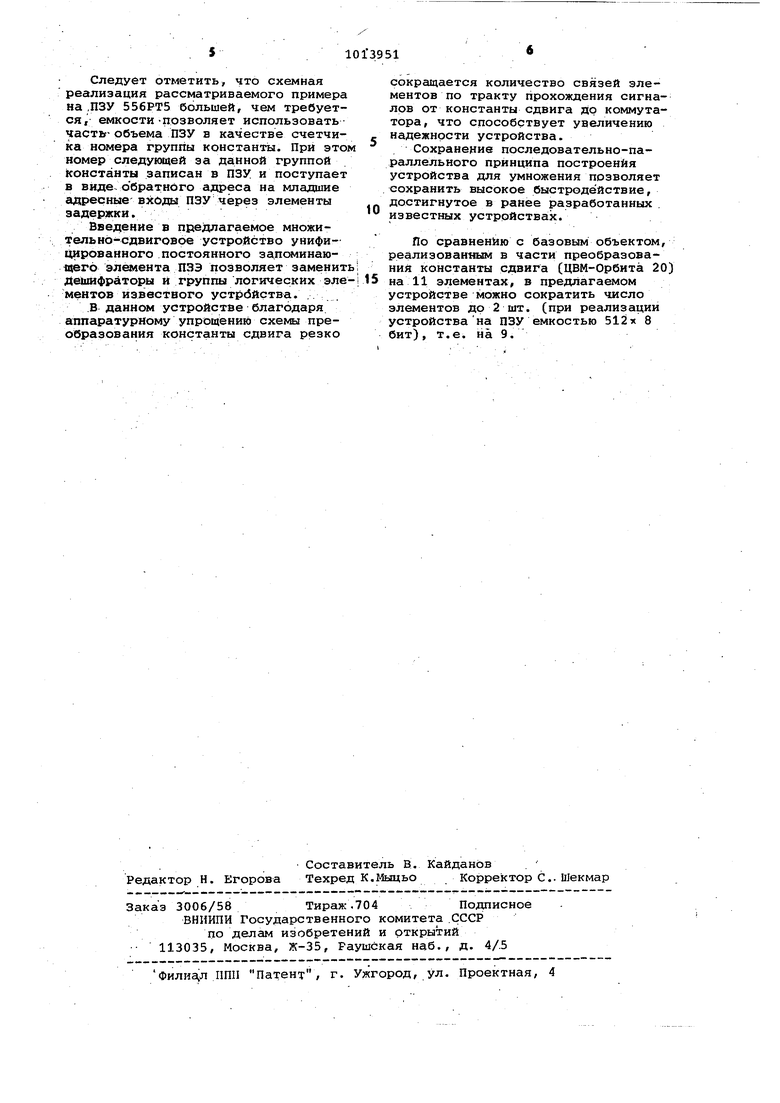

Однопозиционный код для г 16, п 4, А 7. формируется следующим образом.

Разрядность двоичного кода константы og2. 16+1 5. Значение двоичного -кода константы при сдвиг влево - 00111, при сдвиге вправо 10111.

Однопозиционные коды, соответствующие константам, указаны в таблиц

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Множительное устройство | 1978 |

|

SU752335A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Цифровое множительное устройство | 1977 |

|

SU675423A1 |

| Устройство для умножения | 1976 |

|

SU583433A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

МНОЖИТЕЛЬНб-СДВЙГОВОЕ УСТРОЙСТВО, содержащее блок последовательно-параллельного умножения, коммутатор множимого и счетчик, причем первая группу входов кою4утатора множимого подключена к группе входов ввода, множимого устройства, выходам коммутатора множимого подключены к входам блока последовательно-параллельного умножения соответственно, группа выходов которого подключена i к группе выходов устройства о т-л и ч а: ю ц е е с я тем, что, с целью повьааения надежности и упро- : щения, устройство содержит постоянный запомингиощий элемент, первая группа адресных входов подключена к входам ввода кода константы устройства соответственно, вторая группа адресных входов постоянного запоминакяцего элемента подклю-: чена к выходам счетчика соответственно, счетный вход которого соединен . с управляющим входом устройства, : группа выходов постоянного запоминающего элемента подключена к втоСО рой группе входов коммутатора множимого . с

Номер группы константы 11

Номер т&кта выборки IV

Каждый шестнадцатиразрядный однопозиционный код занимает четыре соседние ячейки ПЗЭ. Младшие разряды адресов ПЗЭ соответствуют номеру группы константы таблицы. Старшие .разряды - двоичному коду константы сдвига.

. В первый такт через коммутатор 2 на входы множительно-суммирующей . схемы 6 поступают четыре младших разряда однопозиционного кода (0-3 разр.). Во втором такте - вторая группа кода, в третьей - третья, в четвертом - четвертая группа кода (15-12 разр.),

00 I

01

II

Умножение сдвигаемого числа на ОДНОПОЗИЦИОННЫЙ код, содержащий единицу в восьмом разряде, соответствует сдвигу этого числа на семь разрядов влево. Причем результатом сдвига являются младшие 16 разрядов произведения.

Умножение сдвигаемого числа на ОДНОПОЗИЦИОННЫЙ код, содержащий единицу в 10 разряде, соответствует сдвигу этого числа на семь разрядов вправо, причем результатом сдвига

являются старшие 16 разрядов произведения.

Следует отметить, что схемная реализация рассматриваемого примера на ,ПЗУ 556РТ5 большей, чем требуется, емкости-позволяет использовать объема ПЗУ в качестве счетчика номера группы константы. При это номер следующей за данной группой константы записан в ПЗУ и поступает в виде обратного адреса на младшие адресные входы ПЗУ через элементы задержки.

Введение в предлагаемое множительно-сдвиговое устройство унифицированного постоянного задоминающего элемента ПЗЭ позволяет заменит Дешифраторы и группы логических элементов известного устС)5йства. .

В данном устройстве благодаря аппаратурному упрощению схемы преобразования константы сдвига резко

сокращается количество связей элементов по тракту прохождения сигналов от константы сдвига до коммутатора, что способствует увеличению надежности устройства.

Сохранение последовательно-параллельного принципа построения устройства для умножения позволяет сохранить высокое быстродействие, достигнутое в ранее разработанных известных устройствах.

По сравнению с базовым объектом, реализованным в части преобразования константы сдвига (ЦВМ-Орбита 20) на 11 элементах, в предлагаемом устройстве можно сократить число элементов до 2 шт. (при реализации устройствана ПЗУ емкостью 512х 8 бит), т.е. на 9.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-23—Публикация

1982-01-06—Подача