(54) МНОЖИТЕЛЬНО-СДВИГОВОЕ, УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-сдвиговое устройство | 1982 |

|

SU1013951A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для умножения | 1979 |

|

SU817701A1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Устройство для умножения | 1976 |

|

SU583433A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения двоичных чисел | 1985 |

|

SU1260948A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

Изобретение предназначено для ислользования в вычислительной технике, в частности для выполнения операций умножения и сдвига в цифроввлх вычис лительных машинах (ЦВМ) и устройствах автоматики.

В настоящее время в перспективных разработках находят применение последовательно-параллельные ЦВМ, имеющие компромиссное решение между малогабаритными со средним быстродействием ЦВМ последовательного типа и быстродействующими, но со значительными затратами ЦВМ параллельного типа.

Известно устройство, которое относится к числу устройств умножения последовательно-11араллельного типа с параллельной обработкой п разрядов множимого и т. разрядов множителя и содержит генератор кратнЕлх множимых, регистр множителя, коммутатор частны. произведений и последовательнопараллельную схему суммирования с элементами задержки. Это устройство обеспечивает быстродействие выполнения операций умножения,, достаточное для последовательно-параллельных машин с параллельной обработкой пгразрядных групп операндов 1.

Недостаток устройства - невозможность выполнения операций сдвига кодов .

Наиболее близким к предлагаемому техническому решению является устройство, содержащее сумматор, регистр множителя, генератор произведений и преобразователь константы сдвига в

параллельный однопозиционный код, вход которого соединён с выходом адресной части регистра команд основного арифметического устройства (т.е. с шиной двоичной константы сдвига), а выход - со входом генератора произведений. В этом устройстве все младшие разряды константы сдвига, кроме старшего знакового и разрядов, определякядих вид сдвига (арифметический или логический), подаются на

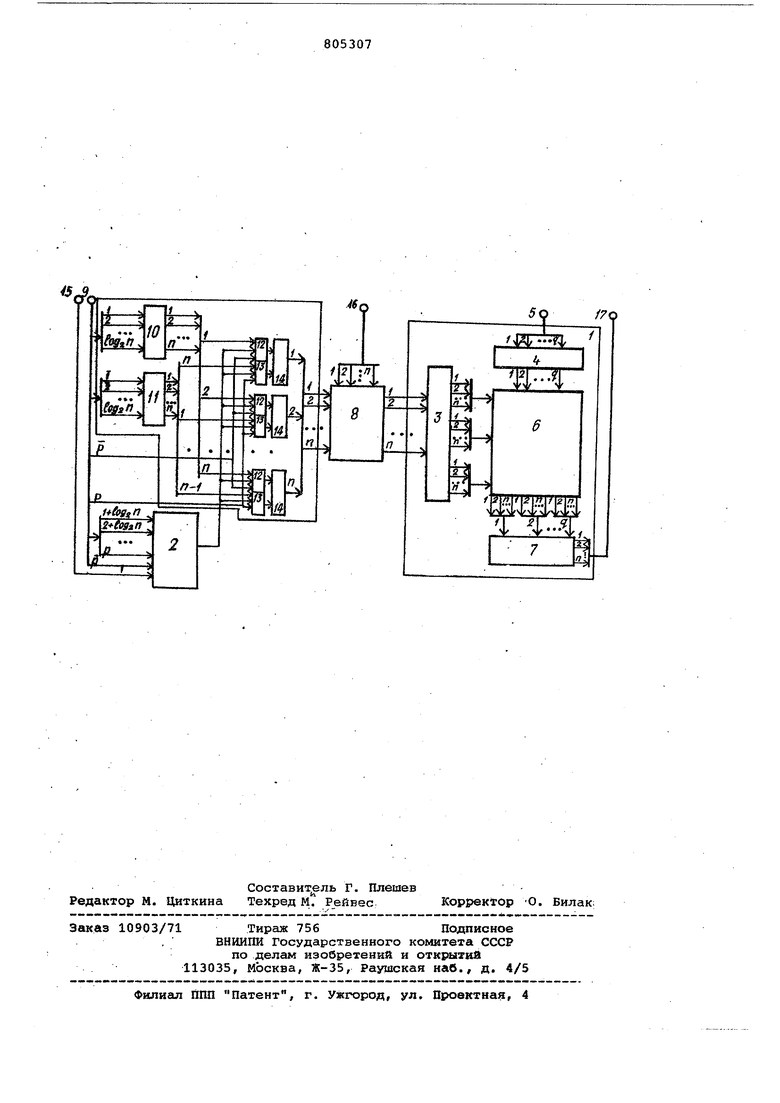

вход преобразователя двоичной константы сдвига, преобразующего двоичный код константы сдвига в параллельный однопозиционный код. Таким обра-зом, на выходе преобразователя выдается код в виде нулей с единицей в К-ом разряде при сдвиге влево или единицей в 15-К-ом разряде при сдви.ге вправо, который подается в качестве множимого на вход последовательно-параллельного множительного устройства, которое реализует операцию сдвига аналогично операции умножения полноразрядного множимого, так как выход преобразователя константы сдви га подключен к соответствующему вход генератора произведений, т.е. конста та сдвига является полноразрядным мн жимым, а сдвигаемое число в этом слу чае следует по каналам множителя 2 Недостатком этого устройства являются значительные аппаратурные затраты, связанные с невозможностью группировки разрядов параллельнбго однопозиционного кода преобразованной константы сдвига для их дальнейшей последовательной обработки в схе ме для умножения группами по п разрядов (где п 2,3,4... 2- числа натурального ряда от 2 до Е , а В - полная разрядность константы сдвига, т.е. множимого). Цель изобретения - сокращение апп ратурных затрат, связанных с проведе нием операций сдвига и умножения, а также обеспечение простоты и универсальности оборудования. Указанная цель достигается тем, что множительно-сдвиговое устройство, содержащее преобразователь двоич ного кода константы сдвига в однопозиционный код, блок последовательнопараллельного умножения, выход которого является выходом устройства, содержит коммутатор множимого и счет чик тактов, при этом Лервая группа входов коммутатора множимого соединена с группой выходов преобразовате ля двоичного кода константы, сдвига в сэднопозиционный код, а вторая - с шиной множимого,первая группа входов преобразователя константы сдвига в одн позиционный код соединена с группой выходов счетчика тактов, соединенног своими входами с шиной старших разрядов двои 1ного кода константы сдвига в однопозиционный код и тактовой шиной устройства, вторая группа входов преобразователя двоичного кода константы сдвига в однопозиционный код соединена с шиной младших и стар шего разрядов кода константь сдвига, группа входов множителя блока последовательно-параллельного умножения соединена с шиной множителя устройства, а группа входов множимого - с группой выходов коммутатора множимого . При этом для достижения поставленной цели преобразователь двоичног кода константы сдвига в однопозицион ный код содержит первый и второй дешифраторы, первую и группы элементов И, группу элементов ИЛИ, выход которых являются группой выходов пре образователя, а входы каждого элемен та ИЛИ соединены с выходами соответствуквдих ему элементов И первой и второй групп, первьае входы элементов И первой и второй групп соединены соответственно с выходами первого и второго дешифраторов, вторые - с шиной инверсного и прямого значений старшего.разряда кода константы сдвига, третьи входы соединены с первой группой входов преобразователя, а входы дешифраторов и шины прямого и инверсного значений старшего разряда кода константы сдвига соединены со второй группой входов преобразовател 1. На чертеже схематически представлено устройство. Оно содержит блок 1 последовательно-параллельного умножения с параллельной обработкой п-разрядных групп множимого и (п-разрядных групп множителя, счетчик 2 тактов, преобразующий старшую часть двоичного кода константы сдвига с (1+2og2,n )-ого по Р-ый разряды в последовательный однопозиционый код/ генератор 3 кратных множимого, формирующий из последовательно-параллельного кода множимого-М ряд чисел типа также последовательно-параллельно группа за группой по п разрядов в каждой, где К - числа натурального ряда от 1 до () , т - разрядность параллельно обрабатываемой группы мнохсителя, параллельный q-разрядный регистр 4 множителя, хранящий множитель или число, подлежащее сдвигу при умножении и сдвигу в течение всего времени выполнения операции, q-разрядную входную шину 5, обеспечивавядую прием кода множителя в регистр 4 при умножении или сдвигаемого числа при сдвиге; KOMMyfaTOp 6 частичных произведений, формирующий -3. частичных произведений.в последовательнопараллельном виде каждое; схему 7 суммирования частичных произведений,, обеспечивающую суммирование частичных произведений, каждое со своим весом в последовательно-параллельном виде и формирующую на своих выходах результат операции умножения или сдвига; п-разрядйый двухвходовой коммутатор 8 множимого, обеспечивающий кол утацию МНОЖИМОГО или преобразованной константы сдвига при операциях умножения или сдвига соответственно на входах гевератора 3 кратных множимого; входную щину 9 двоичиой константы сдай-га, обеспечиваесэдую параллельный прием в устройство и инверсных значений Р-разрядного кода двоичной константы сдвига , первый дешифратор 10, преобразующий младшую часть прямого кода шииы 9 с первого по разряды в одиопозиционный параллельный код; второй д ифратор 11, преоб-. раэуквдий младшую часть обратного кода шины 9 с первого по log/j, п-ый разряды Е однопоэициониый параллельный код; группу 12 элементов И, группу 13 элементов И, группу 14 элементов ИЛИ, состоящие из п элементов каждая, формирующие на п вьгходах элементов ИЛ константу сдвига, следующую последовательно группа за группой по п разрядов в каждой группе; тактовую шину 15, обеспечивающую прием тактирующих кодов устройства; входную шину 16 множимого, обеспечивающую прием кода множимого при операции умножения; выход 17 устройства представляю щий шину г по которой выдается код пр изведения; преобразователь двоичного кода константы сдвига в однопозиционный код. Принцип действия устройства состоит в том, что операция сдвига представляет собой умножение сдвигае мого числа на число величиной , где К - число разрядов, на которое необходимо сдвинуть код. При сдвиге влево К имеет положительный знак, а при сдвиге вправо - отрицательйый что определяется состоянием старшего разряда Р двоичной константы сдвига Таким образом, для выполнения сдвига путем умножения ка константу требуется преобразование последней в однопозиционный код при сдвиге влево и 2 при сдвиге вправо, т.е. &-разрядный код с нулями во всех разрядах кроме К-го при сдви ге влево или {2-к)-ого при сдвиге вправо, где 2 - полная разрядность множимого, К - величина сдвига. При параллельной передаче п разрядов в одном такте передаются сразу п разрядов , и необходимо определить две величины - номер разряда, равного единице, внутри группы и номер группы, внутри которой находится этот разряд. Для определения номера разряда внутри п -разрядной группы необходим и достаточно определить младших разрядов двоичного кода константы, рричем эта функция реализуется дешифрацией бодд п-разрядного двоичного кода. Для этого и введены в устройство первый и второй дешифраторы 10 и 11 соответственно. Номер группы, старшей по весу, определяется с помощью )старших разрядов двоичной константы. Номер группы представляет собой временной такт, соответствующий моменту прохождения через логические элементы 12,13..,14 той п-разрядной группы, в которо имеется разряд, равнйй единице. Это не что иное как. последовательный код разрядностью с нулями во всех разрядах кроме одно го, соответствукяцего номеру группы, один из разрядов, равный единице, т.е. константа сдвига с раз рядностью . Разрядность двоичного кода такой константы определитс как 2од(1), eog, - , где ( Р-1 )-разрядность исходной двоичной константы сдвига беу старшего разряда Р, управляющего направлением сдвига вправо или влево, а од. о - группа разрядов исходной двоичной константы, используемая в дешифраторах 10 и 11 для определения номера разряда,равного единице, внутри п-разрядной группы. Из вида однопозиционной константы сдвига, разбитой на - групп в соответствии с нумерацией этих групп г ё 0,1,...,( - - 1 )j и разрядов о, 1, . . . , (6 -1) , следует , что номер п-разрядной группы, в которой должен располагаться разряд, равный единице, определяется целой частью соотнсяиенийI- I IK |- для сдвига влево, j| |В-к|- для сдвига вправо, т.е.. определение номера этой группы сводится к преобразованию двокчного кода в последовательный однопозиционный вида для сдвига влево и для сдвига вправо. Для такого преобразования необходима и достаточна старшая- часть двоичного кода константы сдвига, от ()-го по (Р-1) разряд. При этом учет Р-го разряда и его инверсии определяет выбор 2 или 2 , т.е. направление сдвига. В соответствии с описанным выше принципом, счётчиХ 2 тактов формирует среди последовательности выдаваемых им нулей сигнал, равный единице, в момент времени, соответствую1ДИЙ- прохождению через п логических , элементов ИЛИ очередной параллельной группы разрядов константы, среди которых должен быть разряд, равный единице. Выбор разряда, равного единице, внутри п-разрядной группы определяется состоянием, равным единице, одного из выходов первого дешифратора 10 для первой группы 12 элементов И и второго дешифратора 11 для второй группы 13 элементов И. Выбор второй или первой группы элементов И, т.е. направление сдвига вправо или влево, определяется состоянием старшего разряда Р и его инверсии Р на входах элементов И 13 и 12. Таким образом, в результате преобразования с выходов группы 14 элементов ИЛИ снимается последовательнопараллельный код константы сдвига Труппами по п разряэдов в каждом такте. Для дальнейшего выполнения операции сдвига необходимо в схеме 1 для умножения перемножить сдвигаемое чиспо на константу сдвига, для этого . указанные числа обрабатываются как полноправные, сомножители. . Число, подлежащее сдвигу, так .же как и множитель, поступает по входной шине 5 множителя в регистр 4 мно жителя параллельно и остается в нем до конца операции. Последовательно-параллельная константа сдвига поступает с выходов ,группы 14 логических элементов ИЛИ через коммутатор 8 множимого, открытый при выполнении операции сдвига для константы сдвига, на входы генератора 3 кратных множимого. Генератор 3 кратных множимого формирует по ный ряд чисел, крат.ных исходной унитарной константе сдвига с кратностью от О до 2 - 1 - и представленных последовательно-параллельным кодом, где m - разрядность группы множителя Кратные множимому т.е. константе сдв га, последовательно-параллельные чис ла побтупают на вход коммутатора 6 частичных произведений, который пропускает на каждую п-разрядную группу своих выходов число, кратность которого определяется соответствующей группой разрядов множителя, т.е. сдвигаемого числа, таким образом, на Группах выходов коммутатора 6 частич ных произведений одновременно формируются последовательно-параллельные коды частичных произведений множимого насоответствующие группы разрядов множителя. Блок 7 суммирования производит сложение частичных произведений с учетом их весов, определяемых весом соответствующих групп множителя. С выходов блока 7 суммирования полное произведение, являющееся сдви нутым исходным числом, последователь HQ-параллельным кодом поступает на выходную п-разрядную шину 17 результата. Для , разрядность двоичного кода константы Р знаковый а 4 + 1 5-(1) Значение двоичного кода константы знаковый старшие младшие О 01 11 (2) сдвиг11 (3) вправо

Математическое значение преобразованной константы для сдвига влево ,;

№ разр. , - - . 15 14 13 12 .11 10 9 8 7 б 5 4 3 2 10 (4) : значение

15 34 13 12 -11iO 9 8 7 6 5 4 3 2 1 О

значение 0000 001 000000 Р 00 (5)

На входы, дешифратора 10 поступает прямой код fog-n og 4 2

т.е. исходной математической константе сдвига вправо - 0000 0010 0000 0000.

Для исходных данных q а 8, К 3, m п 2 код сдвигаемого числа - 00001001, значение константы сдвига определяется как 000001000.

Аналогично вышеприведенному в последовательно-параллельном виде: млсгдших разрядов, т.е. код 11/ на входы дешифратора 11 поступают инверсные значения, т.е. код 00. Таким образом, в течение всего преобразования на 4-м выходе дешифратора 10 и 1-ом выходе дешифратора 11 будет логическая единица, на остальных - нули. В преобразователь 2 поступает комбинация разрядов двоичного кода константы от () (l+eog.ji) 3 до Р 5, т.е. код 0.01 для сдвига влево, а 1.01 для сдвига вправо ; к Ж.1 g. , что соответствует присутствию логической единицы во втором и третьем тактах для сдвига влево и вправо соответственно. В результате по первой группе элементов И подготовлен выход четвертого элемента ИЛИ группы 14, а по второй - выход третьего элемента ИЛИ группы 14. . При сдвиге влево состояние разряда -Р кода константы сдвига определяет выбор первой группы элементов И, а логическая единица на выходе счетчика 2 возбуждает выход четвертого элемента ИЛИ группы 14 только во втором такте, что соответствует последовательно-параллельной информации на выходах элементов ИЛИ 14 вида: № такта т.е. исходной математической константе для сдвига влево - 0000 0000 1000 0000. При сдвиге вправо . . № сборки № такта

Номер такта

I И 1М IV

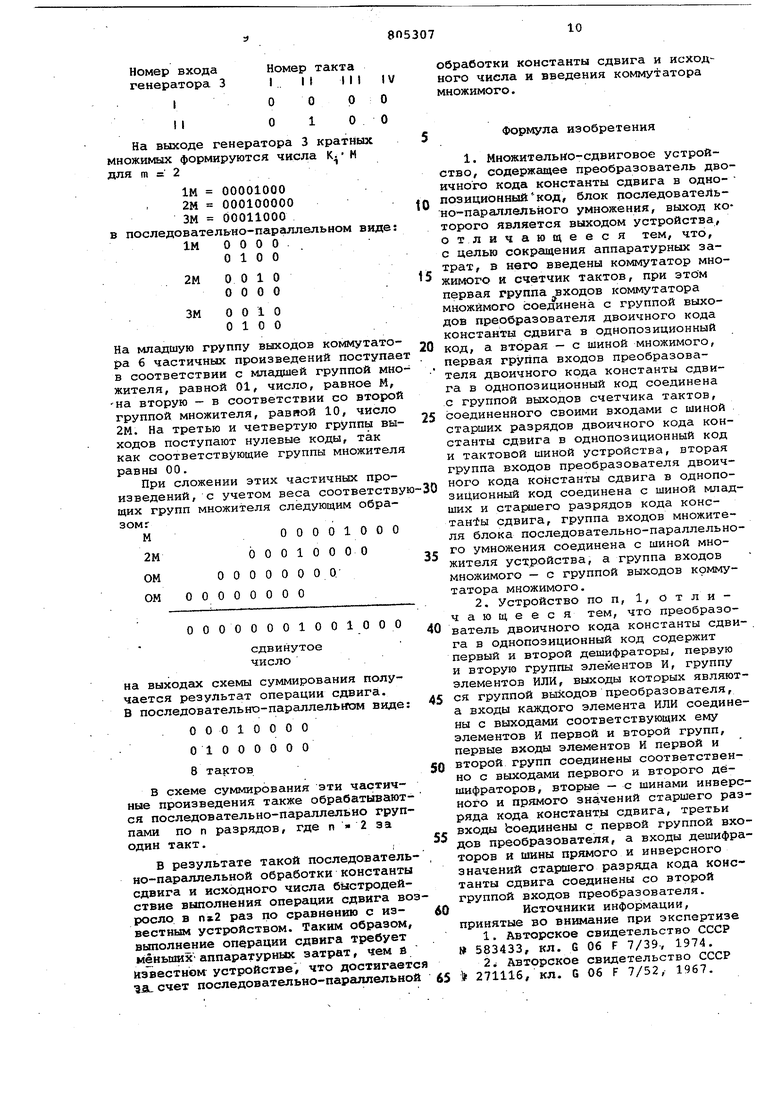

О На выходе генератора 3 кратных множимых формируются числа К- Н для m 2 Ш 00001000 2М 000100000 ЗМ 00011000 в последовательно-параллельном виде 1М 0000. 0100 0010 0000 0010 0100 На млсщшую группу выходов коммутато ра 6 частичных произведений поступа в соответствии с младшей группой мн жителя, равной 01, число, равное М, -на вторую - в соответствии со второ группой множителя, равпой 10, число 2м. На третью и четвертую группы вы ходов поступают нулевые коды, так как соответствующие группы множител равны 00. При сложении этих частичных произведений, с учетом веса соответств щих групп множителя следующим образомгМ00001000 00010000 ом 00000000 ом 00000000 00000001001000 сдвинутое число на выходах схемы суммирования получается результат операции сдвига. В последовательно-параллельном виде 00010000 01000000 8 тактов В схеме суммирования эти частичные произведения также обрабатывают ся последовательно-параллельно груп пами по п разрядов, где п 2 за один такт. В результате такой последователь но-параллельной обработки константы сдвига и исходного числа быстродействие выполнения операции сдвига во росло в раз по сравнению с известным устройством. Таким образом выполнение операции сдвига требует мёньпшх аппаратурных затрат, чем s известном устройстве, что достигает А- счет последовательно-параллельно

обработки константы сдвига и исходного числа и введения коммутатора множимого. Формула изобретения 1.Множительно-сдвиговое устройство, содержащее преобразователь двоичного кода константы сдвига в одно- позиционныйкод, блок последовательно-параллельного умножения, выход которого является выходом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены коммутатор множимого и счетчик тактов, при этом первая группа входов коммутатора множимого соединена с группой выходов преоб разователя двоичного кода константы сдвига в однопозиционный код, а вторая - с шиной множимого, первая группа входов преобразователя двоичного кода константы сдвига в однопозиционный код соединена с группой выходов счетчика тактов, соединенного своими входами с шиной старших разрядов двоичного кода константы сдвига в однопозиционный код и тактовой шиной устройства, вторая группа входов преобразователя двоичного кода константы сдвига в однопозиционный код соединена с шиной младших и старшего разрядов кода константы сдвига, группа входов множителя блока последовательно-параллельного умножения соединена с шиной множителя устройства, а группа входов множимого - с группой выходов коммутатора множимого. 2.Устройство по п, 1, отличающееся тем, что преобразователь двоичного кода константы сдвига в однопозиционный код содержит первый и второй дешифраторы, первую и вторую группы элементов И, группу элементов ИЛИ, выходы которых являются группой выходов преобразователя, а входы каждого элемента ИЛИ соединены с выходами соответствующих ему элементов и первой и второй групп, первые входы элементов И первой и второй групп соединены соответственно с выходами первого и второго дешифраторов, вторые - с шинами инверсного и прямого значений старшего разряда кода константы сдвига, третьи входаа соединены с первой группой входов преобразователя, а входы дешифраторов и шины прямого и инверсного значений старшего разряда кода константы сдвига соединены со второй группой входов преобразователя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 583433, кл. G 06 F 7/39, 1974. 2 Авторское свидетельство СССР )| 271116, кл. G Об F 7/52, 1967.

Авторы

Даты

1981-02-15—Публикация

1978-07-11—Подача