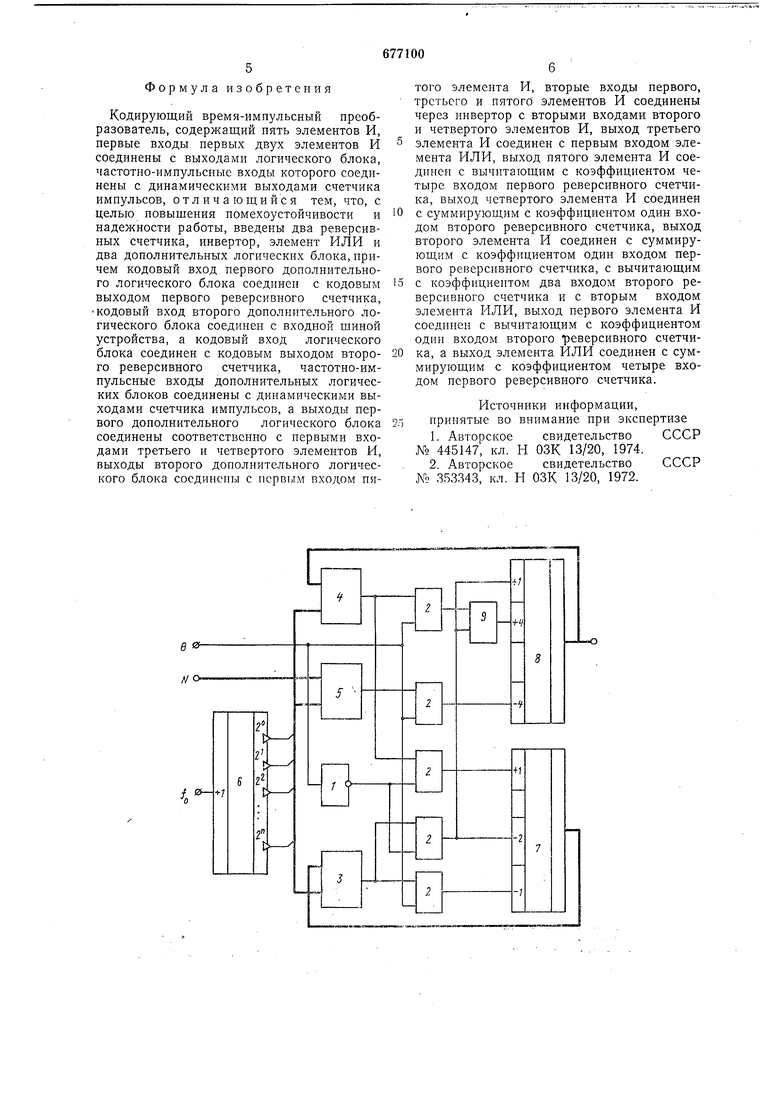

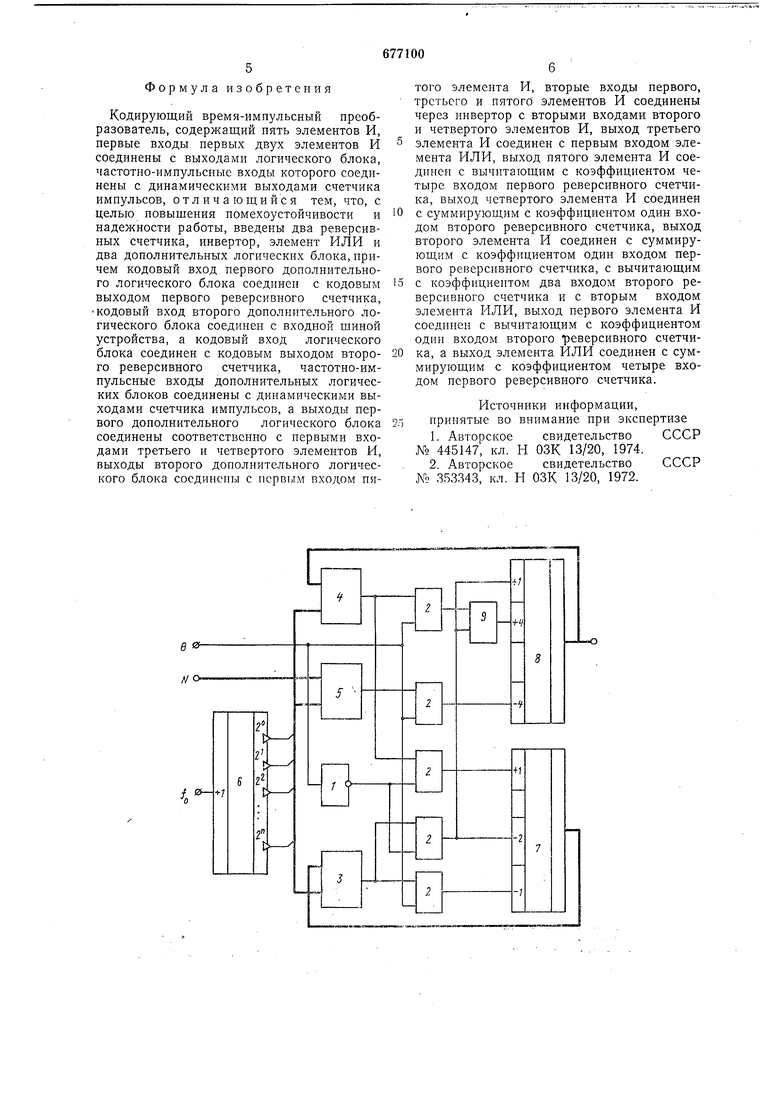

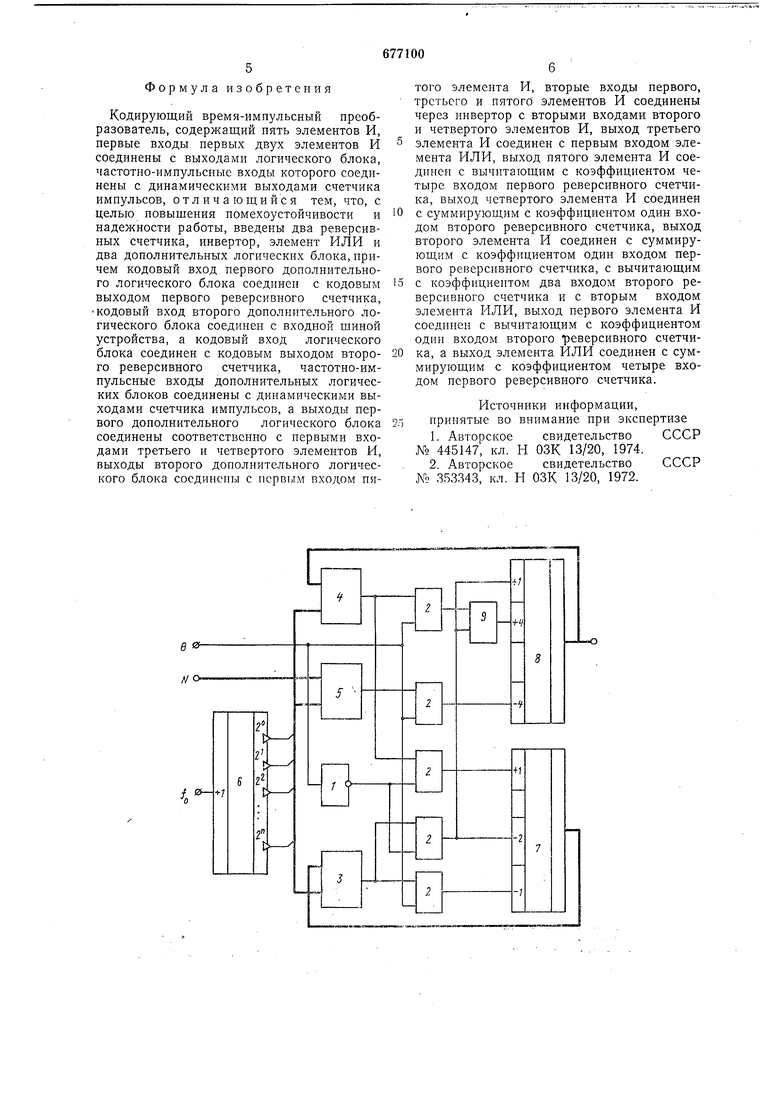

ентом один входом первого реверсивного счетчика, с вычитающим с коэффициентом два входом второго реверсивного счетчика и с вторым входом элемента ИЛИ. Выход первого элемента И подключен к вычитающему с коэффициентом один входом второго реверсивного счетчика, а выход элемента ИЛИ - к суммирующему с коэффициентом четыре входом первого реверсивного счетчика. Структурная электрическая схема устройства приведена на чертеже. Устройство содержит инвертор 1, элементы И 2, логические блоки 3, 4, 5, счетчик 6 импульсов, реверсивные счетчики 7, 8, элемент ИЛИ 9. Работает устройство следующим образом. Пусть в исходном положении все сметчики 6, 7, 8 находятся в нулевом состоянии. На входы устройства подается двоичный код Л, ШИМ-сигнал с относительной длительностью 0, а на вход счетчика подключена опорная импульсная последовательность с частотой foЛогические блоки 3, 4, 5 совместно со счетчиком 6 реализуют линейное преобразование код - частота. /лв-|ьлА,б, где /лб - среднее значение частоты на выходе логического блока; - входной управляющий код логического блока; л - разрядность счетчика и кода. Элементы И 2 осуществляют широтноимпульсную модуляцию последовательностей. Иа каждом периоде в течение интервала времени т импульсные последовательности имеют возможность проходить через первый, второй, пятый элементы И 2, а в остальную часть периода Т-т - через третий и четвертый элементы И2. Вначале начинает работать преобразователь код-частота на основе логического блока 5, так как остальные логические блоки 3 и 4 управляются нулевыми кодами NZ и ЛА с выходов реверсивных счетчиков 8 и 7 соответственно. Тогда первый импульс с выхода логического блока 5, пройдя через соответствующий элемент И 2, поступает на реверсивный счетчик 7 и делает его содержимое отличным от нуля. Благодаря этому начинается работа логического блока 4. На кодовом входе логического блока 3 ненулевое значение управляющего кода ЛА появляется после прохождения на реверсивный счетчик 7 первого же импульса с выхода логического блока 4 через третий элемент И 2 и интервал времени Таким образом, импульсные последовательности на выходах элементов И 2 описываются следзющими функциональными характеристиками. f,K-Nz. f,-K-IV-Q, J, J.N(l-e), 7,:/Г.Л/л(1-в), J, K-IVA-Q, где /С 2« Эти импульсные последовательности поступают на реверсивные счетчики 7 и 8 следучрщим образом: fi - через элемент ИЛИ 9 на вход « + счетчика 8; /2 - на вход «-4 счетчика 8; /3 - на вход «-fl счетчика 7; /4 - на вход «-f 1 и через элемент ИЛИ 9 на вход « + счетчика 8, а также на вход «-2 счетчика 7; /5 - на вход «-1 счетчика 7. В основу построения устройства положен принцип автоматической компенсации частотно-импульсных последовательностей, реализуемый с помощью отрицательной обратной связи. В качестве схемы сравнения последних, вырабатывающей сигнал рассогласования в контуре обратной связи, используется реверсивный счетчик. Он выполняет одновременно две операции: вычитание частот и интегрирование полученной разности с выдачей результата в виде двоичного кода. Здесь имеются два контура отрицательной обратной связи: местный - на основе реверсивного счетчика 7 ,и главный - на основе реверсивного счетчика 8. Условием динамического равновесия схемы является равенство приращений кодов суммирующих и вычитающих цепей в каждом реверсивном счетчике в течение периода итиротно-импульсной модуляции. Установившийся режим наступает через т периодов ШИМ-сигнала. При этом благодаря построению устройства в виде замкнутой следящей системы с отрицательной обратной связью и наличия оператора усреднения устройство помехоустойчиво к единичным помехам по ШИМ- и частотноимпульсным сигналам. В преобразователе отсутствует сложный и ненадежный в технической реализации блок опорных частот на больщое число выходов. Исключено из схемы также довольно сложное частотно-импульсное множительно-делительное устройство. Кроме того, устройство эффективно реализуется на основе среднемасщтабных цифровых интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОДИРУЮЩИЙ ВРЕМЯИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2141721C1 |

| Устройство для аппроксимации функций | 1989 |

|

SU1661789A1 |

| Широтно-импульсный преобразователь | 2018 |

|

RU2683180C1 |

| Устройство для вычисления тангенса | 1990 |

|

SU1734091A1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2006935C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 2003 |

|

RU2240652C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2041499C1 |

| Устройство для воспроизведения функций | 1977 |

|

SU703825A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1361549A1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО КОДИРОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 2003 |

|

RU2254674C2 |

Авторы

Даты

1979-07-30—Публикация

1977-05-17—Подача