Изобретение относится к вычислительной технике и может найти применение в телеметрических информационно-измерительных системах, в вычислительных управляющих комплексах.

Цель изобретения - упрощение устройства.

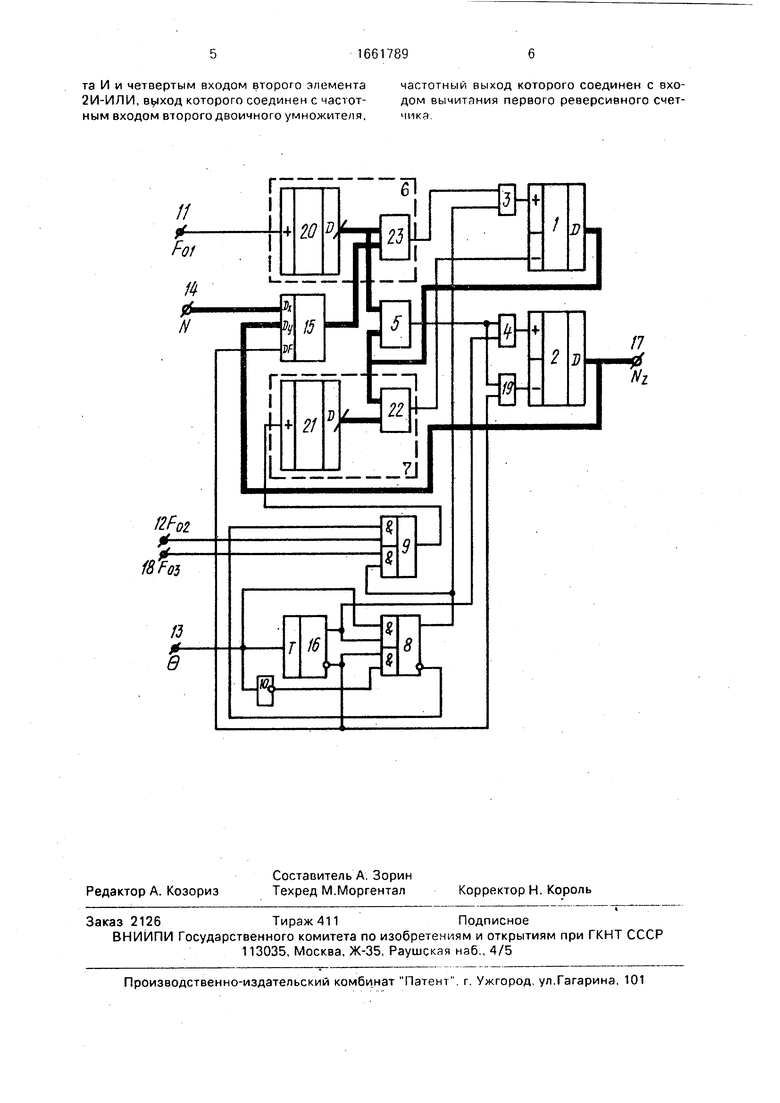

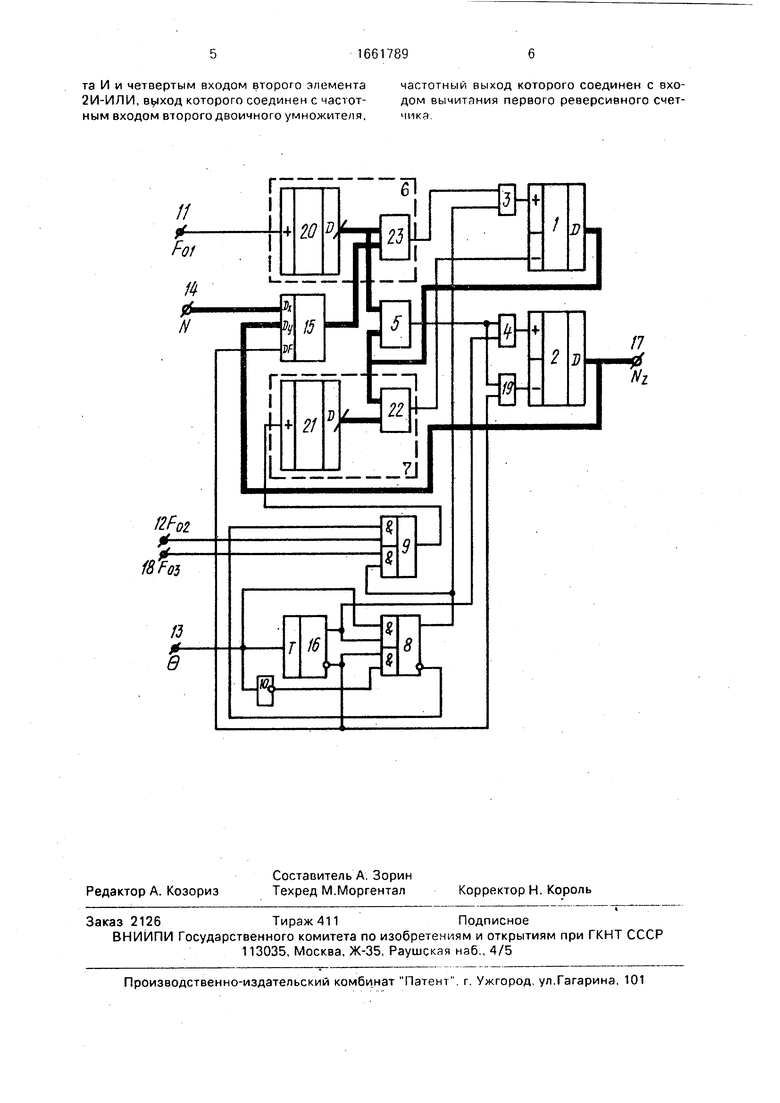

На чертеже показана блок-схема устройства.

Устройство содержит реверсивные счетчики 1 и 2, элементы И 3 и 4, блок 5 сравнения, двоичные умножители б и 7, элементы 2И-ИЛИ 8 и 9, элемент НЕ 10, входы частоты 11 и 12, вход 13 широтно-импульс- но-модулированного сигнала, кодовый вход 14, коммутатор 15, триггер 16 выход 17, вход 18 частоты, элемент И 19 Двоичные умножители содержат счетчики 20 и 21 и блоки 22 и 23 сравнения

Устройство работает следующим образом.

В исходный момент времени оба реверсивных счетчика 1 и 2 и триггер 19 находятся в нулевом состоянии, на вход 14 подается двоичный код N, на вход 13 - ШИМ-сигнал, а на входы 11,12 и 18-опорныеимпульсные последовательности FOL Fo2, Роз соответственно Блок 5 сравнения совместно с двоичным счетчиком 20 и двоичные умножители 6 и 7 осуществляют линейное преобразование кода в частоту, т.е. вырабатывают импульсные последовательности с частотами, среднее значение которых пропорционально соответствующим входным кодам

При первом периоде ШИМ-сигнала на прямом выходе триггера 16 устанавливается логическая 1, а на инверсном - логический О. На управляющий вход комON ON

00 Ч)

мутаторэ 15 подается с триггера 19 логический О, который обуславливает подачу входного кода N на вход первого двоичного умножителя 6. При этом с помощью первого элемента 2И-ИЛИ 8 на второй вход первого элемента И 3 и на вход элемента 2И-ИЛИ 9 подается ШИМ-сигнал в, а на его другой вход -8 -(1-0). Тогда на первом периоде ШИМ-сигнала первый же импульс, появившийся на выходе первого двоичного умножителя 6, в течение интервала т проходит через элемент И 3 и записывается в реверсивный счетчик 1.

Двоичный умножитель 7, имея на этом периоде опорные частоты Роз в течение интервала г, и частоту Fo2 в течение интервала Т- г, а также блок 5 сравнения начинают вырабатывать импульсные последовательности, так как управляющий ими код NI с выхода счетчика 1 стал отличен от нуля. Выходная импульсная последовательность двоичного умножителя 7 непрерывно поступает на вычитающий вход первого счетчика 1. Выходная импульсная последовательность блока 5 сравнения на этом периоде ШИМ-сигнала, непрерывно проходя через элемент И 4, поступает на суммирующий вход второго счетчика 2 и делает его содержимое отличным от нуля.

При следующем периоде ШИМ-сигнала на прямом выходе триггера 16 восстанавливается логический О, а на инверсном - логическая 1. Тогда на входах второго 4 и третьего 19 элементов И восстанавливается соответственно логические О и 1. Кроме того, на управляющем входе коммутатора 15 также восстанавливается логическая 1, которая обуславливает подачу выходного кода NZ на вход первого двоичного умножителя 6. При этом с помощью первого элемента 2И-ИЛИ 8 на второй вход первого элемента И 3 и на вход элемента 2И-ИЛИ 9 подается ШИМ-сигнал $(1- $), а на другой его вход -в.

Тогда при данном периоде ШИМ-сигнала выходные импульсы последовательности первого двоичного умножителя 6 с опорной частотой РОЧ в течение интервала (T-z) проходят через элемент И 3 и записываются в счетчик 1, который уже имеет ненулевое содержание. В этом случае двоичный умножитель 7 с опорной частотой Роз в течение интервала т и частотой Роз в интервале (Т-г) и блок 5 сравнения продолжают вырабатывать импульсные последовательности. Выходная импульсная последовательность двоичного умножителя 7 непрерывно поступает на вычитающий вход первого реверсивного счетчика 1, а выходная импульсная

последовательность блока 5 непрерывно проходит через элемент И 19 и поступает на вычитающий вход счетчика 2 При третьем периоде ШИМ-сигнала процесс происходит

так же, как и при первом периоде, а при четвертом - как при втором периоде. Далее процесс повторяется аналогично. Формула изобретения Устройство для аппроксимации функ0 ций, содержащее первый и второй двоичные умножители, блок сравнения, первый и второй реверсивные счетчики, первый и второй элементы И, первый и второй элементы 2И- ИЛИ и элемент НЕ, причем вход первой

5 частоты устройства соединен с частотным входом первого двоичного умножителя, частотный выход которого соединен с первым входом первого элемента И, выход которого соединен с суммирующим входом первого

0 реверсивного счетчика, выход которого соединен с управляющим входом второго двоичного умножителя и первым входом блока сравнения, второй вход которого соединен с выходом кода первого двоичного умножи5 теля, выход второго реверсивного счетчика соединен с выходом устройства, вход ши- ротно-импульсно-модулированного сигнала которого соединен с первым входом первого элемента 2И-ИЛИ и через элемент НЕ с

0 третьим входом первого элемента 2И-ИЛИ, отличающееся тем, что, с целью упрощения, оно содержит триггер, коммутатор и третий элемент И, причем вход шмрот- но-импульсно-модулированного сигнала

5 устройства соединен со счетным входом триггера, прямой выход которого соединен с первым входом второго элемента И и вторым входом первого элемента 2И-ИЛИ, четвертый вход которого соединен с

0 инверсным выходом триггера, управляющим входом коммутатора и первым входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента И и выходом блока сравнения, выходы

5 второго и третьего элементов И соединены с входами соответственно суммирования и вычитания второго реверсивного счетчика, инверсный выход первого элемента 2И- ИЛИ соединен с первым входом второго

0 элемента 2И-ИЛИ, второй и третий входы которого соединены с входами соответственно второй и третьей частот устройства, кодовый вход которого соединен с первым информационным входом коммутатора, вто5 рой информационный вход и выход которого соединены соответственно с выходом второго реверсивного счетчика и управляющим входом первого двоичного умножителя, прямой выход первого элемента 2И-ИЛ И соединен с вторым входом первого элемента И и четвертым входом второго элемента 2И-ИЛИ, выход которого соединен с частотным входом второго двоичного умножителя,

частотный выход которого соединен с входом вычитания первого реверсивного счет- микя

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АППРОКСИМАЦИИ ФУНКЦИЙ | 1992 |

|

RU2010324C1 |

| Широтно-импульсный преобразователь | 2018 |

|

RU2683180C1 |

| Устройство для измерения кратковременной нестабильности периода | 1990 |

|

SU1774279A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1990 |

|

SU1841066A2 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1992 |

|

RU2039953C1 |

| Устройство для воспроизведения функций | 1977 |

|

SU703825A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Функциональный широтно-импульсный преобразователь кода | 1987 |

|

SU1437882A1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Множительно-делительное устройство | 1985 |

|

SU1305677A1 |

Изобретение относится к вычислительной технике и может найти применение в телеметрических информационно-измерительных системах, в вычислительных управляющих комплексах. Целью изобретения является упрощение устройства. Устройство содержит два реверсивных счетчика, три элемента И, блок сравнения, коммутатор, два двоичных умножителя, два элемента 2 И - ИЛИ, элемент НЕ, три частотных входа, вход ШИМ-сигнала, кодовый вход, триггер. Сущность изобретения состоит в создании простого, надежного и помехоустойчивого устройства для воспроизведения функций времяимпульсного аргумента с использованием итерационного метода реализации оператора усреднения путем функционального обобщения двух местных контуров с отрицательной обратной связью за счет временного разделения процессов в цепях прямой и обратной связи главного контура с соответствующим фазированием. 1 ил.

| Смолов В.Б | |||

| Функциональные преобразователи информации | |||

| Л.: Энергоиздат, 1981, с | |||

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

| рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для воспроизведения функций | 1977 |

|

SU703825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-08-04—Подача