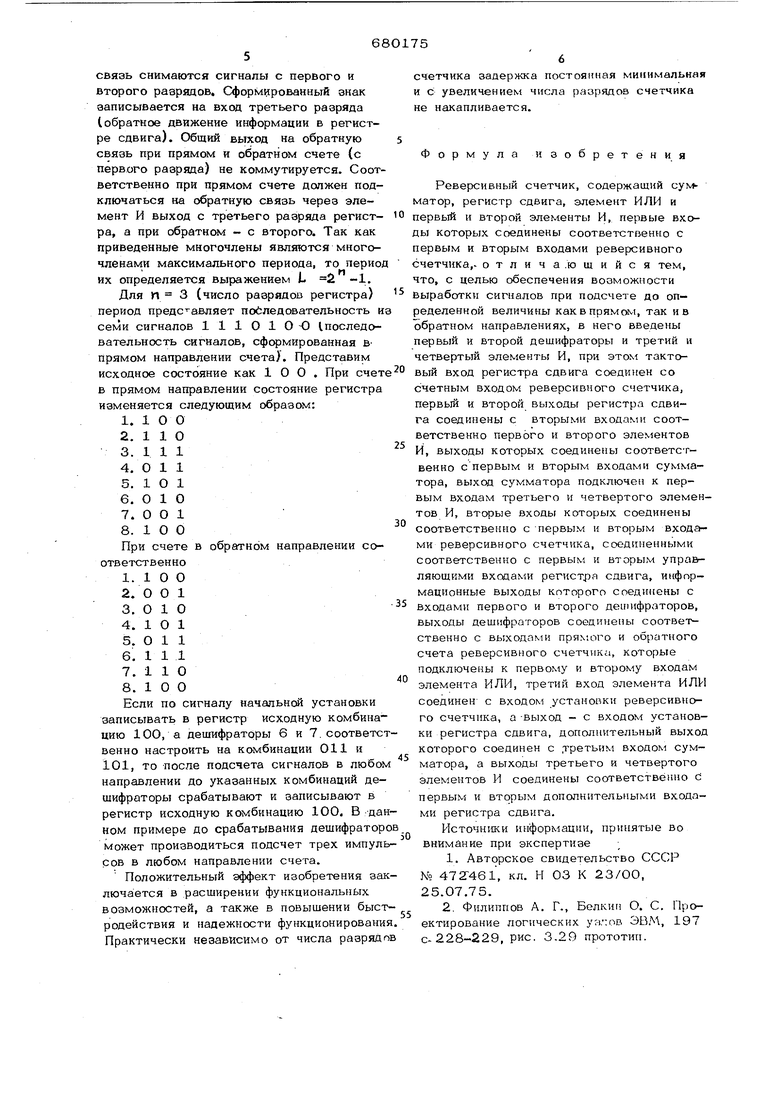

Изобретение относится к технике передачи дискретной информации, вычислительной технике и может быть применено при создании систем передачи данных. Счетчик может использоваться в анализаторах наличия передачи дискретной информации по каналам связи, з коррекционных устройствах схем автоматической подстройки такт вой частоты, при измерении параметров связи, в схемах синхронизации, а также в различных пересчетных устройствах. Известен реверсивный счетчик, содержащий дешифратор, элементы совпадения и триггеры il . Недостатком этого устройства являются ограниченные функциональные возможности при значительных аппаратурных затратах. Известен также реверсивный счетчик, содержащий сумматор, регистр сдвига, элемент ИЛИ и первый и второй элементы И, первые входы которых соединены соответственно с первым и вторым входами реверсивного счетчика 2 . В таком реверсивном счетчике отсутствует возможность выработки сигналсж при подсчете до определенной величины как в прямом, так и обратном направлениях с последующей начальной установкой счетчика. Цепью изобретения является обеспечение возможности выработтси сигналов при подсчете до определенной :Вепичины как в прямом, так и в обратном направлениях. Поставленная цель достигается тем, что в реверсивный счетчик введены первый и втсфой дешифраторы и третий и четвертый элементы И. При этом тактовый Вход регистра сдвига соединен со счетным входом реверсивного счетчика, первый и второй выходы регистра сдвига соединены с вторыми входами соответственно первого и второго элементов И, выходы которых соединены соответственно с первым и вторым Входами сумматора. Выход . сумматора подключен к ,первым входам третьего и четвертого элементов И, вторые входы которых соеди-нены соответственно с первым и вторым входами реверсивного счетчика, соединенными соответственно с первым и вторым управляющими Входами регистра сдвига. Информационные выходы регистра сдвига соединены с вхо. дами первого и второго дешифраторов, вы ходами соединенных соответственно с выходами .прямого и обратного счета реверсивного счетчика, которые подключены к первому и второму входам элемента ИЛИ Третий вход элемента ИЛИ соединен с входом установки реверсивного счетчика, его выход - с входом установки регистра сдвига, дополнительный выход которого соединен с третьим входом сумматора, Вы ходы третьего и четвертого элементов И соединены соответственно с первыми вторым дополнительными входами регистра сдвига. Структурная схема реверсивного счетчика показана на чертеже. Реверсивный счетчик содержит сумматор 1, регистр сдвига 2, элемент ИЛИ 3 элементы И 4 и 5, дешифраторы 6 и 7, элементы И 8 и 9. Первые входы элемен тов И 4 и 5 соединены соответственно с входами 10 и 11 реверсивного счетчика. Тактовый вход регистра сдвига 2 соедине со счетным входом 12 реверсивного счет чика. ПервыйИ второй выходы регистра сдвига соединены с вторыми входами соответственно элементов И 4 и 5, выходы которых подключены соответственно к пер вому и второму входам сумматора 1, выходом соединенного с первыми входами элементов И 8 и 9, Вторые входы элемен тов И 8 и 9 соединены соответственно с входами 10 и 11 реверсивного счетчика, которые подключены соответственно к пер вому и второму управляющим входам регистра сдвига. Информационные выходы последнего подк:л очены к входам дешифраторов б и 7. Выходы дешифраторов соединены соответственно с выходами прямого 13 и обратного 14 счета реверсивного счетчика, которые соединены с первым к вторым входами элемента ИЛИ 3, Третий вход элемента ИЛИ соединен с входом установки 15 реверсивного счетчика, его выход - с входом установки регистра сдвига 2, дополнительный выход которого соединен с третьим входом сумматора. Вы ходы элементов И 8 и 9 соединены соответственно с первым н вторым дополнительными входами регистра сдвига. Реверсивный счетчик работает следующнм образом. С входа 15 подают ифи необходимости сигнал начальной устагЕовки реверсивного счетчика в исходное фазовое состояние, который через элемент ИЛИ 3 поступает на вход регистра сдвига 2, Сигналом управления реверсом (направлением счета), подаваемым с входа 10 при прямом счете и с входа 11 при обратном, регистр сдвига коммутирует для счета в соответствующем направлении. Одновременно к входу сумматора 1 этим сигналом подключают соответствующие точки съема в цепи логической обратной связи через элементы И 4 и 5. Сигналы вырабатываемой рекуррент ной последовательности через элемент И 8 при прямом счете и элемент И 9 при обратном поступают на входы регистра сдвига 2, Сигналы рекуррентной последовательности вырабатываются только при наличии счетных сигналов, которые со счетного входа 12 поступают на тактовьм вход регистра сдвига. При подсчете установленного числа счетных сигналов в направлении счета срабатывает соответст вующий дешифратор - б при прямом счете и 7 при обратном. Сигналы с дешифраторов поступают соответственно на выходы 13 и 14 и через элемент ИЛИ 3 подаются на вход начальной установки регистра сдвига 2. Таким образом счетчик подготавливается к следующему циклу . работы. При необходимости в любой момент времени сигнал начальной установки можетбыть подан извне для подготовки к работе и установки реверсивного счетчика в исходное фазовое состояние. Пример принципа построения и работытакого реверсивного счетчика. Пусть закон формирования последовательности сигналов в прямом направлении задан харак;теристическим многочленом Pl.x)X +Х T-l. Тогда для счета в обратном направлении (обратный порядок выработки формируемой последовательности сигналов) должен быть применен другой, сопряженный многочлен. Причем при построении регистра точки съема на обратную связь, определяемые членами сопряженного многочлена, должны быть расположены в обратном порядке относительно точек съема, определяемых исходным многочленом. Сопряженный многочлен имеет следующий вид: F- (х) Х+ 1. . Если пронумеровать разряды регистра длева направо, то при прямом счете на обратную связь снимаются сигналы с первого и третьего разрядов. Очередной формируемый знак записывается в первый разряд. При обратном счете на обр/ггную связь снимаются сигналы с первого и второго разрядов. Сформированный знак записывается на вход третьего разряда (обратное движение информации в регистре сдвига). Общий выход на обратную связь при прямом и обратном счете (с первого разряда) не коммутируется. Соответственно при прямом счете должен подключаться на обратную связь через элемент И выход с третьего разряда регистра, а при обратном - с второго. Так как приведенные многочлены являются многочленами максимального периода, то перио их определяется выражением L 2 -1. Для п 3 (число разрядов регистра) период представляет последовательность и семи сигналов 1 11 О 1 О -О (последовательность сигналов, сформированная В прямом направлении счета). Представим исходное состояние как 100. При счет в прямом направлении состояние регистра изменяется следующим образом: 1. 1 О О 7.о о 1 8.1 О О При счете в обратном направлении соответственно1.1 О О 2.О О 1 О 8. 1 О О Если по сигналу начальной установки записывать в регистр исходную комбинацию 100, а дешифраторы 6 и 7. соответс венно настроить на комбинации 011 и 101, то после подсчета сигналов в любом направлении до указанных комбинаций дешифраторы срабатывают и записывают в регистр исходную комбинацию 100. В да ном примере до срабатывания дешифратор Может производиться подсчет трех импул сов в любом направлении счета. Положительный эффект изобретения зак лючается в расширении функциональных возможностей, а также в повышении быст родействия и надежности функционировани Практически независимо от числа разряд счетчика задержка постоянная минимальная и с увеличением числа разрядов счетчика не накапливается. Формула изобретени Реверсивный счетчик, содержащий cyjvK матор, регистр сдвига, элемент ИЛИ и первый и второй элементы И, первые входы которых Соединены соответственно с первым и вторым входами реверсивного счетчика,- отлича.ющийся тем, что, с целью обеспечения воаможностн Выработки сигналов при подсчете до определенной величины как в прям ом, так ив обратном направлениях, в него введены первый и второй дешифраторы и третий и четвертый элементы И, при этом тактовый вход регистра сдвига соединен со счетным входом реверсивного счетчика, первый и второй выходы регистра сдвига соединены с вторыми входами соответственно первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами сумматора, выход сумматора подключая к первым входам третьего и четвертого элементов И, вторые входы которых соединены соответственно с первым и вторым входами реверсивного счетчика, соединенными соответственно с первым и вторым управляющими входами регистра сдвига, информационные выходы которого соединены с Входами первого и второго дешифраторов, выходы дешифраторов соединены соответственно с выходами прямого и обратного счета реверсивного счетчика, которые подключены к первому и второму входам элемента ИЛИ, третий вход элемента ИЛИ соединен с входом установки реверсивного счетчика, а-выход - с входом установки регистра сдвига, дополнительный выход которого соединен с .третьим входом сумматора, а выходы третьего и четвертого элементов И соединены соответственно с первым и вторым дополнительными входами регистра сдвига. Источнгаси информации, пp нятыe во внимание при экспертизе 1. Авторское свидетельство СССР № 472Г461, кл. Н 03 К 23/ОО, 25.07.75. 2. Филиппов А. Г., Белкин О. С. Проектирование логических уа;ов ЭВМ, 197 с-228-229, рис. 3.29 прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Декодирующее устройство | 1989 |

|

SU1644223A1 |

| Устройство для формирования маски | 1988 |

|

SU1580344A1 |

| Устройство для формирования маски | 1988 |

|

SU1513459A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Преобразователь угол-код | 1987 |

|

SU1619398A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU907547A1 |

| Устройство для защиты данных | 1990 |

|

SU1837278A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

Авторы

Даты

1979-08-15—Публикация

1977-01-03—Подача