узла коммутации, выход которого соединен с первым входом К-го сумматора по модулю два группы, выходы сумматора по модулю два группы с первого по (К-1)-й соединены с информационными входами одноименных разрядов регистра сдвига, вь1ходыsKOToporo с первого по К-й соединеньг с соответствующими информационным й входами блока индикации и с входами сумматора по модул Два,- выход которбго соединен с первым входом т етьего элемента И, второй вход котор ого соединен с выходом первого элемента ИЛИ, выход третьего элемента И соединен с вторым входом К-го сумматора по модулю два группы, выход которого соединен с входом К-го разряда регистра сдвига, выхоп,- разрядов которого с второго по К-й соединены с вторыми входами с первого по (К-1)-и .сумматоров по модулю два группы, выходы разрядов регистра сдвига с (К+1)-го по ггй соединены с группой входов дго сумматора по модулю два группы, выходы которого с (К-И)-го по п-й соединены с входами одноименных разрядов регистра сдвига,, выходы разрядов которого с (К+2)-го по п-й соединены с вторыми входами с (к+1)-го по п-й сумматоров по модулю два группы соответственно, выход (К+1)-го разряда регистра сдвига соединен с вторым входом второго элемента И, выход которого соединен с третьим входом К-го сумматора по модулю два группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Сигнатурный анализатор | 1981 |

|

SU962962A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1191911A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля цифровых узлов | 1988 |

|

SU1695310A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Устройство для контроля многовы-ХОдНыХ цифРОВыХ узлОВ | 1979 |

|

SU817721A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ, содержащее генератор, тестов, блок индикации, два переключателя, два формирователя импульсов, счетчик, дешифратор, первый элемент ИЛИ, группу сумматоров по модулю два, регистр сдвига, сумматор по модулю два, узел коммутации, который содержит две группы элементов И и элемент ИЛИ, причем вход пуска устройства соединен с входом пуска генератора тестов, выходы метки начальной установки и метки сдвига которого соединены с соответствующими входами регистра сдвига, информационные выходы генератора тестов соединены с входами контролируемого цифрового блока, вьгход первого переключателя соединен с входом первого формирователя импульсов, выход которого соединен с входом обнуления счетчика, счетный вход которого соединен с выходом второго формирователя импульсов, группа выходов счетчика соединена с группой входов дешифратора, выходы которого соединены с группой управляющих входов блока индикации, входы первого элемента ИЛИ соединены с выходами дешифратора, за исключением первого выхода дешифратора, который соединен с первыми входами элементов И первой группы, выходы дешифратора с третьего по (п+2)-й (п- число выходов контролируемого цифрового блока) соединены с первыми входами элементов И второй группы, отличающееся тем, что, с целью повьш1ения достоверности контроля, оно дополнительно содержит два элемента ИДИ, три элемента И, причем выход второго переключателя соединен с первьм входом второго элемента ИЛИ, второй вход коi торого соединен с выходом первого элемента И, первьй вход которого (Л соединен с выходом метки конца контроля генератора тестов, второй вход первого элемента И соединен с первым выходом дешифратора, выход второго элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом второго формирова 00 теля импульсов, первьш и второй вхоо со о to ды третьего элемента ИЛИ соединены с первым и вторым выходами дешифратора, выход третьего элемента ИЛИ соединен с первым входом второго элемента И, вторые входы элементов И первой и второй групп соединены с соответствунйцими выходами контролируемого цифрового блока, выходы элементов И первой группы с первого по (К+1)-й (к - число разрядов сигнатуры) и с (К+1)-го по соединены с первыми входами одноименных сумматоров по модулю два группы, выходы элементов И второй группы и выход К-го элемен- . та И первой группы соединены с соответствующими входами элемента ИЛИ

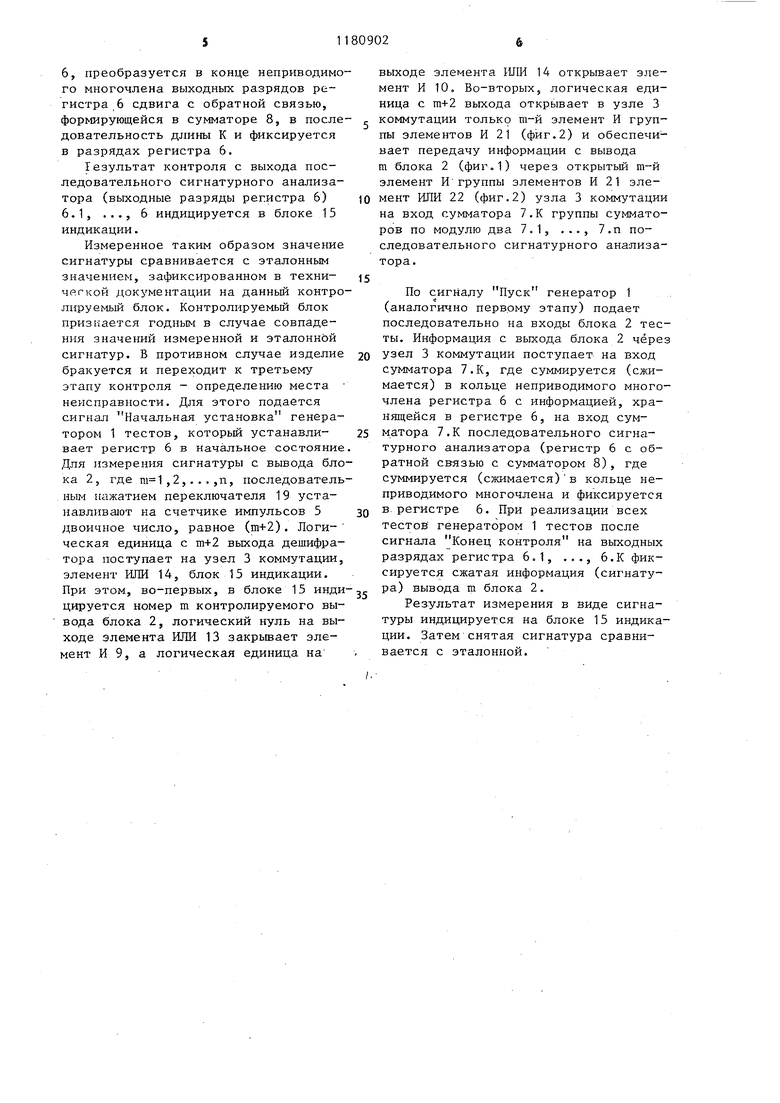

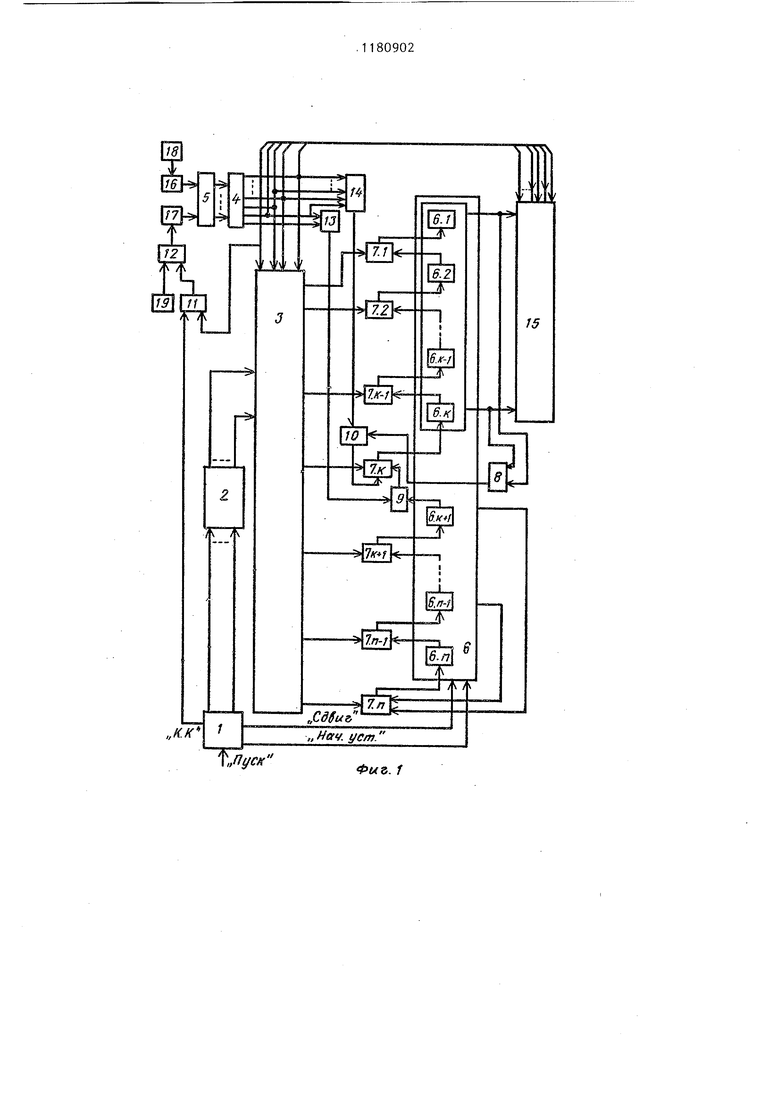

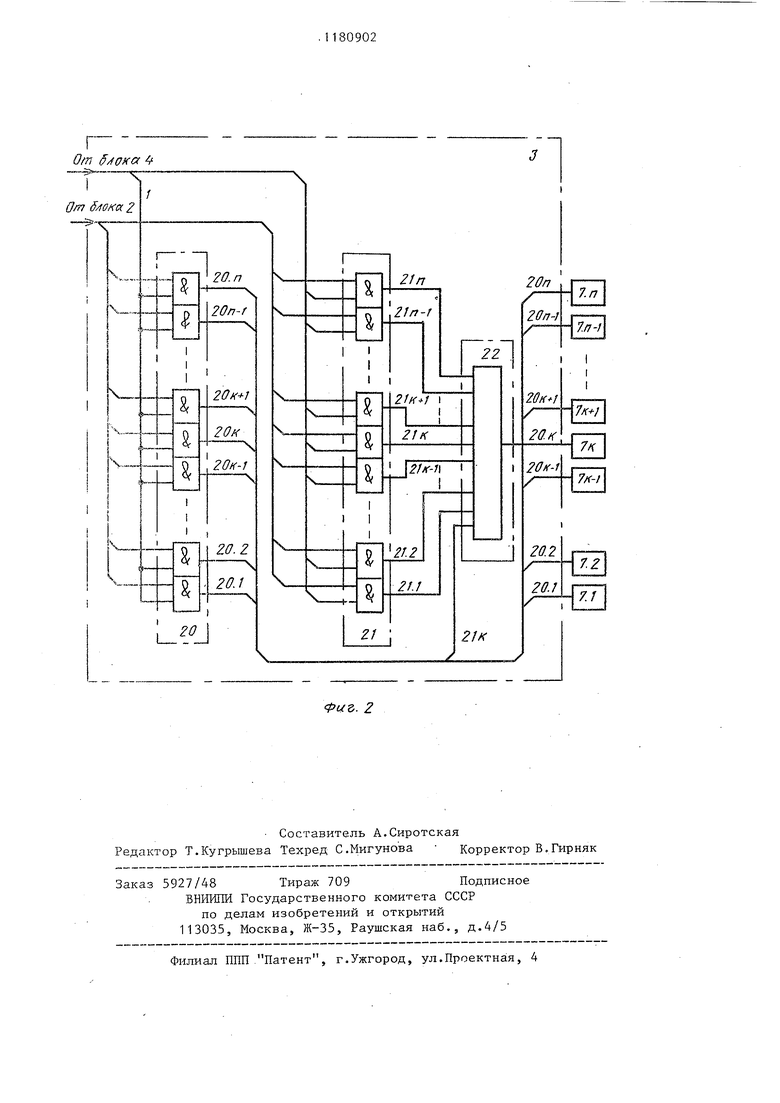

Изобретение относится к автоматике и вычислительной технике, в частности к автоматизированным системам контроля, и может быть использовано при контроле цифровых плат. Цель изобретения - повьшение до-стоверности контроля. На фиг.1 показана схема устройства, на фиг.2 - узел коммутации. Устройство для контроля цифровых блоков содержит генератор 1 тестов, контролируемый цифровой блок 2, узел 3 коммутации, дешифратор 4, счетчик 5, регистр 6 сдвига, группу сумматоров по модулю два 7, сумматор по модулю два 8, элементы И 9-11, элементы ИЛИ 12-14, блок 15 индикации, формирователи 16 и 17 импульсов, переключатели 18 и 19. Узел 3 коммутации (фиг.2) содержит группы элементов И 20 и 21, элемент ИЛИ 22. Устройство работает следующим образом. Работа устройства начинается с подачи сигнала начальной установки Начальная установка генератором 1 тестов, по которому разряды 6,1..., 6.К,6К+1,...,6.п регистра 6 сдвига длины п устанавливаются в начальное состояние. По нажатии переключателя 18 формирователь 16 одиночных импульсов вьфабатьшает импульс, который устанавливает счетчик 5 в начальное состояние, при котором на первом выходе дешифратора 4 устанавливается логическая единица. Выполняется первьш этап. , При этом, во-первых, логическая единица с первого выхода дешифратора 4 через элемент ИЛИ 13 открывает элемент И 9 и обеспечивает передачу информации с выхода регистра 6,К+1 сдвига на вход сумматора 7.К группы сумматоров по модулю два 7.1,...,7.п. Логический нуль с выхода элемента ИЛИ 14 закрывает элемент И 10, и сигналы с выхода сумматора по модулю два 9 не поступают на вход сумматора по модулю два 7.К. Во-вторых, логическая единица с первого выхода дешифратора 4 открывает элемент И 11 и группу элементов И 20 (фиг.2) узла 3 коммутации, Информа.цая параллельно с выводов блока 2 через элементы И 20 (фиг.2) узла 3 коммутации поступает на первые входы сумматоров 7.1, ..., 7.п группы сзшматоров по модулю два 7.1, .,., 7.п. Таким образом, в устройстве на сумматорах по модулю два 7.1,..., 7.П реализуется сжатие в п-разрядный код в кольце неприводимого многочлена (за счет цепей обратной связи регистра 6) информации, поступающей с выводов контролируемого узла 2, с информацией, хранящейся в регистре 6. Сжатая информация с выводов сумматоров 7,1, ..., 7.К, 7.К+1, .., 7,п по сигналу Сдвиг генератора 1 тестов записывается параллельно в разрядные регистры 6.1, ..., 6.К, 6.К+1,..,,6.п регистра 6 соответственно. Открытьй элемент И 9 и закрытьш элемент И 10 группой сумматоров 7.1, ..., 7.П и разряды регис тра 6.К+1, ..., 6.П образуют параллельный сигнатурный анализатор с сумматором по модулю два 7.п в цепи обрат ной связи. По сигналу Пуск генератор 1 тес тов выдает первый тест, который поступает на входы блока 2. Информация с вьшодов блока 2 через узел 3 комму тации поступает на входы сумматоров 7.1, ..., 7.П для сжатия. Запись результата первого теста производится по сигналу Сдвиг с генератора 1. Информация поканально записывается в разряды регистра 6 сдвига. Затем генератор реализует второй тест. По сигналу Сдвиг второй знак информации с вьшодов контролируемого блока 2, поканально сложенный по модулю два с информацией, хранящейся в регистре 6, в кольце неприводимого многочлена параллельного сигнатурног анализатора, записывается поканально в разряды регистра 6 и т.д. В результате реализации всех тестов последовательности сигналов с вьшодов контролируемогоблока 2 сжимаются на параллельном сигнатурном анализаторе в одну последовательност длины п.. На этом заканчивается выпол нение первого этапа контроля, и по сигналу Конец контроля (К.к.) ге нератора 1 тестов, который проходит через открытый первый элемент И 11 и второй элемент ИЛИ 12, первый формирователь 17 импульсов вырабатывает одиночный импульс, который поступает на счетный вход счетчика 5. На второ выходе дешифратора 4 возникает сигна Логическая единица. Начинается вто рой этап контроля. При этом узел коммутации закрыт, и информация с вьшодов блока 2 не поступает на входы сумматоров по мо124 дулю два 7.1, ..., 7.п. Логическая единица с второго выхода дешифратора 4 через .элемент ИЛИ 13 и элемент ИЛИ 14 открьшает элемент И 9 и третий элемент И 10 соответственно. Открытый третий элемент И 10 формирует в устройстве внутри параллельного сигнатурного анализатора электрические цепи для реализации последовательного сигнатурного анализатора, которьй включает выходные разряды регистра 6 сдвига, открытый третий элемент И 10, сумматор 8 и сумматор по модулю два 7.К в цепи обратной связи. Информация с выхода разряда регистра сдвига 6.К+1 регистра 6 через открытый второй элемент И 9 поступает на вход последовательного сигнатурного анализатора (сумматор 7.К), где суммируется с сигналами обратной связи сумматора 8. Сигналы обратной связи с выхода сумматора 8 через открытый элемент И 10 поступают на вход сумматора 7. К. По сигналу Сдвиг генератора 1 тестов последовательность длины п, полученная в результате выполнения первого этапа контроля и хранящаяся в регистре 6, сжимается в последовательность длины п-1. При этом информация с выходов одноразрядных регистров 6.П, 6.п-1, ..., 6,К+2 через сумматоры 7.п-1, 7.п-2,...,7.К+ +1 записывается в разряды регистра 6.П--1 ,6.п-2, ...,6.К+1 соответственно. Информация, хранящаяся в выходных разрядах регистра 6.1, -.. ., 6.К регистра 6, сжимается в кольце неприводимого многочлена последовательного сигнатурного анализатора с сумматором по модулю два 8 в цепи обратной связи с информацией на выходе разряда регистра 6.К+1, которая поступает через открытый элемент И 9 на вход сумматора 7.К. По следующему сигналу Сдвиг последовательность длины п-1, хранящаяся в регистре-6, снимается в последовательность длины п-2 и т.д. до тех пор, пока сжатая последовательность не станет равной длине К, где К - число разрядов сигнатуры в двоичном представлении (число разрядов выходного регистра 6 сдвига обычно ). Таким образом, при подаче последовательности п-К сигналов Сдвиг генератора 1 тестов последовательность длины п, хранящаяся в регистре

6, преобразуется в конце неприводимого многочлена выходных разрядов регистра 6 сдвига с обратной связью, формирующейся в сумматоре 8, в последовательность длины К и фиксируется в разрядах регистра 6.

Гезультат контроля с выхода последовательного сигнатурного анализатора (выходные разряды регистра 6) 6.1, ..., 6 индицируется в блоке 15 индикации.

Измеренное таким образом значение сигнатуры сравнивается с эталонным значением, зафиксированном в техничвгкой документации на данный контролируемый блок. Контролируемый блок признается годным в случае совпадения значений измеренной и эталонной сигнатур. В противном случае изделие бракуется и переходит к третьему этапу контроля - определению места неисправности. Для этого подается сигнал Начальная установка генератором 1 тестов, которьй устанавливает регистр 6 в начальное состояние Для измерения сигнатуры с вывода блока 2, где ,2,. . . ,п, последовательным нажатием переключателя 19 устанавлившот на счетчике импульсов 5 двоичное число, равное (т+2). Логическая единица с т+2 выхода дешифратора поступает на узел 3 коммутации, элемент ИЛИ 14, блок 15 индикации. При этом, во-первых, в блоке 15 индицируется номер m контролируемого вывода блока 2, логический нуль на выходе элемента ИЛИ 13 закрьшает элемент И 9, а логическая единица на

выходе элемента ИЛИ 14 открывает элемент И 10. Во-вторых, логическая единица с т+2 выхода открывает в узле 3 2 коммутации только т-й элемент И группы элементов И 21 (фиг.2) и обеспечивает передачу информации с вывода га блока 2 (фиг.1) через открытый ш-й элемент Игруппы элементов И 21 элеO мент ИЛИ 22 (фиг.2) узла 3 коммутации на вход сумматора 7.К группы сумматоров по модулю два 7.1, ..., 7.п последовательного сигнатурного анализатора.

По сигналу Пуск генератор 1 (аналогично первому этапу) подает последовательно на входы блока 2 тесты. Информация с выхода блока 2 через

0 узел 3 коммутации поступает на вход сумматора 7.К, где суммируется (сжимается) в кольце неприводимого многочлена регистра 6 с информацией, хранящейся в регистре 6, на вход сумматора 7.К последовательного сигнатурного анализатора (регистр 6 с обратной связью с сумматором 8), где суммируется (сжимается)в кольце неприводимого многочлена и фиксируется

Q в регистре 6. При реализации всех тестов генератором 1 тестов после сигнала Конец контроля на выходных разрядах регистра 6.1, .,., 6.К фиксируется сжатая информация (сигнатура) вывода m блока 2.

Результат измерения в виде сигнатуры индицируется на блоке 15 индикации. Затем снятая сигнатура сравнивается с эталонной.

Г

От лока

0/77 S/tOKK Z

I i ----

L.

Риъ. Z

| Устройство для контроля логических блоков | 1980 |

|

SU951312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-01-09—Подача