Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах для обнаружения ошибок в быстродействующих накопителях с последовательным доступом.

Устройство предназначено для реализации циклических кодов, задаваемых обычным полиномом кода Файоа вида Р(х) (хс - 1) Pi(x) или псгиномом

m

обобщенного кода вида Р (х) (х - 1)ПР|(х),

J 1

где Рч(х) и Pj(x) - неприводимые полиномы степени В и Bj соответственно, j 1. 2,...

Цель изобретения - расширение функциональных возможностей и области применения устройств за счет обеспечения возможности кодирования и декодирования кодов различной длины.

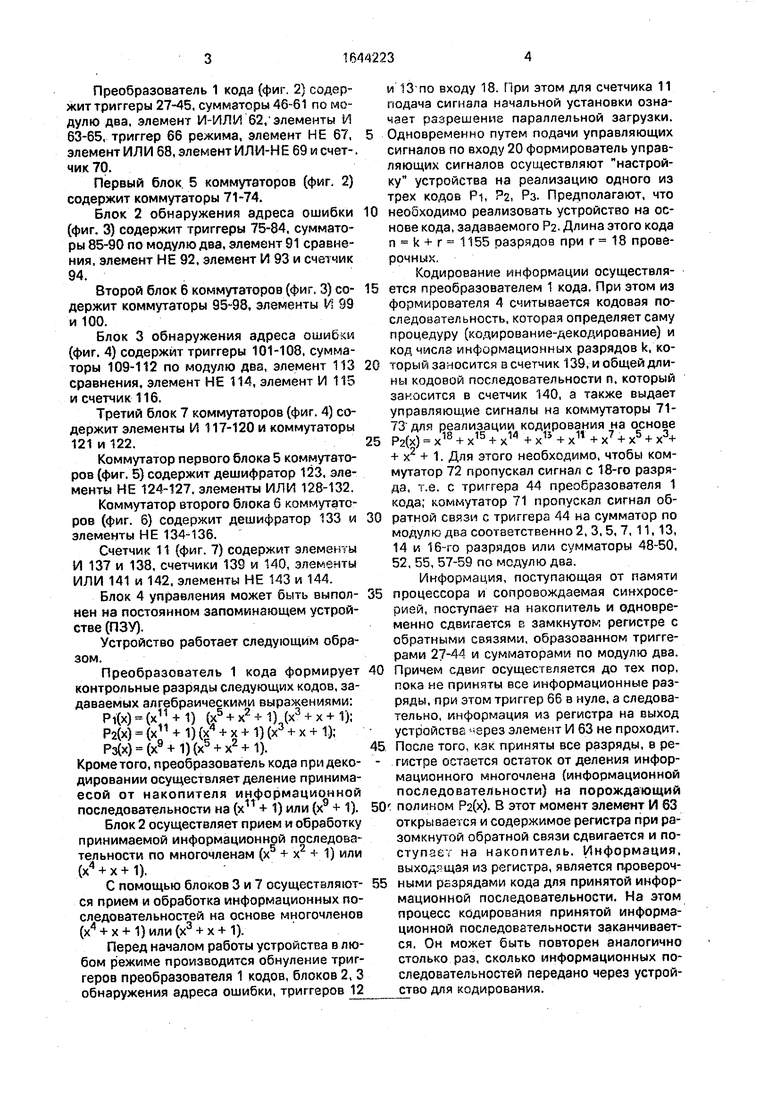

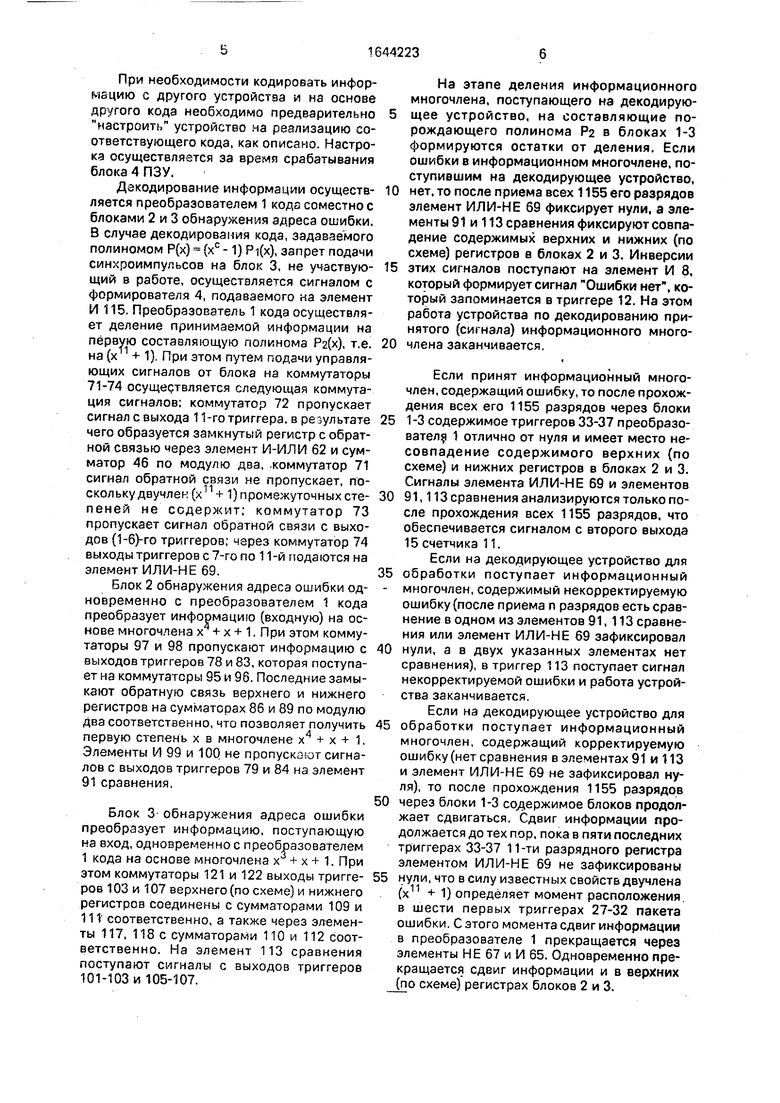

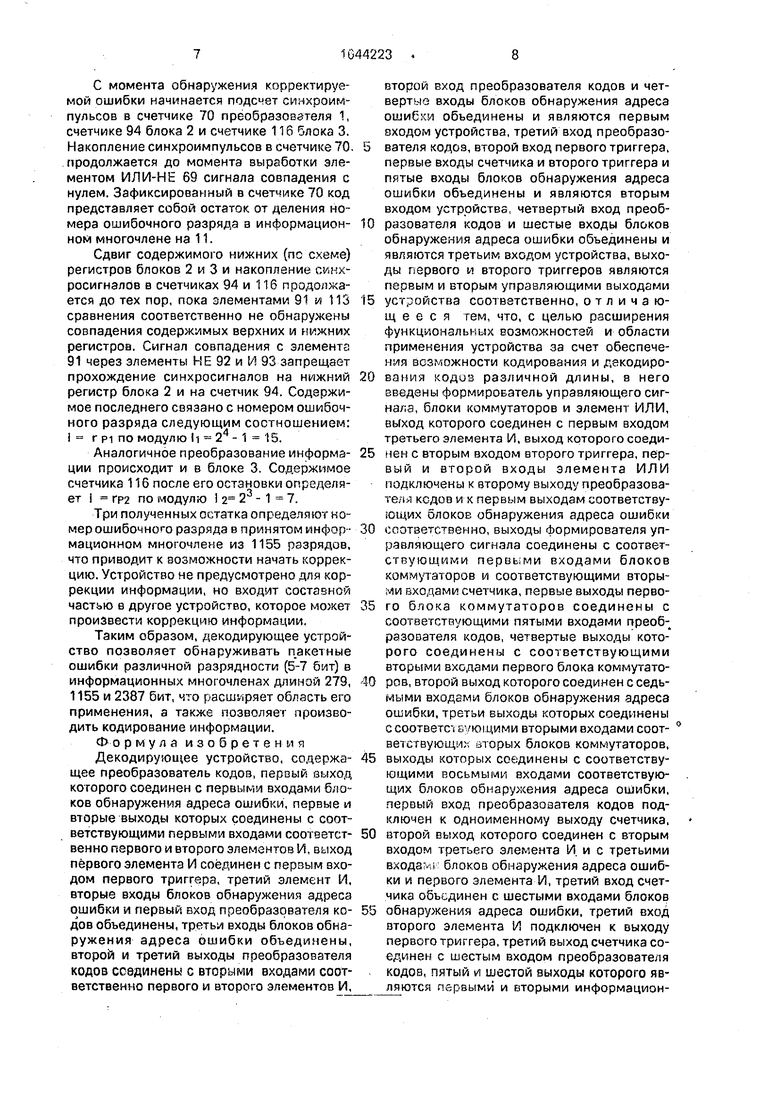

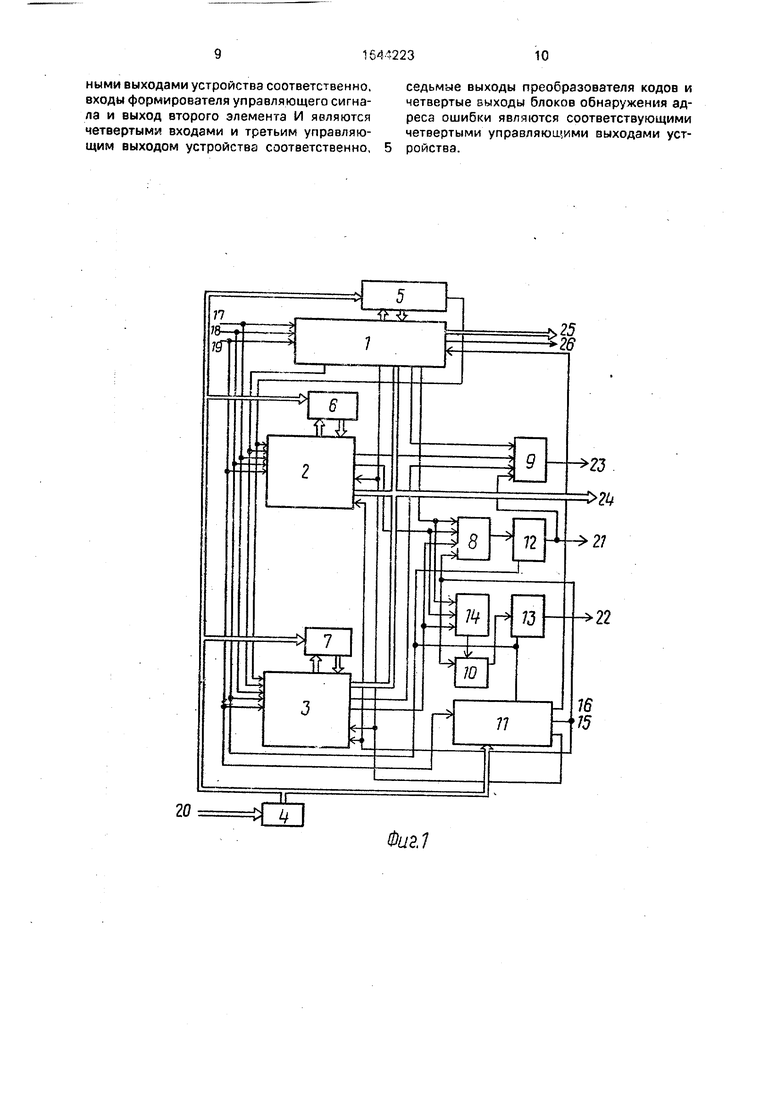

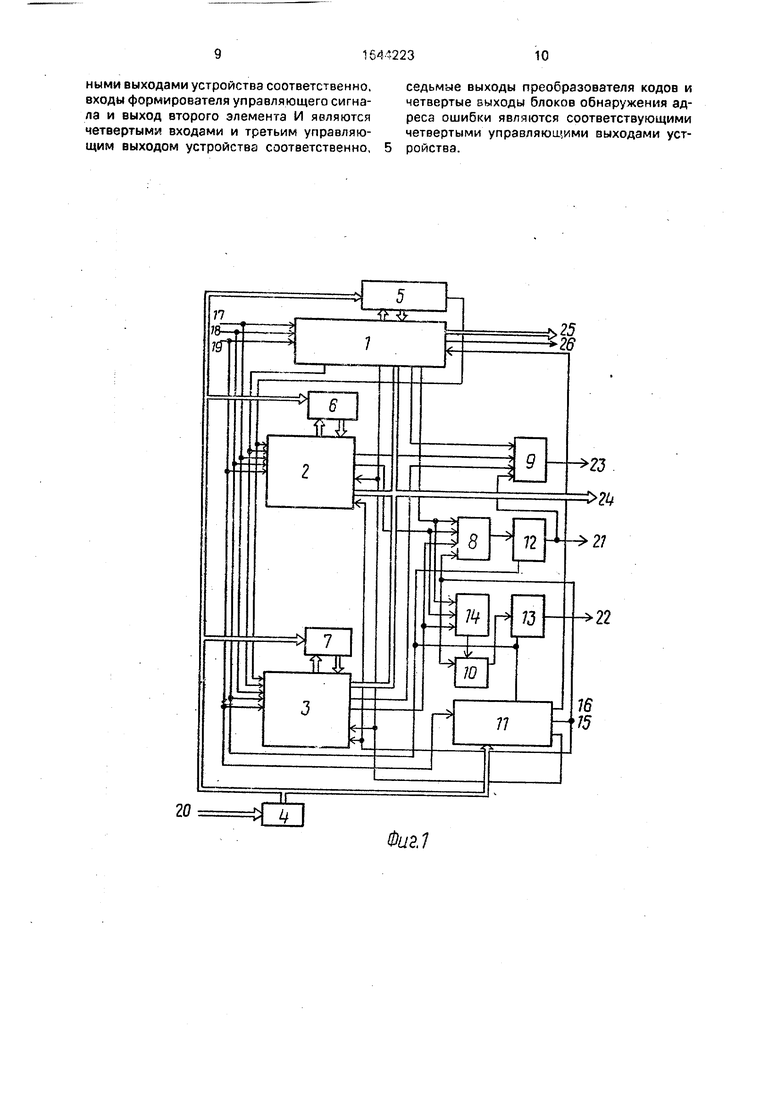

На фиг. 1 представлена функциональная схема декодирующего устройства; на фиг. 2 - функциональная схема преобразователя кодов с первым блоком коммутаторов; на фиг. 3 - функциональная схема блока обнаружения адреса ошибки с вторым блоком коммутаторов; на фиг. 4 - функциональная схема блока обнаружения адреса ошибки с третьим блоком коммутаторов; на фиг. 5 - функциональная схема одного из коммутаторов первого блока коммутаторов; на фиг. 6 - функциональная схема одного из коммутаторов второго блока коммутаторов; на фиг. 7 - функциональная схема счетчика. Декодирующее устройство (фиг. 1) содержит преобразователь 1 кода, блоки 2 и 3 обнаружения адреса ошибки, формирователь 4 управляющего сигнала, первый - третий блоки 5-7 коммутаторов, первый - третий элементы И 8-10, счетчик 11, первый 12 и второй 13 триггеры, элемент ИЛИ 14. Кроме того, показаны второй 15 и третий 16 выходы счетчика 11, первый - четвертые входы 17-20устройства, первый-четвертые управляющие выходы 21-24 устройства и первые 25 и второй 26 информационные выходы устройства.

Ё

&

±

Јь ю к со

Преобразователь 1 кода (фиг. 2) содержит триггеры 27-45, сумматоры 46-61 по модулю два, элемент И-ИЛИ 62, элементы И 63-65, триггер 66 режима, элемент НЕ 67, элемент ИЛ И 68, элемент И ЛИ-Н Е 69 и счет-. чик 70.

Первый блок 5 коммутаторов (фиг, 2) содержит коммутаторы 71-74.

Блок 2 обнаружения адреса ошибки (фиг. 3) содержит триггеры 75-84, сумматоры 85-90 по модулю два, элемент 91 сравнения, элемент НЕ 92, элемент И 93 и счетчик 94.

Второй блок 6 коммутаторов (фиг. 3) содержит коммутаторы 95-98, элементы А 99 и 100.

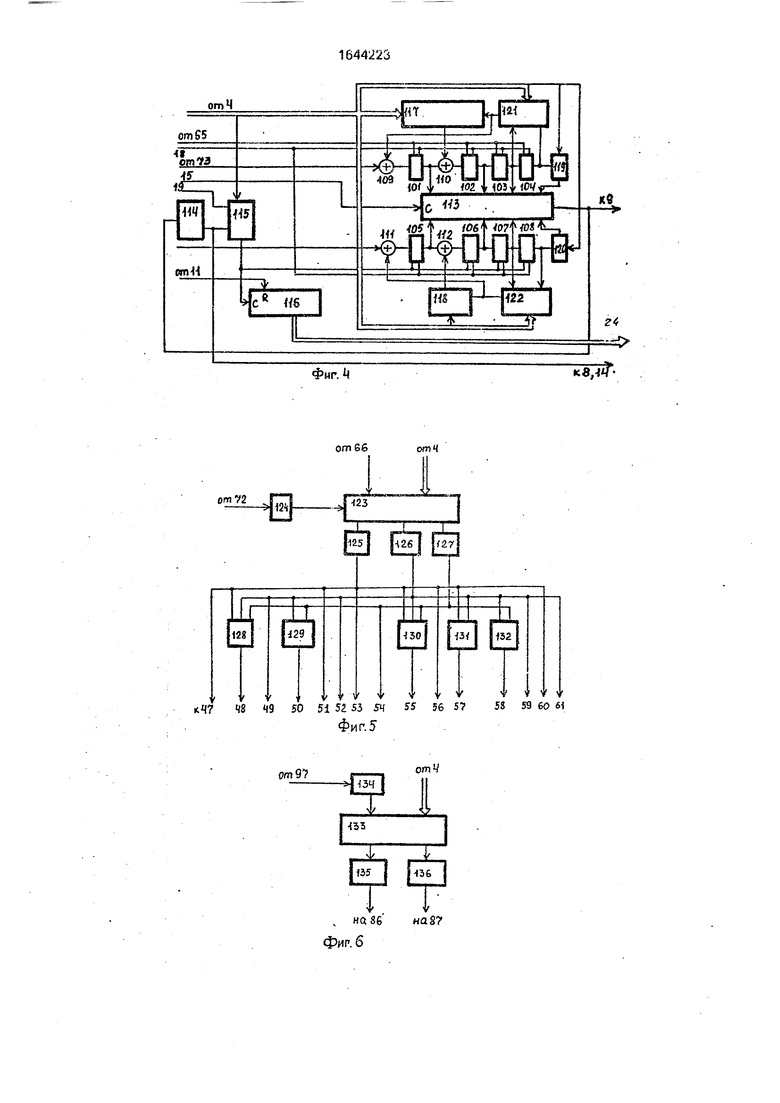

Блок 3 обнаружения адреса ошибки (фиг. 4) содержит триггеры 101-108, сумматоры 109-112 по модулю два, элемент 113 сравнения, элемент НЕ 114, элемент И 115 и счетчик 116.

Третий блок 7 коммутаторов (фиг. 4) содержит элементы И 117-120 и коммутаторы 121 и 122.

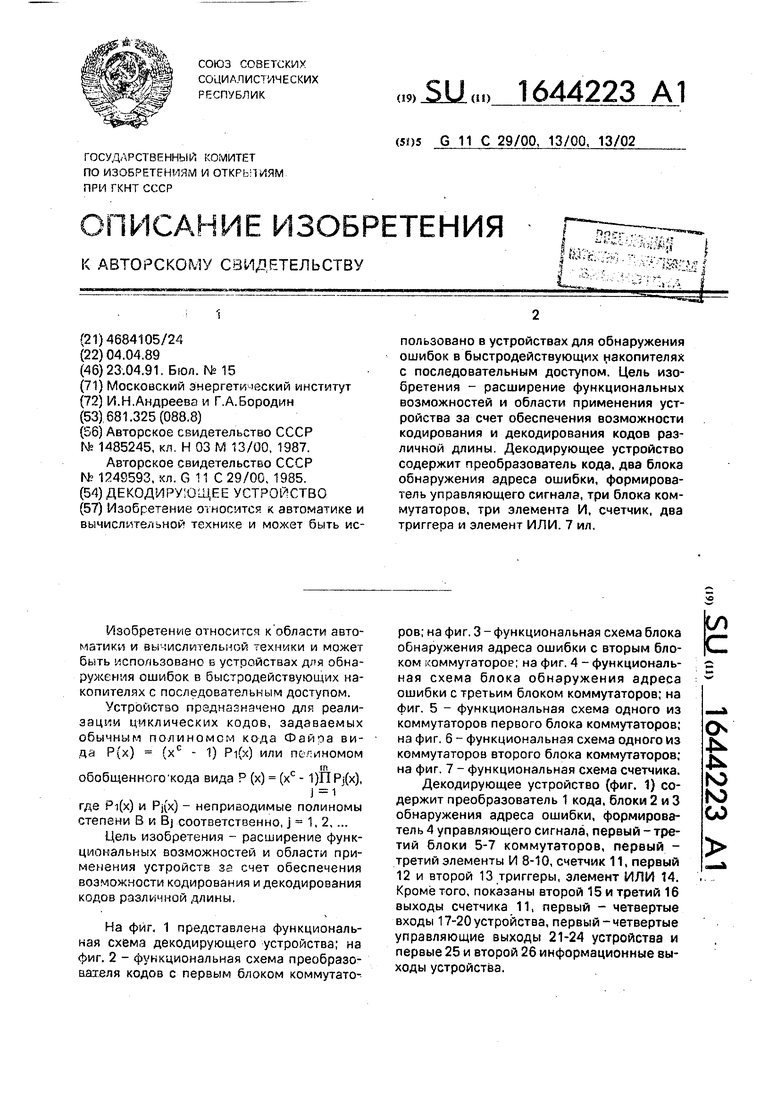

Коммутатор первого блока 5 коммутаторов (фиг. 5} содержит дешифратор 123, элементы НЕ 124-127. элементы ИЛИ 128-132.

Коммутатор второго блока б коммутаторов (фиг. 6) содержит дешифратор 133 м элементы НЕ 134-136.

Счетчик 11 (фиг. 7) содержит элементы И 137 и 138, счетчики 139 и 140, элементы ИЛИ 141 и 142, элементы НЕ 143 и 144.

Блок 4 управления может быть выполнен на постоянном запоминающем устройстве (ПЗУ).

Устройство работает следующим образом.

Преобразователь 1 кода формирует контрольные разряды следующих кодов, задаваемых алгебраическими выражениями:

PiM (х11 + 1) fx5 + х2 + 1Нх3 + х + 1):

., v- 1) (Х + Х. Р2М (X11 + 1) (X4 + X + 1) (X3 + X 4- 1);

Рз(х) (х9+1)(х5 + х2+1).

1);

Кроме того, преобразователь кода при декодировании осуществляет деление принима- есой от накопителя информационной последовательности на (x1t + 1) или (х9 + 1).

Блок 2 осуществляет прием и обработку принимаемой информационной последовательности по многочленам (х + х2 + 1) или (х4 + х + 1).

С помощью блоков 3 и 7 осуществляются прием и обработка информационных последовательностей на основе многочленов (х4 + х + 1) или (х3 + х + 1).

Перед началом работы устройства в любом режиме производится обнуление триггеров преобразователя 1 кодов, блоков 2, 3 обнаружения адреса ошибки, триггеров 12

м 13-по входу 18. При этом для счетчика 11 подача сигнала начальной установки означает разрешение параллельной загрузки.

Одновременно путем подачи управляющих сигналов по входу 20 формирователь управляющих сигналов осуществляют настройку устройства на реализацию одного из трех кодов Pt, 2, Рз. Предполагают, что

0 необходимо реализовать устройство на основе кода, задаваемого Р2. Длина этого кода п к + г 1155 разрядов при г 18 проверочных.

Кодирование информации осуществля5 ется преобразователем 1 кода. При этом из формирователя 4 считывается кодовая последовательность, которая определяет саму процедуру (кодирование-декодирование) и код числа информационных разрядов к, ко0 торы и за носится всчетчик 139, и общей длины кодовой последовательности п, который заносится в счетчик 140, а также выдает управляющие сигналы на коммутаторы 71- 73 для реализации кодирования на основе

5 Р2(х) х18 + х15 + х14 + х15 + х11 + х7 + х5 + х3+ + х2 + 1. Для этого необходимо, чтобы коммутатор 72 пропускал сигнал с 18-го разряда, т.е. с триггера 44 преобразователя 1 кода; коммутатор 71 пропускал сигнал об0 ратной связи с триггера 44 на сумматор по модулю два соответственно 2, 3,5, 7, 11,13, 14 и 16-го разрядов или сумматоры 48-50, 52, 55, 57-59 по модулю два.

Информация, поступающая от памяти

5 процессора и сопровождаемая синхросе- рией, поступает на накопитель и одновременно сдвигается в замкнутом регистре с обратными связями, образованном триггерами 27-44 и сумматорами по модулю два.

0 Причем сдвиг осуществляется до тех пор, пока не приняты все информационные разряды, при этом триггер 66 в нуле, а следовательно, информация из регистра на выход устройства элемент И 63 не проходит.

5 После того, как приняты все разряды, в ре- - гистре остается остаток от деления информационного многочлена (информационной последовательности) на порождающий

0 полином Р2(х). В этот момент элемент И 63 открывается и содержимое регистра при разомкнутой обратной связи сдвигается и поступает на накопитель. Информация. выходящая из регистра, является ггровероч5 ными разрядами кода для принятой информационной последовательности. На этом процесс кодирования принятой информационной последовательности заканчивается. Он может быть повторен аналогично столько раз, сколько информационных последовательностей передано через устройство для кодирования.

При необходимости кодировать информацию с другого устройства и на основе другого кода необходимо предварительно настроить устройство на реализацию соответствующего кода, как описано. Настро- ка осуществляется за время срабатывания блока 4 ПЗУ.

Декодирование информации осуществ- ляется преобразователем 1 кода соместно с блоками 2 и 3 обнаружения адреса ошибки. В случае декодирования кода, задаваемого полиномом Р(х) (х° -1) Pi(x), запрет подачи синхроимпульсов на блок 3, не участвую- щий в работе, осуществляется сигналом с формирователя 4, подаваемого на элемент И 115. Преобразователь 1 кода осуществляет деление принимаемой информации на первую составляющую полинома Р2(х), т.е. на (х + 1). При этом путем подачи управляющих сигналов от блока на коммутаторы 71-74 осуществляется следующая коммутация сигналов: коммутатор 72 пропускает сигнал с выхода 11-го триггера, в результате чего образуется замкнутый регистр с обратной связью через элемент И-ИЛИ 62 и сумматор 46 по модулю два, .коммутатор 71 сигнал обратной связи не пропускает, поскольку двучлен (х + 1) промежуточных сте- пеней не содержит; коммутатор 73 пропускает сигнал обратной связи с выходов (1-6)-го триггеров; через коммутатор 74 выходы триггеров с 7-го по 11-й подаются на элемент ИЛИ-НЕ 69.

Блок 2 обнаружения адреса ошибки од- новременно с преобразователем 1 кода преобразует информацию (входную) на основе многочлена х + х + 1, При этом коммутаторы 97 и 98 пропускают информацию с выходов триггеров 78 и 83, которая поступает на коммутаторы 95 и 96. Последние замыкают обратную связь верхнего и нижнего регистров на сумматорах 86 и 89 по модулю два соответственно, что позволяет получить первую степень х в многочлене х + х + 1. Элементы И 99 и 100 не пропускают сигналов с выходов триггеров 79 и 84 на элемент 91 сравнения,

Блок 3 обнаружения адреса ошибки преобразует информацию, поступающую на вход, одновременно с преобразователем 1 кода на основе многочлена х + х + 1. При этом коммутаторы 121 и 122 выходы тригге- ров 103 и 107 верхнего (по схеме) и нижнего регистров соединены с сумматорами 109 и 111 соответственно, а также через элементы 117, 118 с сумматорами 110 и 112 соответственно. На элемент 113 сравнения поступают сигналы с выходов триггеров 101-103 и 105-107.

На этапе деления информационного многочлена, поступающего на декодирующее устройство, на составляющие порождающего полинома Рг в блоках 1-3 формируются остатки от деления. Если ошибки в информационном многочлене, поступившим на декодирующее устройство, нет, то после приема всех 1155 его разрядов элемент ИЛИ-НЕ 69 фиксирует нули, а элементы 91 и 113 сравнения фиксируют совпадение содержимых верхних и нижних (по схеме) регистров в блоках 2 и 3. Инверсии этих сигналов поступают на элемент И 8, который формирует сигнал Ошибки нет, который запоминается в триггере 12. На этом работа устройства по декодированию принятого (сигнала) информационного многочлена заканчивается.

Если принят информационный многочлен, содержащий ошибку, то после прохождения всех его 1155 разрядов через блоки 1-3 содержимое триггеров 33-37 преобразователя 1 отлично от нуля и имеет место несовпадение содержимого верхних (по схеме) и нижних регистров в блоках 2 и 3. Сигналы элемента ИЛИ-НЕ 69 и элементов 91,113 сравнения анализируются только после прохождения всех 1155 разрядов, что обеспечивается сигналом с второго выхода 15 счетчика 11.

Если на декодирующее устройство для обработки поступает информационный многочлен, содержимый некорректируемую ошибку (после приема п разрядов есть сравнение в одном из элементов 91, 113 сравнения или элемент ИЛИ-НЕ 69 зафиксировал нули, а в двух указанных элементах нет сравнения), в триггер 113 поступает сигнал некорректируемой ошибки и работа устройства заканчивается.

Если на декодирующее устройство для обработки поступает информационный многочлен, содержащий корректируемую ошибку (нет сравнения в элементах 91 и 113 и элемент ИЛИ-НЕ 69 не зафиксировал нуля), то после прохождения 1155 разрядов через блоки 1-3 содержимое блоков продолжает сдвигаться. Сдвиг информации продолжается до тех пор, пока в пяти последних триггерах 33-37 11-ти разрядного регистра элементом ИЛИ-НЕ 69 не зафиксированы нули, что в силу известных свойств двучлена (х11 + 1) определяет момент расположения в шести первых триггерах 27-32 пакета ошибки. С этого момента сдвиг информации в преобразователе 1 прекращается через элементы НЕ 67 и И 65. Одновременно прекращается сдвиг информации и в верхних (по схеме) регистрах блоков 2 и 3.

С момента обнаружения корректируемой ошибки начинается подсчет синхроимпульсов в счетчике 70 преобразователя 1, счетчике 94 блока 2 и счетчике 116 блока 3. Накопление синхроимпульсов в счетчике 70. продолжается до момента выработки элементом ИЛИ-НЕ 69 сигнала совпадения с нулем. Зафиксированный в счетчике 70 код представляет собой остаток от деления номера ошибочного разряда в информационном многочлене на 11.

Сдвиг содержимого нижних (пс схеме) регистров блоков 2 и 3 и накопление синхросигналов в счетчиках 94 и 116 продолжается до тех пор, пока элементами 91 и 113 сравнения соответственно не обнаружены совпадения содержимых верхних и нижних регистров. Сигнал совпадения с элемента 91 через элементы НЕ 92 и И 93 запрещает прохождение синхросигналов на нижний регистр блока 2 и на счетчик 94. Содержимое последнего связано с номером ошибочного разряда следующим соотношением: I r pi по модулю И 24 - 1 15.

Аналогичное преобразование информации происходит и в блоке 3. Содержимое счетчика 116 после его остановки определяет i rpz по модулю I 2 2 - 1 7.

Три полученных остатка определяют номер ошибочного разряда в принятом информационном многочлене из 1155 разрядов, что приводит к возможности начать коррекцию. Устройство не предусмотрено для коррекции информации, но входит составной частью в другое устройство, которое может произвести коррекцию информации.

Таким образом, декодирующее устройство позволяет обнаруживать пакетные ошибки различной разрядности (5-7 бит) в информационных многочленах длиной 279, 1155 и 2387 бит, что расширяет область его применения, а также позволяет производить кодирование информации.

Формула изобретения

Декодирующее устройство, содержащее преобразователь кодов, первый выход которого соединен с первыми входами блоков обнаружения адреса ошибки, первые и вторые выходы которых соединены с соответствующими первыми входами соответственно первого и второго элементов И, выход первого элемента И соединен с первым входом первого триггера, третий элемент И, вторые входы блоков обнаружения адреса ошибки и первый вход преобразователя кодов объединены, третьи входы блоков обнаружения адреса ошибки объединены, второй и третий выходы преобразователя кодов соединены с вторыми входами соответственно первого и второго элементов И,

второй вход преобразователя кодов и четвертые входы блоков обнаружения адреса ошибки объединены и являются первым входом устройства, третий вход преобразователя кодоэ, второй вход первого триггера, первые входы счетчика и второго триггера и пятые входы блоков обнаружения адреса ошибки объединены и являются вторым входом устройства, четвертый вход преоб0 разователя кодов и шестые входы блоков обнаружения адреса ошибки объединены и являются третьим входом устройства, выходы первого и второго триггеров являются первым и вторым управляющими выходами

5 устройства соответственно, отличающееся тем, что, с целью расширения функциональных возможностей и области применения устройства за счет обеспечения возможности кодирования и дакодиро0 вания кодов различной длины, в него введены формирователь управляющего сигнала, блоки коммутаторов и элемент ИЛИ, выход которого соединен с первым входом третьего элемента И, выход которого соеди5 йен с вторым входом второго триггера, первый и второй входы элемента ИЛИ подключены к второму выходу преобразователя кедов и к первым выходам соответствующих блоков обнаружения адреса ошибки

0 соответственно, выходы Формирователя управляющего сигнала соединены с соответствующими первыми входами блоков коммутаторов и соответствующими вторыми входами счетчика, первые выходы перво5 го блока коммутаторов соединены с соответствующими пятыми входами преобразователя кодов, четвертые выходы которого соединены с соответствующими вторыми входами первого блока коммутато0 ров, второй выход которого соединен с седьмыми входами блоков обнаружения адреса ошибки, третьи выходы которых соединены есоответс БАЮЩИМИ вторыми входами соответствующие вторых блоков коммутаторов,

5 выходы которых соединены с соответствующими восьмыми входами соответствующих блоков обнаружения адреса ошибки, первый вход преобразователя кодов подключен к одноименному выходу счетчика,

0 второй выход которого соединен с вторым входом третьего элемента И и с третьими входам блоков обнаружения адреса ошибки и первого элемента И, третий вход счетчика объединен с шестыми входами блоков

5 обнаружения адреса ошибки, третий вход второго элемента И подключен к выходу первого триггера, третий выход счетчика соединен с шестым входом преобразователя кодов, пятый и шестой выходы которого являются первыми и вторыми информациейными выходами устройства соответственно, входы формирователя управляющего сигнала и выход второго элемента И являются четвертыми входами и третьим управляющим выходом устройства соответственно,

седьмые выходы преобразователя кодов и четвертые выходы блоков обнаружения адреса ошибки являются соответствующими четвертыми управляющими выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в блоках памяти | 1987 |

|

SU1594611A1 |

| Устройство для контроля информации | 1987 |

|

SU1522210A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

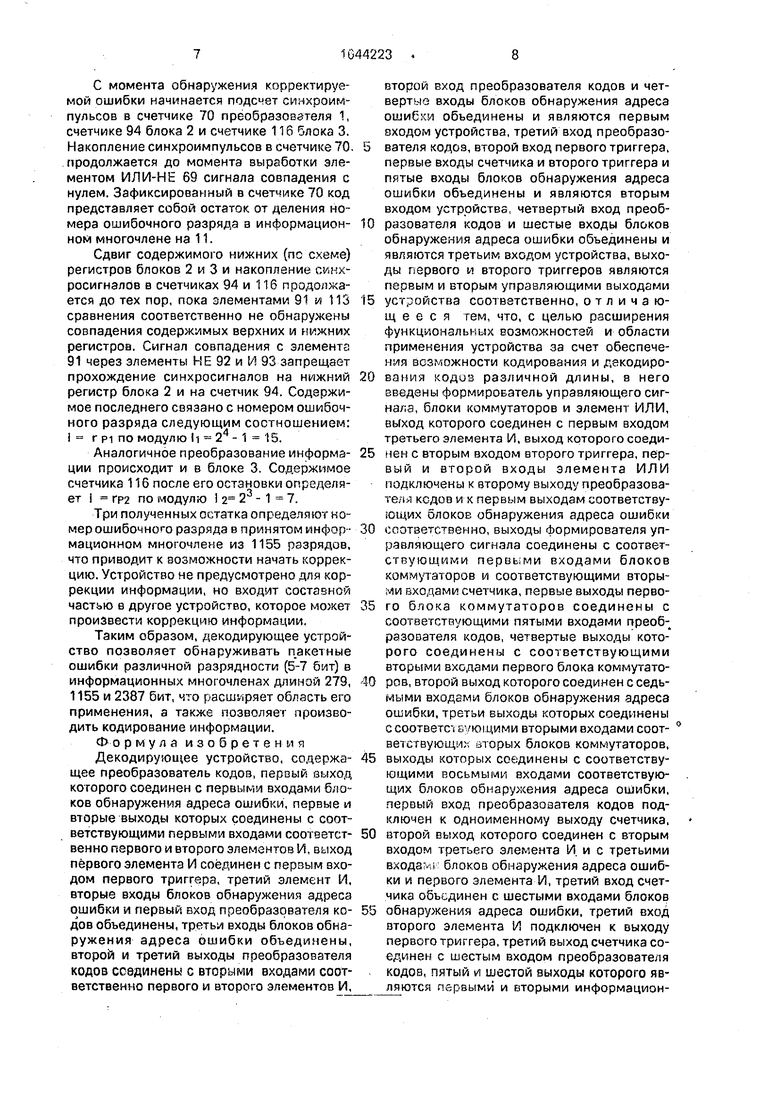

Изобретение oi носится к автоматике и вычислительной технике и может быть использовано в устройствах для обнаружения ошибок в быстродействующих накопителях с последовательным доступом. Цель изобретения - расширение функциональных возможностей и области применения устройства за счет обеспечения возможности кодирования и декодирования кодов различной длины. Декодирующее устройство содержит преобразователь кода, два блока обнаружения адреса ошибки, формирователь управляющего сигнала, три блока коммутаторов, три элемента И, счетчик, два триггера и элемент ИЛИ. 7 ил.

20

Л I

Т

Фиг.1

от Ц

Фиг. 3

иг2

с

-Ь.

Ј

rc

N5

U «

от Ч

«9

9

Ю7

«/

W

6

142

«V

5

а

| Авторское свидетельство СССР № 1485245, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-23—Публикация

1989-04-04—Подача