Изобретение относится к вычисли-: тельной технике, предназначено для защиты от несанкционированного доступа к информации и может быть ис- пользовано для маскирования идентификаторов пользователей.

Цель изобретения - повышение быстродействия.

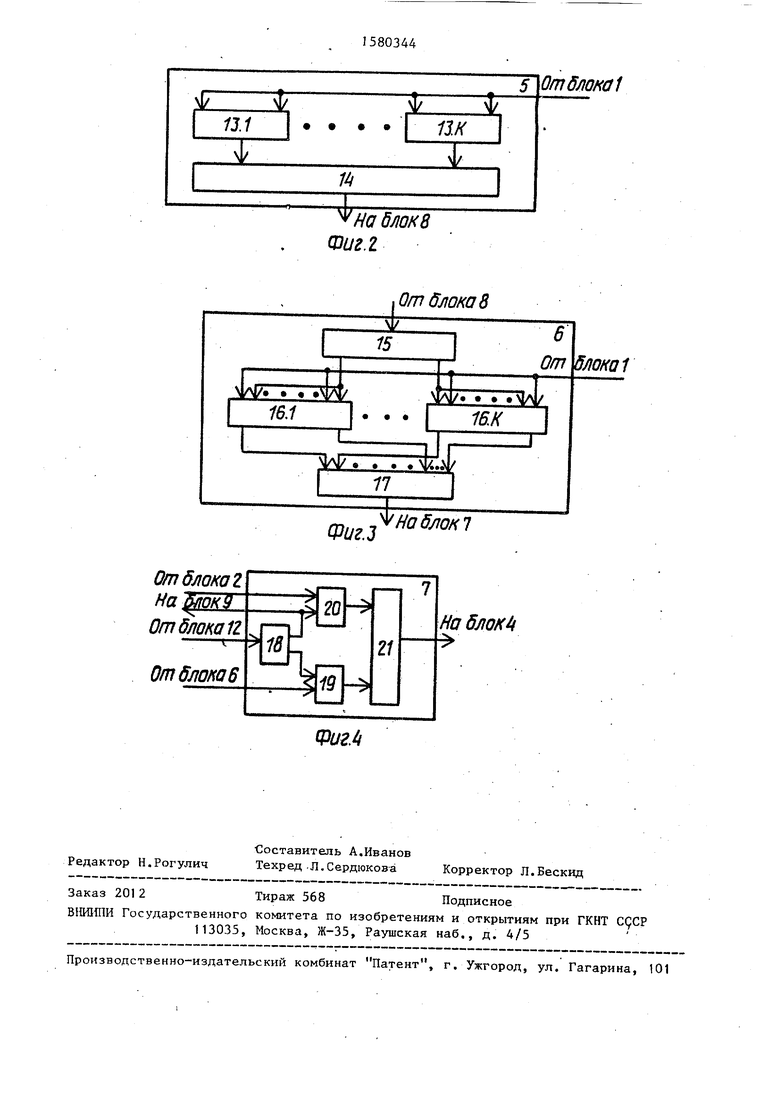

На фиг.1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока определения формата; на фиг. 3 - функциональная схема блока формирования числа; на фиг. 4 - функциональная схема блока установки ключа.

Устройство (фиг.1) содержит буферный регистр 1, регистр 2 сдвига, блок сумматоров 3 по модулю два, счетчик 4 битов, блок 5 определения фор- мата, блок 6 формирования числа,блок 7 установки ключа, счетчик 8 слов, триггер 9, первый 10, второй 11 и третий 12 элементы И.

Буферный регистр 1 предназначен для хранения идентификатора, для которого в данный момент вырабатывается маска. Он представляет собой регистр сдвига с количеством разрядо равных разрядности идентификатора.

Регистр 2 совместно с сумматором 3 по модулю два предназначен для получения частного от деления идентификатора, хранящегося в буферном регистре 1, на полином Р(х) в поле Галуа. Полином F(x) определяется видом обратных связей, замыкаемых с выходов регистра 2 сдвига через сумматор 3 по модулю два на его вход.

Счетчик 4 битов предназначен для задания количества шагов деления идентификатора на многочлен F(X).

Блок 5 определения формата служит для определения количества блоков (слов) идентификатора за- ранее установленной длины (формат идентификатора). Он может быть выполнен по схеме, приведенной на фиг.2. Блок 5 определения формата содержит группу эле- ментов ИЛИ 13.1 - 13.К и дешифратор 14. Количество входов каждого элемента ИЛИ равно длине одного слова идентификатора, а количество элементов ИЛИ равно максимально допустимому формату идентификатора. Появление сигнала на выходе любого из элментов ИЛИ 13.1 - 13.К означает налчие хотя бы одного единичного бита

5

0

5 Q

.«

45 5„

5

55

в данном отрезке идентификатора, а значит, и наличие самого слова. Следовательно, формат поступившего идентификатора определяется сигналом на крайнем справа элементе ИЛИ. Данный позиционный код преобразовывается в двоичный дешифратором 14.

Блок 6 формирования числа предназначен для выборки из буферного регистра 1 соответствующего слова идентификатора. Он может быть выполнен по схеме, приведенной на фиг.З. Блок 6 формирования числа содержит дешифратор 15, блоки элементов И 16.1 - 16.К, элемент ИЛИ 17. Количество информационных входов каждого блока элементов И 16.1 - 16.К равно длине одного слова идентификатора, а количество таких блоков равно максимально допустимому формату идентификатора. Дешифратор 15 преобразует двоичный код на своем входе .в позиционный на выходе таким обра- |зом, что разрешение на выдачу конк- 1ретного слова идентификатора появляется на входе соответствующего блока элементов И 16.1 - 16.К. Через элемент ИЛИ 17 соответствующее слово идентификатора поступает в блок 7 установки ключа.

Блок 7 установки ключа (фиг.7) предназначен для записи в счетчик 4 битов требуемого количества шагов деления и содержит счетный триггер 18, блоки элементов И 19 и 20 и элемент ИЛИ 21. В исходном состоянии сигналом с инверсного выхода триггера 18 разрешается запись в счетчик 4 числа, поступающего на входы блока элементов И 19, а после переключения триггера 18 - числа, сформированного в регистре 2 сдвига через открытые элементы И 20. Кроме того, после переключения триггера 18 выдается сигнал на переключение триггера 9. Счетчик 8 слов предназначен для задания количества циклов деления идентификатора на многочлен F(X).

Устройство работает следующим образом.

Идентификатор пользователя, для которого необходимо выработать маску, записывается в буферный регистр 1. При этом с блока 5 определения формата в счетчик 8 слов записывается число, определяющее формат данного идентификатора. По сигналу от счетчика 8 слов блок 6 формирования числа выбирает первое слово идентификатора из буферного регистра 1,которое посредством блока 7 установки ключа записывается в счетчик 4 битов Кроме того, сигналом с инверсного выхода триггера 9 элемент И 10.открыт, и выход последнего разряда бу- ферного регистра 1 подключен как к его входу, образуя кольцо, так и к , сумматору 3 по модулю два, а счетчики установлены в режим вычитания.При подаче тактовых импульсов в буферный регистр I счетчик 4 битов и регистр 2 сдвига устройства осуществляют деление идентификатора на полином F(x) в течение количества шагов , установленных в счетчике 4 битов. Как только счетчик 4 битов установится в нулевое состояние, по его сигналу в счетчике 8 слов уменьшится состояние на единицу и блок 6 формирования числа запишет через блок 7 установки ключа в счетчик 4 битов очередное слово идентификатора из буферного регистра 1. Процесс деления на полином F(x) продолжен. Деление идентификатора продолжается до тех пор, пока в счетчике 8 слов не установится нулевое состояние. Тогда с его выхода поступает сигнал разрешающий прохождение сигнала счета со счетчика 4 битов через элемент И 12. После деления идентификатора в соответствии со значением последнего его слова блок 7 установки осуществляет запись в счетчик 4 битов числа, полученного в регистре 2 сдви га, и процесс деления продолжается, iПосле повторного прохождения сигнала нулевого состояния из счетчика 4 битов через элемент И 12 на блок 7 установки ключа срабатывает триггер 9 и разрешает выдачу маски на выход устройства через открытый элемент ИИ.

Формула изобретения

Устройство для формирования маски, содержащее буферный регистр, счетчик битов, блок установки ключа, регистр сдвига, блок сумматоров по

5

0

модулю два, триггер и два элемента И, причем первый вход первого элемента И соединен с выходом младшего разряда данных буферного регистра, второй вход первого элемента И соединен с инверсным выходом триггера, прямой выход которого соединен с первым входом второго элемента И,второй

п вход которого соединен с выходом младшего разряда данных регистра сдвига и первым входом блока сумматоров по модулю два, второй вход которого соединен с выходом соответ5 ствующих разрядов данных регистра

i сдвига, последовательный информационный вход которого соединен с выходом блока сумматоров по модулю два, третий вход которого соединен с выходом

0 первого элемента И и последовательным информационным входом буферного регистра, параллельный информационный вход которого является входом идентификатора устройства, выход вто5 рого элемента И является выходом маски устройства, параллельный информационный выход регистра сдвига соединен с первым входом блока установки ключа, управляющий выход которого

0 соединен с входом триггера, а информационный выход - с информационным входом счетчика битов, о т л и ч а ю- щ е е с я тем, что, с целью повышения быстродействия, в него введены блок определения формата, блок формирования числа, счетчик слов и третий элемент И, причем параллельный информационный выход буферного регистра соединен с первым входом блока формирования числа и входом блока определения формата, выход которого соединен с информационным входом счетчика слов, информационный выход которого соединен с вторым входом блока

5 формирования числа, выход которого соединен с вторым входом блока установки числа, третий вход которого соединен с выходом третьего элемента И, первый вход которого соединен с

0 выходом переполнения счетчика слон, вход вычитания которого соединен с выходом переполнения счетчика битов и с вторым входом третьего элемента И.

ФигА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования маски | 1988 |

|

SU1513459A1 |

| Устройство для формирования маски | 1987 |

|

SU1451704A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Изобретение относится к вычислительной технике , предназначено для защиты от несанкционированного доступа к информации и может быть использовано для маскирования идентификации пользователей. Цель изобретения - повышение быстродействия. Устройство содержит буферный регистр 1, регистр 2 сдвига, блок сумматоров 3 по модулю два, счетчик 4 битов, блок 5 определения формата, блок 6 формирования числа, блок 7 установки ключа, счетчик 8 слев, триггер 9, первый 10, второй 11 и третий 12 элементы И. За счет блоков 5 и 6 и счетчика 8 в устройстве осуществляется разбиение маскируемого идентификатора на слова, сумма значений которых является кодом начального состояния. 4 ил.

| Мартин Дж | |||

| Вычислительные сети и распределенная обработка данных | |||

| Финансы и статистика | |||

| Вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - М., 1986, с | |||

| Русская печь | 1919 |

|

SU240A1 |

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Авторское свидетельство по заявке № 4378069/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-10-03—Подача