Изобретение относится к области автоматики И вычислительной техники и может быть использовано в устройствах отобрпл ения и преобразования данных, преимущественно в устройствах отображения графической информации на электронно-лучевых трубках (ЭЛТ). Известны аналоговые устройства (генераторы, интерполяторы) для формирования прямых линий на экране ЭЛТ ,1. Недостаток этих устройств заключается в том, что они имеют значительную погрешность выхода в заданную точку, которая увеличивается по мере увеличения длины линии. Известны также цифровые линейные ийтерполяторы на делителях частоты . Такие устройства обладают методической погрешностью выхода в заданную точку и значительно уступают аналоговым устройствам в быстродействии. Наиболее близким по технической сущности к предлагаемому техническому решению является цифровой линейный интерполятор 3, содержащий генератор тактовых импульсов, интеграторы, каждый из которых содержит приемный регистр, входы которого подключены ко входным информационным шинам интерполятора, и накапливающий сумматор, вход синхронизации которого соединен с одним из выходов генератора тактовых импульсов. Недостатком известного интерполятора является ограниченная скорость интерполирования линий. Сущность этого ограничения заключается в следующем. За время одного такта генератора тактовых импульсов на выходе каждого из двух интеграторов вырабатывается не более одного эле.ментарного приращения. Следовательно, предельно достижимая скорость И 1терполирования однозначно определяется максимально допустимой частотой /.ах следования тактовых импульсов, которая, в свою очередь, определяется разрядностью накапливающего сумматора и временем переключения применяемых логических элементов. Минимальное время, необходимое для интерполирования линии с п-разрядной (двоичной) проекцией на координатную ось X или у Для линии с 10-разрядной проекцией (характерной для графических устройств отображения на ЭЛТ) и при f .;, 2 Мгц (для 10-разрядного накапливающего сумматора, выполненного на базе интегральных микросхем серии 155)

;500 МКС,

ИНТ.

что в 5-10 раз превышает время построения линии аналоговыми методами.

Именно недостаточно высокое быстродействие ограничивало до настоящего времени применение этих илтерполяторов в графических устройствах отображе«ия на ЭЛТ.

Целью изобретения является повышение быстродействия интерполятора. Указанная цель достигается в интерлоляторе тем, что он содержит блок элементов ИЛИ, входы которого подключены к выходам приемных регистров интеграторов, блок фиксации заг{ятой, вход которого соединены с выходами блока элементов ИЛИ, блок установки нуля и дешифратор, входы которых подключены к выходам блока фиксации запятой, вход синхронизации блока установки нуля соединен с другим выходом генератора тактовых импульсов, а выходы - с установочными Входами сумматоров, причем в каждый из интеграторов введены блок формирования приращений координат И блок параллельного сдвига информации, информационные входы которого подключены к выходам приемного регистра, управляющие входы - ко входным управляющим шинам интерполятора, а выходы - к информационным входам сумматора, выходы которого соединены через блок формирования приращений координат с выходами интерполятора, а управляющие входы блока формирования приращений координат подключены к выходам дешифратора.

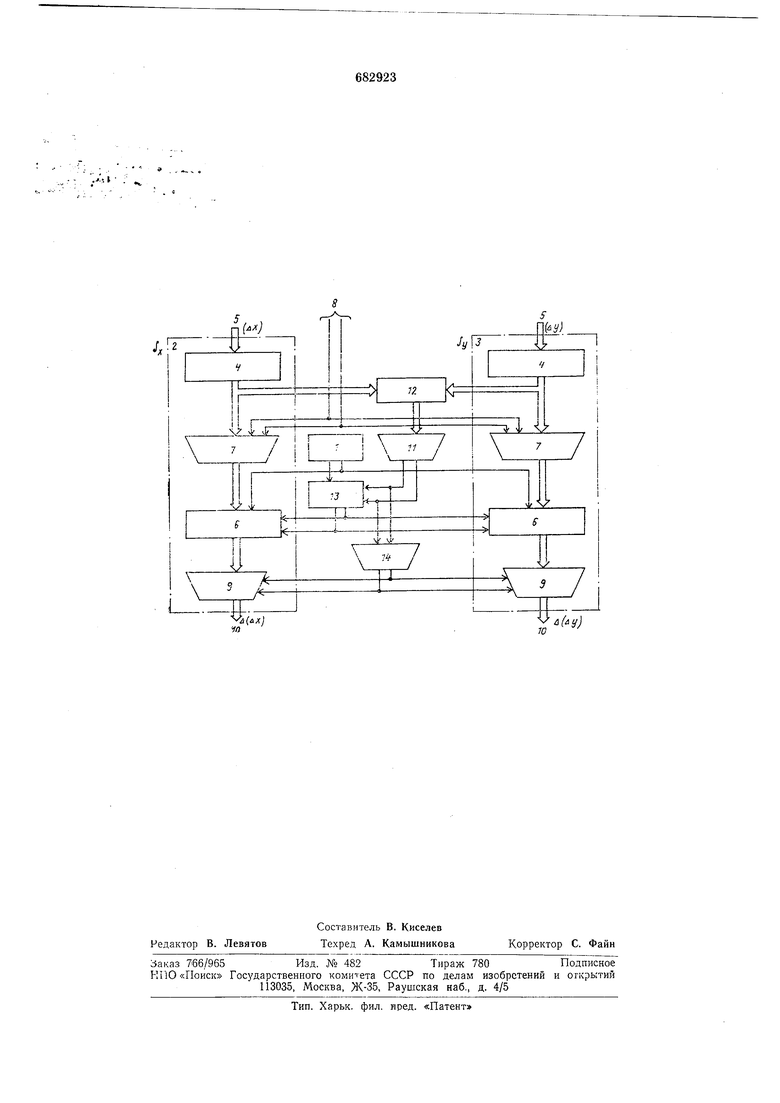

На чертеже представлена блок-схема предлагаемого интерполятора.

Он состоит из генератора / тактовых импульсов, интегратора 2 приращений по координате X И полностью идентичного ему по структуре и связям интегратора 3 приращений по координате у. Каждый интегратор содержит приемный регистр 4, входы которого подключены ко входным информационным шинам 5, и накапливающий сумматор 6, вход синхронизации которого подключен к одному из выходов генератора / тактовых импульсов, блок 7 параллельного сдвига информации, информационные входы которого подключены к выходам приемного регистра 4, управляющие входы - ко входным управляющим шинам 8, а выходы-к информационным входам накапливающего сумматора 6, и блок 9 формирования приращений координат, информационные входы которого подключены к входам сумматора , а выходы - к выходным информационным шинам W. В состав интерполятора включены также блок // фиксации запятой, блок 12 элементов ИЛИ, первые входы которого подключены поразрядно квыходам приемного {эегистра 4 интегратора 2, вторые входы - к соответствующим выходаМ приемного регистра 4 интегратора 3, а выходы соединены со входами блока 11 фиксации запятой, блок 13 установки нуля, выходы которого подключены поразрядно ко входам установки «О старших (слева от запятой) разрядов сумматора 6, а вход синхронизации - к другому выходу генератора /, и дешифратор 14, входы которого соединены со входами блока 13 установки нуля и с выходами блока фиксации запятой.

Интерполятор работает следующим образом.

В исходном состоянии в регистрах 4 - «нулевые коды, запятая фиксирована перед младшим разрядом (нет ни одного разряда, равного «1), все разряды накопительных сумматоров 6 установлены в «О, на выходные Шины 10 информация не поступает. Генератор / тактовых импульсов вырабатывает две серии сдвинутых во времени тактовых импульсов, из которых подтверждает состояние интеграторов 2 и 5.

Коды координатных приращений Дд; и Аг/ со входных информационных шин 5 заносятся в приемные регистры 4 интеграторов 2 и 5 соответственно. С выходов регистров через логический блок 12 дизъюнкция этих кодов поступает на входы блока // фиксации запятой, который выделяет самый старший, равный логический «1

разряд кода дизъюнкции. Сигнал этого разряда с выхода блока // через блок установки нуля 13 подготавливает условия для сброса разрядов переполнения сумматоров 6, а через дешифратор М и блоки 9 формирования приращений координат осуществляет логическое подключение k разрядов нереполнения каждого сумматора 6 к выходным шинам 10. Кроме того, код с выходом приемного регистра 4 каждого интегратора, сдвинутый с помощью блока 7 на i разрядов (О f ) в сторону старшего разряда, поступает на входы накапливающего сумматора 6.

В первом полутакте по тактовому импульсу от генератора / выполняется суммирование суммы и выдача содержимого k разрядов переполнения каждого сумматора в виде малых приращений координат Д(Д.с) и Д(Дг/) на выходные шины 10.

Во втором полутакте через блок 13 установки нуля выполняется «обнуление разрядов переполнения сумматоров.

Затем в следующем полутакте опять выполняется суммирование содержимого

сумматоров 6 с кодами на их входах, запоминание новой суммы, выдача очередных выходных приращений Д(Дл;) и Д(Дг/) и т. д. Последовательность операций циклически повторяется до получения сигнала

конца интерполяции, о чем свидетельствует занесение «нулевого кода на приемные регистры 4, после чего интерполятор переходит в исходное состояние. Максимальная разрядность формируемых в каждом такте малых приращений равна i-fl и, следовательно, однозначно определяется разрядностью сдвига входных приращений в 7-параллельного сдвига информации, которая, в свою очередь, задается кодом на управляющих щинах 8 что позволяет программно изменять скорость интерполяции за счет изменения разрядности выходного приращения. Применение предлагаемого интерполятора в графических устройствах отображения на ЭЛТ предполагает формирование промежуточных точек отрезков, задаваемых малыми приращениями, с помощью аналоговых формирователей. При этом погрещность формирования линии не превыщает погрещности обработки одного выходного приращения и не зависит от полной длины линии, задаваемой входными приращениями координат Ал: и Дг/. Следовательно предлагаемый интерполятор позволяет резко увеличить скорость интерполяции и дает возможность выбора оптимального соотнощения между скоростью интерполяции и допустимой точностью обработки линии при обеспечении выхода в заданную точку без .погрещности. Формула изо б ре тения Цифровой линейный интерполятор, содержащий генератор тактовых импульсов, интеграторы, каждый из которых содержит приемный регистр, входы которого подключены ко входным информационным щинам интерполятора, и накапливающий сумматор, вход синхронизации которого соединен с одним из выходов генератора тактовых импульсов, отличающийся тем, что, с целью повышения быстродействия интерполятора, он содержит блок элементов ИЛИ, входы которого подключены к выходам приемных регистров интеграторов, блок фиксации запятой, входы которого соединены с выходами блока элементов ИЛИ, блок установки нуля и дещифратор, входы которых подключены к выходам блока фиксации запятой, вход синхронизации блока установки нуля соединен с другим выходом генератора тактовых импульсов, а выходы- с установочными входами сумматоров, причем в каждый из интеграторов введены блок формирования приращений координат и блок параллельного сдвига информации, информационные входы которого подключены к выходам приемного регистра, управляющие входы - ко входным управляющим щинам интерполятора, а выходы- к информационным входам сумматора, выходы которого соединены через блок формирования приращений координат с выходами интерполятора, а управляющие входы блока формирования приращений координат подключены к выходам дещифратора. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 424177, кл. G 06 G 7/30, 1973. 2.Авторское свидетельство СССР Хе 395839, кл. G 06 К 15/20, 1972. 3.Карибский В. В. и Черныщев А. В. Цифровые интерполяторы для систем программного управления. М., «Мащиностроение, 1962, с. 10--13.

| название | год | авторы | номер документа |

|---|---|---|---|

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки (элт) | 1980 |

|

SU951378A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1990 |

|

SU1777168A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Устройство для формирования векто-POB HA эКРАНЕ элТ | 1978 |

|

SU807362A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

Авторы

Даты

1979-08-30—Публикация

1977-04-04—Подача