Изобретение относится к области автоматики и вычислительной техники и предназначено для использования, например, в системах числового управления станками и другим технологическим оборудованием.

Цель изобретения - повышение быстродействия путем сокращения времени расчета приращений на участках с постоянной контурной скоростью.

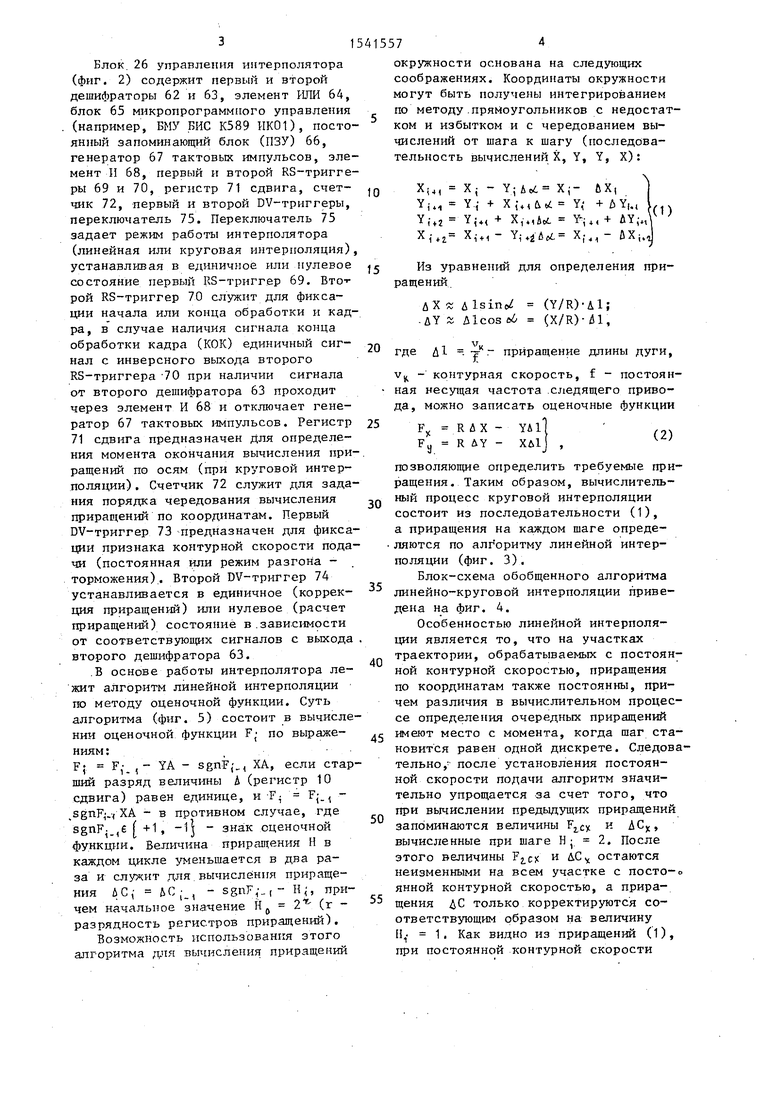

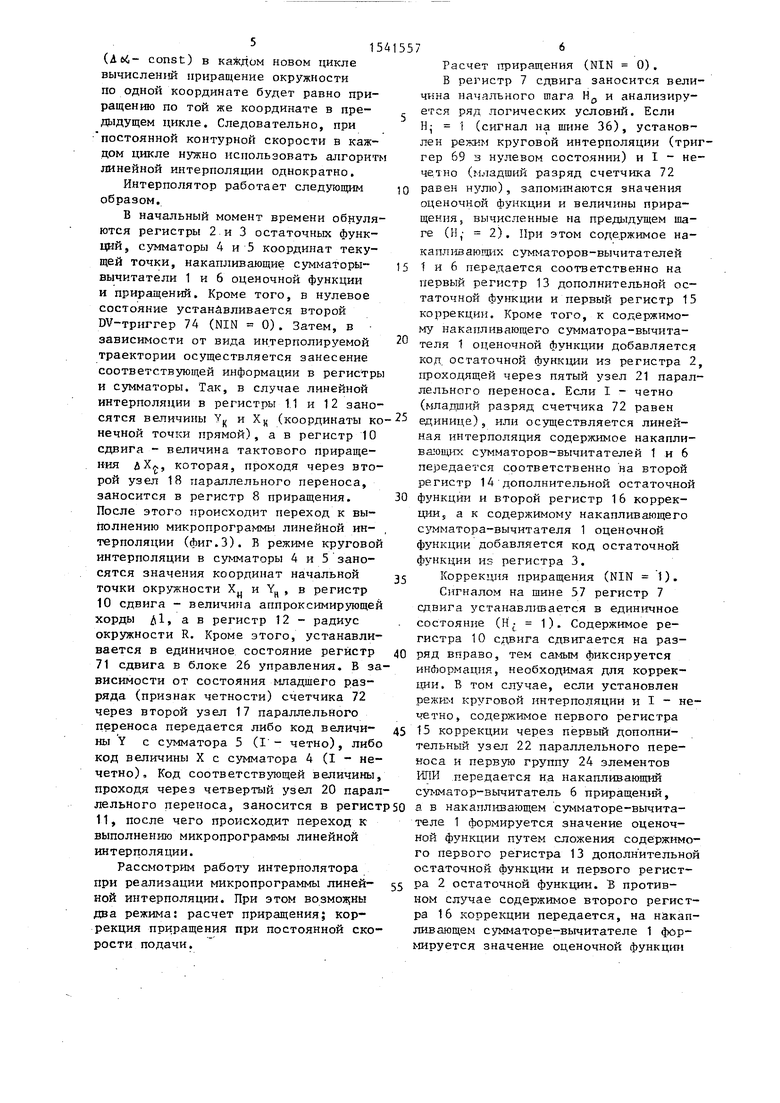

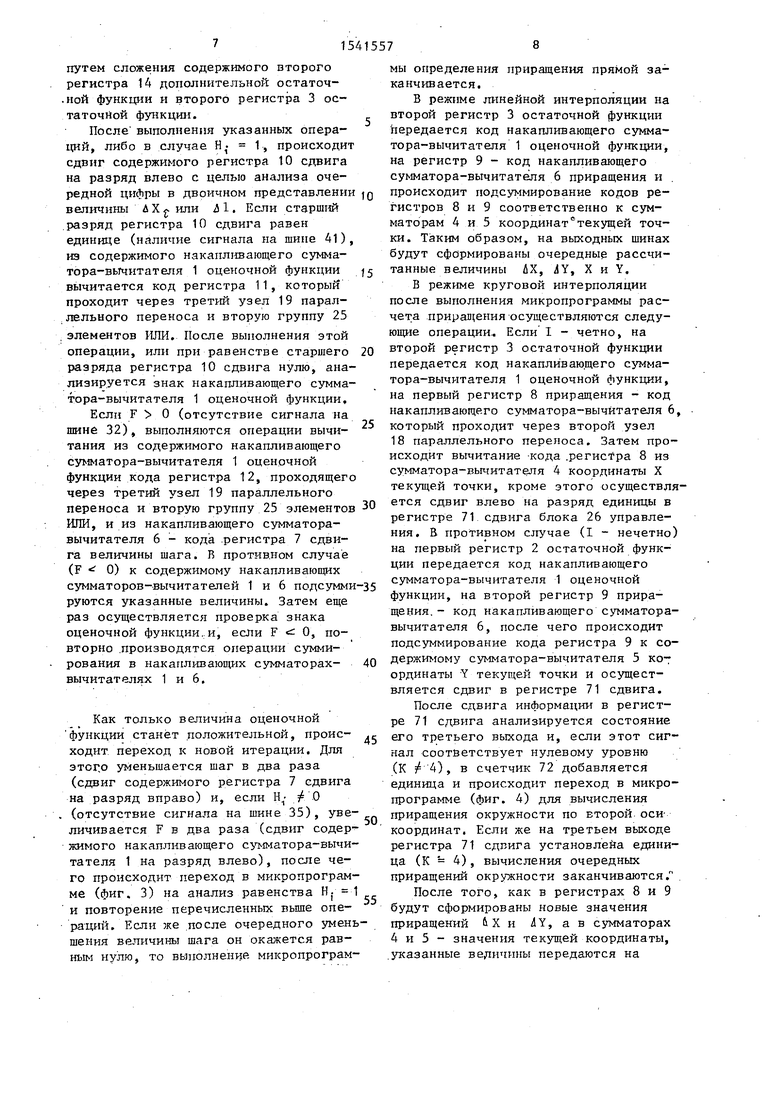

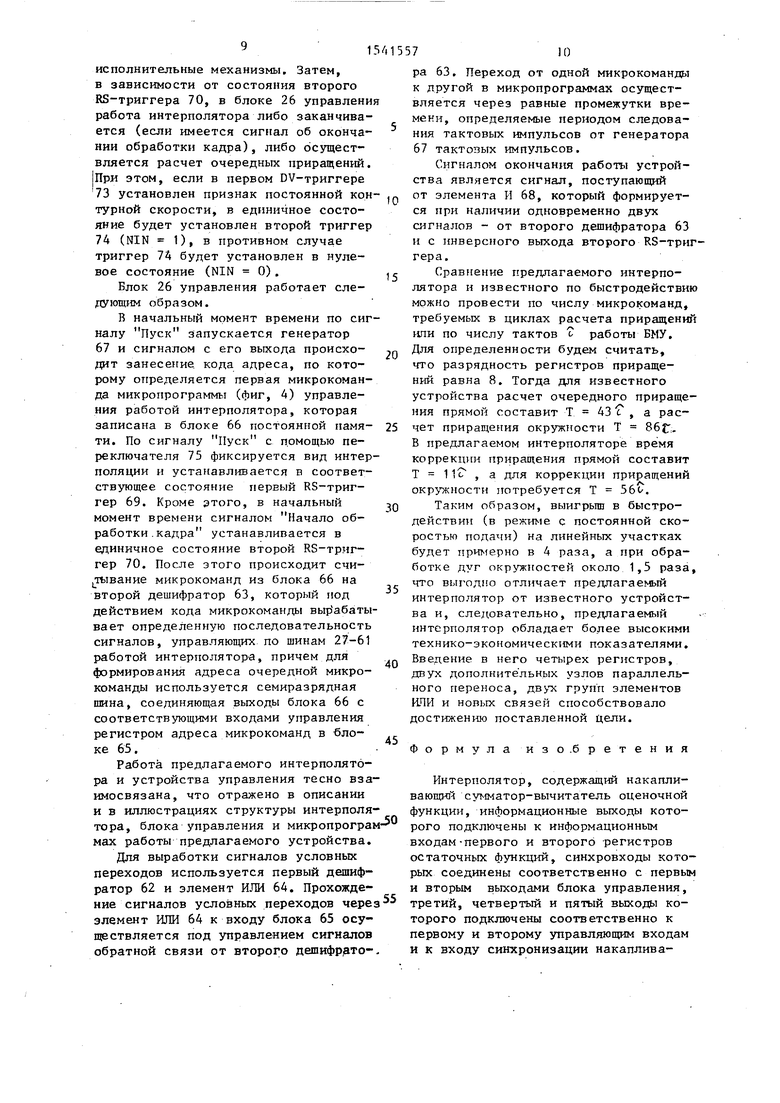

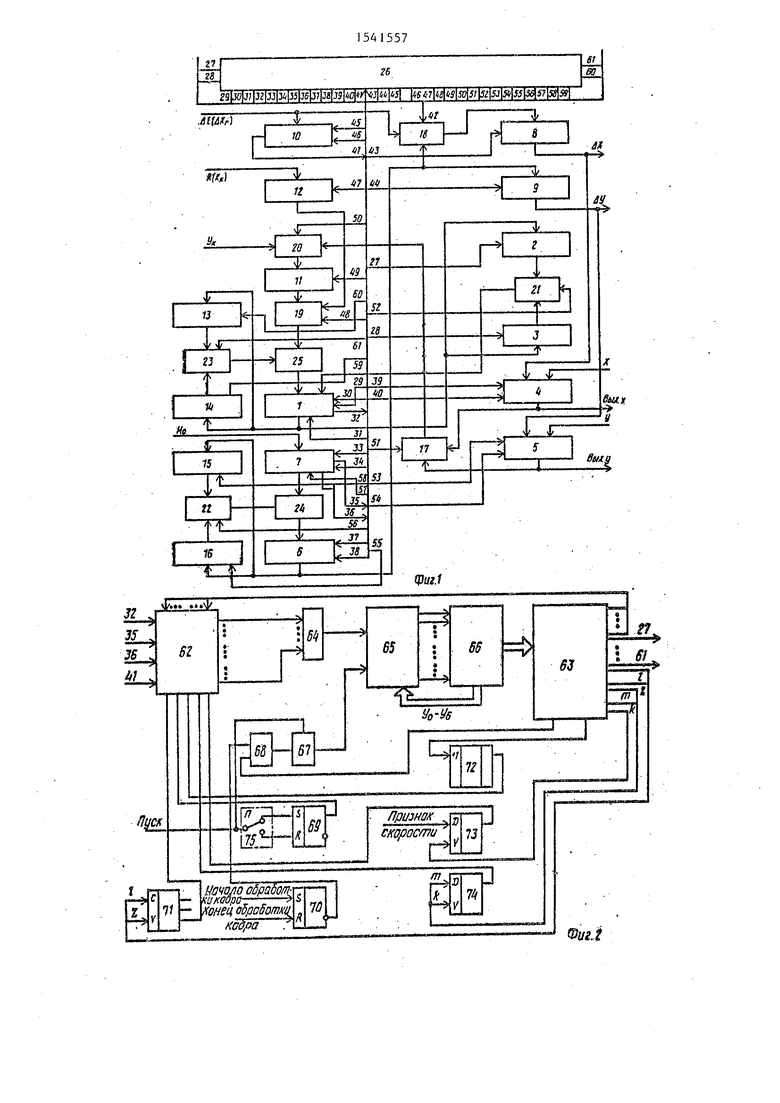

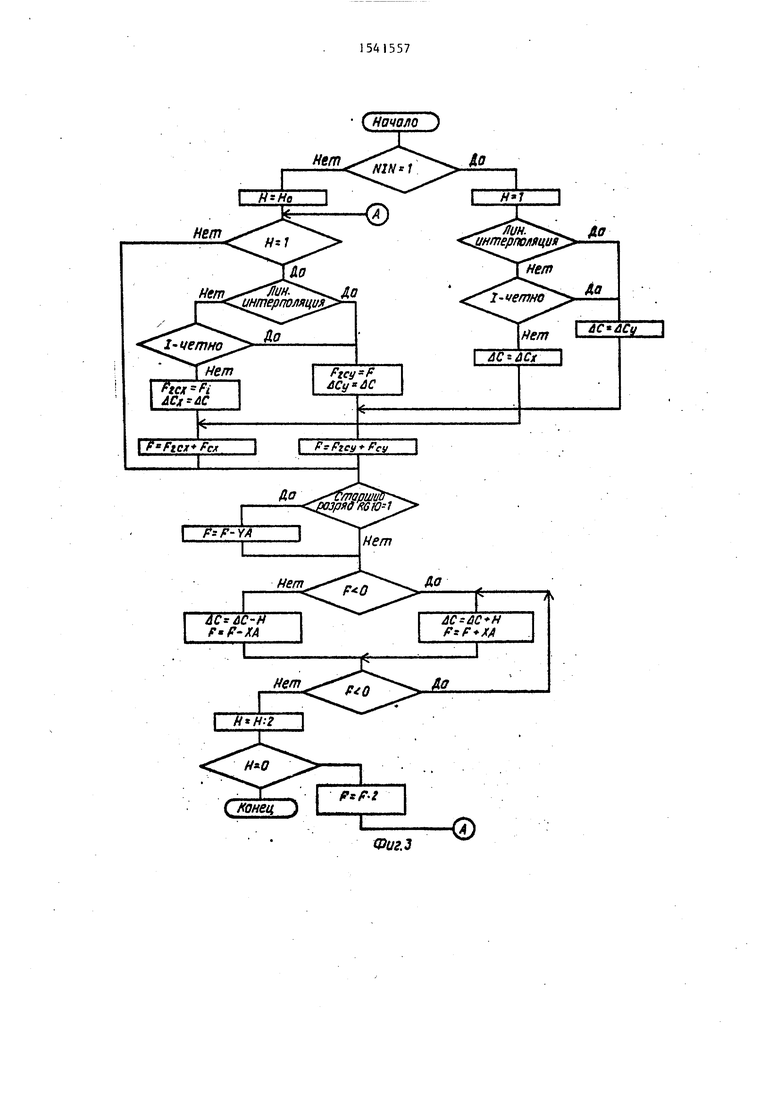

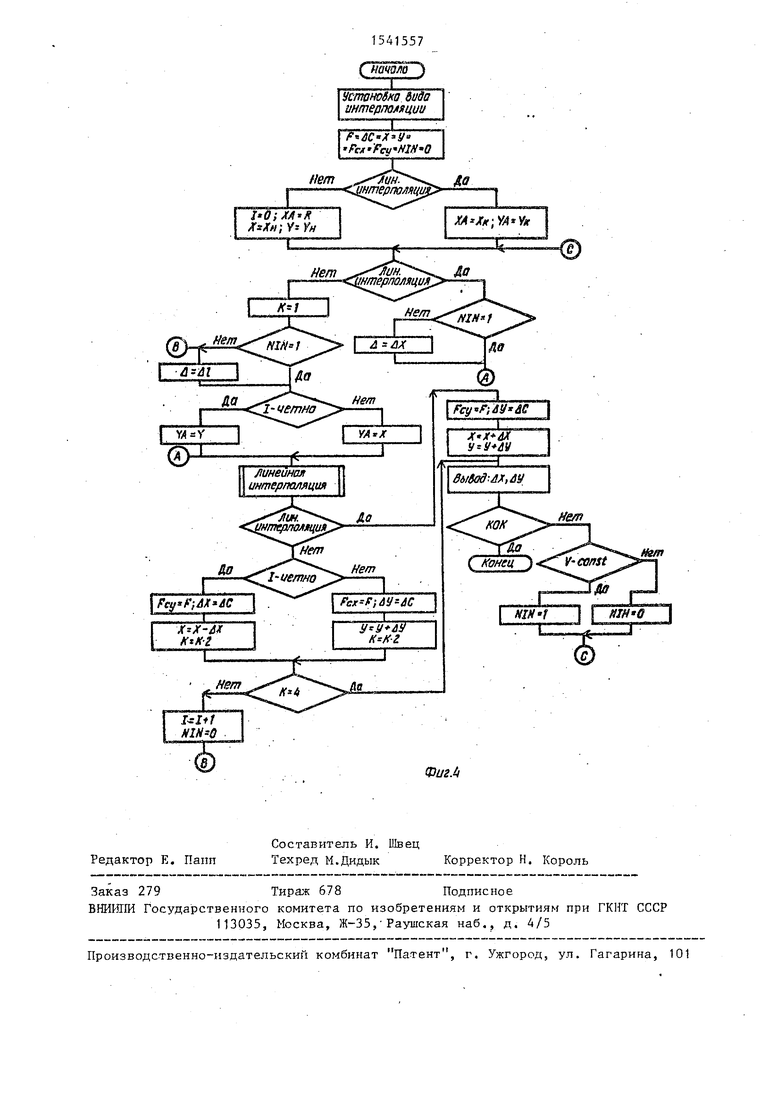

На фиг. 1 приведена структурная схема интерполятора; на фиг. 2 - блок-схема блока управления; на фиг. 3 и 4 - алгоритмы работы интерполятора и блока управления.

Интерполятор (фиг. 1) содержит накапливающий сумматор-вычитатель. 1 оценочной функции, первый и второй регистры 2 и 3 остаточных функций, первый и второй накапливающие сумма- (торы-вычитатёли 4 и 5 координат

текущей точки, накапливающий сумматор-вычитатель 6 приращений, регистр 7 сдвига величины шага, первый и второй регистры 8 и 9 приращений, третий регистр 10 сдвига приращений, имеющ.чй дополнительный (старший) разряд, регистр 11 координаты конечной точки, регистр 12 радиуса окружности, первый и второй регистры 13 и 14 дополнительных остаточных функций, первый и второй регистры 15 и 16 коррекции, первый, второй, третий, четвертый и пятый узлы 17-21

шараллельного переноса, первый и второй дополнительные узлы 22 и 23 параллельного переноса, которые представля. ют собой стандартные схемы мультиплексоров на два входа, первую и вторую группы 24 и 25 элементов ИЛИ, блок 26 управления, входы и выходы 27-61 блока управления.

О1

м

СП

сл

J

«&,

31

Блок 26 управления интерполятора (фиг. 2) содержит первый и второй дешифраторы 62 и 63, элемент ИЛИ 64, блок 65 микропрограммного управления (например, БМУ БИС К589 1IK01), постоянный запоминающий блок (ПЗУ) 66, генератор 67 тактовых импульсов, элемент И 68, первый и второй RS-тригге- ры 69 и 70, регистр 71 сдвига, счетчик 72, первый и второй DV-триггеры, переключатель 75. Переключатель 75 задает режим работы интерполятора (линейная или круговая интерполяция), устанавливая в единичное или нулевое состояние первый RS-триггер 69. рой RS-триггер 70 служит для фиксации начала или конца обработки и кад

ра, в случае наличия сигнала конца обработки кадра (КОК) единичный сигнал с инверсного выхода второго RS-триггера 70 при наличии сигнала от второго дешифратора 63 проходит через элемент И 68 и отключает генератор 67 тактовых импульсов. Регистр 71 сдвига предназначен для определения момента окончания вычисления приращений по осям (при круговой интерполяции) . Счетчик 72 служит для задания порядка чередования вычисления приращений по координатам. Первый DV-триггер 73 предназначен для фиксации признака контурной скорости подачи (постоянная или режим разгона - торможения). Второй DV-триггер 74 устанавливается в единичное (коррекция приращений) или нулевое (расчет приращений) состояние в зависимости от соответствующих сигналов с выхода второго дешифратора 63.

В основе работы интерполятора лежит алгоритм линейной интерполяции по методу оценочной функции. Суть алгоритма (фиг. 5) состоит в вычислении оценочной функции Ft- по выражениям:

F F{. YA - sgnF;, XA, если старший разряд величины Д (регистр 10 сдвига) равен единице, и F;, - .sgnF.j XA - в противном случае, где sgnF,Ј +1, -1j - знак оценочной функции. Величина приращения Н в каждом цикле уменьшается в два раза и служит для вычисления приращения ДС,- АС;, - sgnF ,,,- , причем начальное значение Н0 (г - разрядность регистров приращений).

Возможность использования этого алгоритма для вычисления приращений

окружности основана на следующих соображениях. Координаты окружности могут быть получены интегрированием по методу прямоугольников с недостатком и избытком и с чередованием вычислений от шага к шагу (последовательность вычислений X, Y, Y, X):

Х;4( Xj - У;Де6- Х( 6Х|

Yit1 Y,- + Х,%,& Y,- + UY,.,

Y;tZ YiM + Х,„4Л Y-j.+ AY;.,1

i i + 1 Y, Ј и oi. X j 41 - u X ;,

(D

Из уравнений для определения приращений

д X я Д IsiW (Y/R)-Al; AY X. Alcos eЈ (X/R)-41,

где Д1 . - приращение длины дуги,

v - контурная скорость, f - постоянная несущая частота следящего привода, можно записать оценочные функции

Fx R Д X YA1 R UY - Х&1

(2)

0

5

0

5

0

5

позволяющие определить требуемые приращения. Таким образом, вычислительный процесс круговой интерполяции состоит из последовательности (1), а приращения на каждом шаге опреде- ляются по алгоритму линейной интерполяции (фиг. 3).

Блок-схема обобщенного алгоритма линейно-круговой интерполяции приведена на фиг. 4.

Особенностью линейной интерполяции является то, что на участках траектории, обрабатываемых с постоянной контурной скоростью, приращения по координатам также постоянны, причем различия в вычислительном процессе определения очередных приращений имеют место с момента, когда шаг становится равен одной дискрете. Следовательно, после установления постоянной скорости подачи алгоритм значительно упрощается за счет того, что при вычислении предыдущих приращений запоминаются величины FlCX и АСХ, вычисленные при шаге Н; 2. После этого величины FiCx и ДСЧ остаются неизменными на всем участке с посто-о янной контурной скоростью, а приращения ДС только корректируются соответствующим образом на величину Н,. 1. Как видно из приращений (1), при постоянной контурной скорости

5154

(A&i- const) в каждом новом цикле вычислений приращение окружности по одной координате будет равно приращению по той же координате в предыдущем цикле. Следовательно, при постоянной контурной скорости в каждом цикле нужно использовать алгоритм линейной интерполяции однократно.

Интерполятор работает следующим образом.

В начальный момент времени обнуляются регистры 2 и 3 остаточных функций, сумматоры 4 и 5 координат текущей точки, накапливающие сумматоры- вычитатели 1 и 6 оценочной функции и приращений. Кроме того, в нулевое состояние устанавливается второй DV-триггер 74 (NIN 0). Затем, в зависимости от вида интерполируемой траектории осуществляется занесение соответствующей информации в регистры и сумматоры. Так, в случае линейной интерполяции в регистры 11 и 12 заносятся величины YJ, и Хц (координаты ко нечной точки прямой), а в регистр 10 сдвига - величина тактового приращения йХр, которая, проходя через второй узел 18 параллельного переноса, заносится в регистр 8 приращения. После этого происходит переход к выполнению микропрограммы линейной интерполяции (фиг.З). В режиме круговой интерполяции в сумматоры 4 и 5 заносятся значения координат начальной точки окружности Х„ и Y№ , в регистр 10 сдвига - величина аппроксимирующей хорды Д1, а в регистр 12 - радиус окружности R. Кроме этого, устанавливается в единичное состояние регистр 71 сдвига в блоке 26 управления. В зависимости от состояния младшего разряда (признак четности) счетчика 72 через второй узел 17 параллельного переноса передается либо код величи- ны Y с сумматора 5(1- четно), либо код величины X с сумматора 4 (I - нечетно), Код соответствующей величины, проходя через четвертый узел 20 параллельного переноса, заносится в регист 11, после чего происходит переход к выполнению микропрограммы линейной интерполяции.

Рассмотрим работу интерполятора при реализации микропрограммы линей- ной интерполяции. При этом возможны два режима: расчет приращения; коррекция приращения при постоянной скорости подачи.

76

Расчет приращения (NIN 0).

В регистр 7 сдвига заносится величина начального шага Н0 и анализируется ряд логических условий. Если Н- i (сигнал на шине 36), установлен режим круговой интерполяции (тригер 69 з нулевом состоянии) и I нечетно (младший разряд счетчика 72 равен нулю), запоминаются значения оценочной функции и величины приращения, вычисленные на предыдущем шаге (Н,- 2). При этом содержимое накапливающих сумматоров-вычитателей 1 и 6 передается соответственно на первый регистр 13 дополнительной остаточной функции и первый регистр 15 коррекции. Кроме того, к содержимому накапливающего сумматора-вычита- теля 1 оценочной функции добавляется код остаточной функции из регистра 2 проходящей через пятый узел 21 параллельного переноса. Если I - четно (младший разряд счетчика 72 равен единице), или осуществляется линейная интерполяция содержимое накапливающих сумматоров-вычитателей 1 и 6 передается соответственно на второй регистр 14 дополнительной остаточной функции и второй регистр 16 коррекции, а к содержимому накапливающего сумматора-вычитателя 1 оценочной функции добавляется код остаточной функции из регистра 3.

Коррекция приращения (NIN 1).

Сигналом на шине 57 регистр 7 сдвига устанавливается в единичное состояние (Н; 1). Содержимое регистра 10 сдвига сдвигается на разряд вправо, тем самым фиксируется информация, необходимая для коррекции. В том случае, если установлен режим круговой интерполяции и I - нечетно, содержимое первого регистра 15 коррекции через первый дополнительный узел 22 параллельного переноса и первую группу 24 элементов ИЛИ передается на накапливающий сумматор-вычитатель 6 приращений, а в накапливающем сумматоре-вычита- теле 1 формируется значение оценочной функции путем сложения содержимого первого регистра 13 дополнительно остаточной функции и первого регистра 2 остаточной функции. В противном случае содержимое второго регистра 16 коррекции передается, на накапливающем сумматоре-вычитателе 1 формируется значение оценочной функции

путем сложения содержимого второго регистра 14 дополнительной остаточ- .ной функции и второго регистра 3 остаточной функции.

После выполнения указанных операций, либо в случае Н. 1, происходит сдвиг содержимого регистра 10 сдвига на разряд влево с целью анализа очередной цифры в двоичном представлении величины Д X или Л I. Если старший разряд регистра 10 сдвига равен единице (наличие сигнала на шине 41), из содержимого накапливающего сумматора-вычитателя 1 оценочной функции вычитается код регистра 11, который проходит через третий узел 19 параллельного переноса и вторую группу 25 элементов ИЛИ. После выполнения этой операции, или при равенстве старшего разряда регистра 10 сдвига нулю, анализируется знак накапливающего сумматора-вычитателя 1 оценочной функции.

Если F 0 (отсутствие сигнала на шине 32), выполняются операции вычитания из содержимого накапливающего сумматора-вычитателя 1 оценочной функции кода регистра 12, проходящего через третий узел 19 параллельного переноса и вторую группу 25 элементов ИЛИ, и из накапливающего сумматора- вычитателя 6 - кода регистра 7 сдвига величины шага. R противном случае (F 0) к содержимому накапливающих сумматоров-вычитателей 1 и 6 подсумми руются указанные величины. Затем еще раз осуществляется проверка знака оценочной функции и, если F « 0, повторно производятся операции суммирования в накапливающих сумматорах- вычитателях 1 и 6.

Как только величина оценочной функции станет положительной, проис- .,- ходит переход к новой итерации. Для этого уменьшается шаг в два раза (сдвиг содержимого регистра 7 сдвига на разряд вправо) и, если Н.,- О (отсутствие сигнала на шине 35), увеличивается F в два раза (сдвиг содержимого накапливающего сумматора-вычитателя 1 на разряд влево), после чего происходит переход в микропрограмме (Фиг. 3) на анализ равенства Н, 1

55

и повторение перечисленных выше операций. Если же после очередного уменьшения величины шага он окажется равным нулю, то выполнение микропрограм50

0 5 0

,-

5

0

мы определения приращения прямой заканчивается.

В режиме линейной интерполяции на второй регистр 3 остаточной функции передается код накапливающего сумматора-вычитателя 1 оценочной функции, на регистр 9 - код накапливающего сумматора-вычитателя 6 приращения и происходит подсуммирование кодов регистров 8 и 9 соответственно к сумматорам 4 и 5 координат текущей точки. Таким образом, на выходных шинах будут сформированы очередные рассчитанные величины АХ, 4Y, X и Y.

В режиме круговой интерполяции после выполнения микропрограммы расчета приращения осуществляются следующие операции. Если I - четно, на второй регистр 3 остаточной функции передается код накапливающего сумматора-вычитателя 1 оценочной функции, на первый регистр 8 приращения - код накапливающего сумматора-вычитателя 6, который проходит через второй узел 18 параллельного переноса. Затем происходит вычитание кода регистра 8 из сумматора-вычитателя 4 координаты X текущей точки, кроме этого осуществляется сдвиг влево на разряд единицы в регистре 71 сдвига блока 26 управления. В противном случае (I - нечетно) на первый регистр 2 остаточной функции передается код накапливающего сумматора-вычитателя 1 оценочной функции, на второй регистр 9 приращения - код накапливающего сумматора- вычитателя 6, после чего происходит подсуммирование кода регистра 9 к содержимому сумматора-вычитателя 5 координаты Y текущей точки и осуществляется сдвиг в регистре 71 сдвига.

После сдвига информации в регистре 71 сдвига анализируется состояние его третьего выхода и, если этот сигнал соответствует нулевому уровню (К 4), в счетчик 72 добавляется единица и происходит переход в микропрограмме (фиг. 4) для вычисления приращения окружности по второй оси координат. Если же на третьем выходе регистра 71 сдвига установлена единица (К 4), вычисления очередных приращений окружности заканчиваются.

После того, как в регистрах 8 и 9 будут сформированы новые значения приращений Ь X и 4Y, а в сумматорах 4 и 5 - значения текущей координаты, указанные величины передаются на

исполнительные механизмы. Затем, в зависимости от состояния второго RS-триггера 70, в блоке 26 управлени работа интерполятора либо заканчивается (если имеется сигнал об окончании обработки кадра), либо осуществляется расчет очередных приращений. При этом, если в первом DV-триггере

73установлен признак постоянной контурной скорости, в единичное состояние будет установлен второй триггер

74(NIN 1), в противном случае триггер 74 будет установлен в нулевое состояние (NIN 0).

Блок 26 управления работает следующим образом.

В начальный момент времени по сигналу Пуск запускается генератор 67 и сигналом с его выхода происходит занесение кода адреса, по которому определяется первая микрокоманда микропрограммы (фиг, 4) управления работой интерполятора, которая записана в блоке 66 постоянной памяти. По сигналу Пуск с помощью переключателя 75 фиксируется вид интерполяции и устанавливается в соответствующее состояние первый RS-триг- гер 69. Кроме этого, в начальный момент времени сигналом Начало обработки кадра устанавливается в единичное состояние второй RS-трчг- гер 70. После этого происходит счи- тывание микрокоманд из блока 66 на второй дешифратор 63, который под действием кода микрокоманды вырабатывает определенную последовательность сигналов, управляющих по шинам 27-61 работой интерполятора, причем для формирования адреса очередной микрокоманды используется семиразрядная шина, соединяющая выходы блока 66 с соответствующими входами управления регистром адреса микрокоманд в блоке 65.

Работа предлагаемого интерполятора и устройства управления тесно взаимосвязана, что отражено в описании и в иллюстрациях структуры интерполятора, блока управления и микропрогра мах работы предлагаемого устройства.

Для выработки сигналов условных переходов используется первый дешифратор 62 и элемент ИЛИ 64. Прохождение сигналов условных переходов чере элемент ИЛИ 64 к входу блока 65 осуществляется под управлением сигналов обратной связи от второго дешифрдто

155710

ра 63. Переход от одной микрокоманды к другой в микропрограммах осуществляется через равные промежутки времени, определяемые периодом следования тактовых импульсов от генератора 67 тактовых импульсов.

Сигналом окончания работы устрой

10

15

20

25

30

35

0

5

0

5

ства является сигнал, поступающий от элемента II 68, который формируется при наличии одновременно двух сигналов - от второго дешифратора 63 и с инверсного выхода второго RS-триггера.

Сравнение предлагаемого интерполятора и известного по быстродействию можно провести по числу микрокоманд, требуемых в циклах расчета приращений или по числу тактов Ј работы БМУ. Для определенности будем считать, что разрядность регистров приращений равна 8. Тогда для известного устройства расчет очередного приращения прямой составит Т 43 с , а расчет приращения окружности Т 8бЈ. В предлагаемом интерполяторе время коррекции приращения прямой составит Т 110s , а для коррекции приращений окружности потребуется Т 56с/.

Таким образом, выигрыш в быстродействии (в режиме с постоянной скоростью подачи) на линейных участках будет примерно в 4 раза, а при обработке дуг окружностей около 1,5 раза, что выгодно отличает предлагаемый интерполятор от известного устройства и, следовательно, предлагаемый интерполятор обладает более высокими технико-экономическими показателями. Введение в него четырех регистров, двух дополнительных узлов параллельного переноса, двух групп элементов ИЛИ и новых связей способствовало достижению поставленной Цели.

Формула изобретения

Интерполятор, содержащий накапливающий сумматор-вычитатель оценочной функции, информационные выходы которого подключены к информационным входам-первого и второго регистров остаточных функций, синхровходы которых соединены соответственно с первым и вторым выходами блока управления, третий, четвертый и пятый выходы которого подключены соответственно к первому и второму управляющим входам и к входу синхронизации накаплива

ющего сумматора-вычитателя оценочной функции, выход старшего разряда которого соединен с первым входом блока управления, шестой и седьмой выходы которого соединены соответственно с входом синхронизации и управляющим входом регистра сдвига величины шага информационные входы которого подключены к шине ввода величины начального шага, выходы двух младших разрядо подключены соответственно к второму и третьему входам блока управления, восьмой и девятый выходы которого соединены соответственно с входом синхронизации и управляющим входом накапливающего сумматора-вычитателя приращений, десятый и одиннадцатый выходы подключены соответственно к входу синхронизации и к управляющему входу первого накапливающего сумматора координаты текущей точки, первая группа информационных входов соединена с шиной ввода величины X, вторая группа информационных входов которого подключена к объединенным между собой выходной шине величины АХ и информационным выходам первого регистра приращений, информационные выходы накапливающего сумматора коор- динат текущей точки подключены к объединенным между собой первой группе входов первого узла параллельного переноса и выходной шине величины X, выходная шина величины Y объединена соответствующим образом с второй группой входов первого узла параллельного переноса и подключена к информационным выходам второго накапли1 вающего сумматора координаты текущей точки, первая группа информационных входов которого соединена с шиной ввода величины Y, вторая группа информационных входов - с объединенными между собой выходной шиной величины AY и информационными выходами второго регистра приращений, информационные входы которого объединены с первой группой входов второго узла параллельного переноса и подключены к информационным выходам накапливав ющего сумматора-вычитателя приращений вторая группа входов второго узла параллельного переноса подключена к объединенным между собой шине ввода величины &1(ДХ) и информационным вхо- дам третьего регистра сдвига ириращений, выход старшего разряда которого соединен с четвертым входом блока уп

10

15

20

25

зо

5

0

5

0

равления, двенадцатый выход которого подключен к упраляющему входу второго узла параллельного переноса, выходы которого соединены с информационными входами первого регистра приращений, синхровход которого подключен к тринадцатому выходу блока управления, четырнадцатый выход которого подключен к входу синхронизации второго регистра приращений, пятнадцатый и шестнадцатый выходы подключены соответственно к входу синхронизации и к входу управления третьего регистра сдвига приращения, шина ввода величины Y подключена к информационным входам регистра радиуса окружности, синхро- вход которого соединен с семнадцатым выходом блока управления, а информационные выходы подключены к первой группе входов третьего узла параллельного переноса, управляющий вход которого соединен с восемнадцатым выходом блока управления, вторая группа входов соединена с информационными выходами регистра координаты конечной точки, вход синхронизации которого соединен с девятнадцатым выходом блока управления, а информационные входы подключены к выходам четвертого узла параллельного переноса, первая группа входов которого соединена с шиной ввода величины Yh, управляющий вход подключен к восемнадцатому выходу блока управления, вторая группа входов соединена с соответствующими выходами первого узла параллельного переноса, управляющий вход которого подключен к девятнадцатому входу блока управления, двадцатый выход которого подключен к управляющему входу пятого узла параллельного переноса, первая и вторая группы входов которого соединены с информационными выходами соответственно первого и второго регистров остаточных функций, выходы подключены к первой группе информационных входов накапливающего сумматора-вычитателя оценочной функции, причем двадцать первый и двадцать второй выходы блока управления соединены соответственно с входом синхронизации и с управляющим входом второго накапливающего сумматора координаты текущей точки, отличающийся тем, что, с целью повышения его быстродействия путем сокращения времени расчета приращений на участках с постоянной контурной скоростью, введены дополнительные первый и второй узлы параллельного переноса, первая и вторая группы элементов ИЛИ, первый и второй регистры дополнительных остаточных функций, первый и второй регистры коррекции, управляющий вход второго регистра корекции соединен с двадцать третьим выходом блока управления, а информа- ционные входы, объединенные с информационными входами первого регистра коррекции, подключены к информационным входам накапливающего сумматора- вычитателя приращений, информацией- ные выходы второго регистра коррекции соединены с первой группой входо первого дополнительного узла параллельного переноса, вторая группа входов которого соединена с информа- ционными выходами первого регистра коррекции, управляющий вход которой подключен к двадцать четвертому выходу блока управления, а выходы соединены с первой группой входов пер- вой группы элементов ИЛИ, выходы которой подключены к информационным входам накапливающего сумматора-вы- читателя приращений, а вторая группа входов первой группы :элемента ИЛИ соединена с информационными выходами регистра сдвига величины шага вход установки в единичное состояние которого подключен к дцадцать пятому выходу блока управления, двадцать шестой и двадцать седьмой выходы которого соединены соответственно с управляющими входами первого регистра коррекции и второго регистра дополнительной остаточной функции, информационные входы которого объединены с информационными входами первого регистра дополнительной остаточной функции и подключены к информационным выходам накапливающего сумматора-вычитателя оценочной функции, а информационные выходы соединены с первой группой входов второго дополнительного узла параллельного переноса, вторая группа входов которого соединена с информационными выходами первого регистра дополнительной оценочной функции, а управляющий вход которого подключен к двадцать восьмому выходу блока управления, двадцать девятый выход которого соединен с управляющим входом второго дополнительного узла параллельного переноса, выходы которого подключены к первой группе входов второй группы элементов ИЛИ, вторая группа входов которой соединена с выходами третьего узла параллельного переноса а выходы подключены к второй группе информационных входов накапливающего сумматора-вычитателя оценочной функции.

нет

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1987 |

|

SU1413602A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Круговой интерполятор | 1982 |

|

SU1081623A1 |

| Линейный интерполятор | 1986 |

|

SU1383302A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах числового управления станками и другим технологическим оборудованием. Целью изобретения является повышение быстродействия путем сокращения времени расчета приращений на участках с постоянной контурной скоростью. Интерполятор дополнительно содержит первый и второй узлы параллельного переноса, первую и вторую группы элементов ИЛИ, первый и второй регистры дополнительных остаточных функций, первый и второй регистры коррекции и новые связи. 4 ил.

С конец, 3

Фиг.З

J.

Установка di/ffff интерполяции

L

Р йС Х У Pcjf fcvNIfi-0

Линейная интерполяция

j

fcy f;jy dCI

г

ФигА

| Круговой интерполятор | 1982 |

|

SU1081623A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-02-07—Публикация

1988-02-25—Подача