Предлагаемое устройство для осуществления этого способа снабжено шестью элементами памятис входами запоминания и стирания и блоком выбора минимальной величины, причем входы запоминания элементов памяти соединены с выходом блока выделения максимальной величины, входы считывания элементов памяти связаны с датчиками положительного анодного напряжения соответствующих тиристоров инвертора, а выходы элементов памяти подключены к блоку выбора минимальной величины.

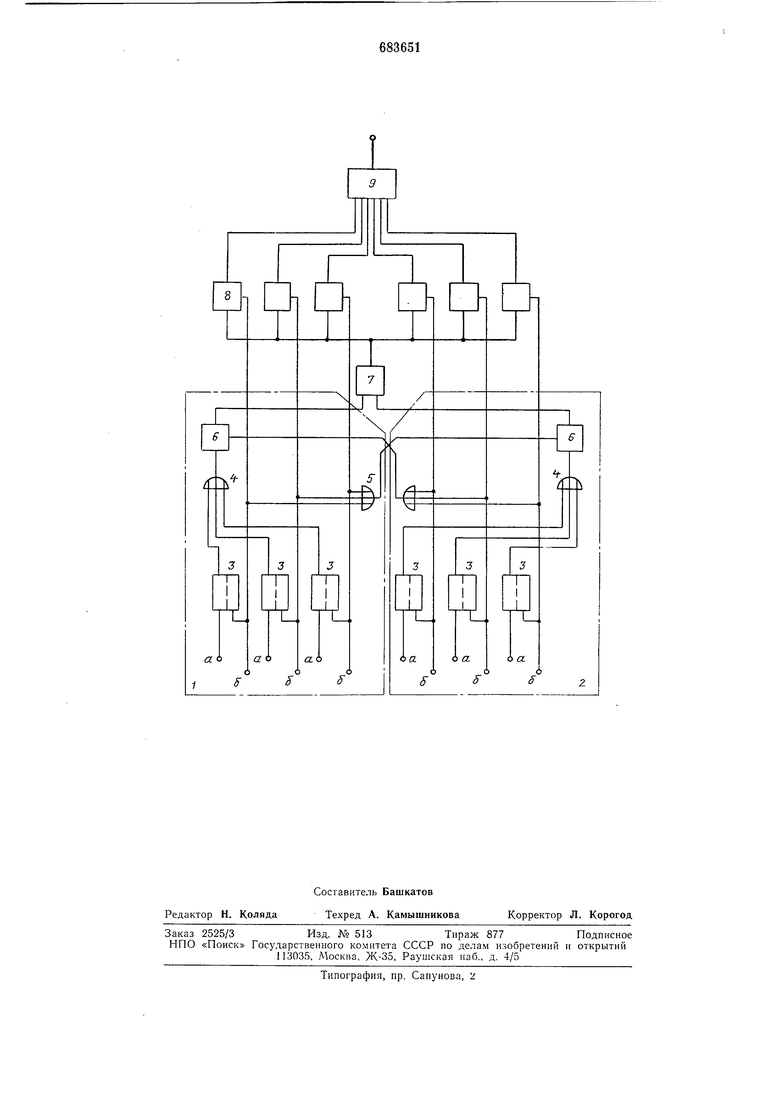

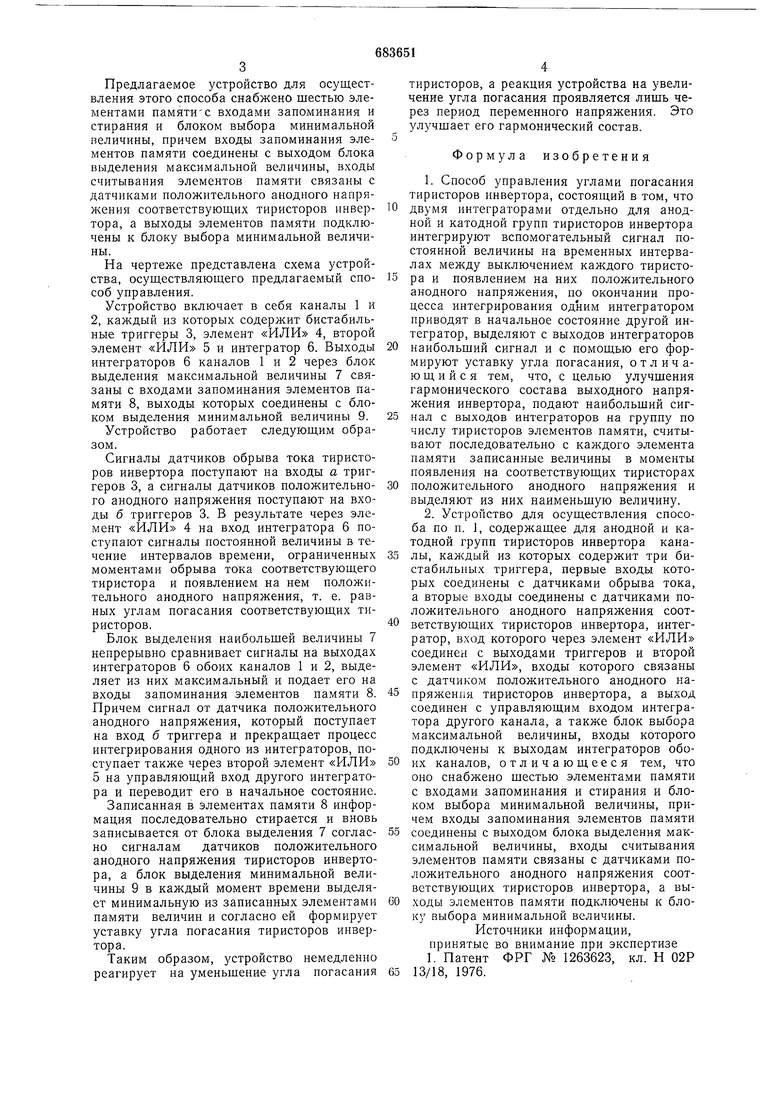

На чертеже представлена схема устройства, осуществляющего предлагаемый способ управления.

Устройство включает в себя каналы 1 и 2, каждый из которых содержит бистабильные триггеры 3, элемент «ИЛИ 4, второй элемент «ИЛИ 5 и интегратор 6. Выходы интеграторов 6 каналов 1 и 2 через блок выделения максимальной величины 7 связаны с входами запоминания элементов памяти 8, выходы которых соединены с блоком выделения минимальной величины 9.

Устройство работает следующим образом.

Сигналы датчиков обрыва тока тиристоров инвертора поступают на входы а триггеров 3, а сигналы датчиков положительного анодного напряжения поступают на входы б триггеров 3. В результате через элемент «ИЛИ 4 на вход интегратора 6 поступают сигналы постоянной величины в течение интервалов времени, ограниченных моментами обрыва тока соответствующего тиристора и появлением на нем положительного анодного напряжения, т. е. равных углам погасания соответствующих тиристоров.

Блок выделения наибольщей величины 7 непрерывно сравнивает сигналы на выходах интеграторов 6 обоих каналов 1 и 2, выделяет из них максимальный и подает его на входы запоминания элементов памяти 8. Причем сигнал от датчика положительного анодного напряжения, который поступает на вход б триггера и прекращает процесс интегрирования одного из интеграторов, поступает также через второй элемент «ИЛИ 5 на управляющий вход другого интегратора и переводит его в начальное состояние.

Записанная в элементах памяти 8 информация последовательно стирается и вновь записывается от блока выделения 7 согласно сигналам датчиков положительного анодного напряжения тиристоров инвертора, а блок выделения минимальной величины 9 в каждый момент времени выделяет минимальную из записанных элементами памяти величин и согласно ей формирует уставку угла погасания тиристоров ипвертора.

Таким образом, устройство немедленно реагирует на уменьшение угла погасания

тиристоров, а реакция устройства на увеличение угла погасания проявляется лищь через период переменного напряжения. Это

улз чщает его гармонический состав.

Формула изобретения

1.Способ управления углами погасания тиристоров инвертора, состоящий в том, что

двумя интеграторами отдельно для анодной и катодной групп тиристоров инвертора интегрируют вспомогательный сигнал постоянной величины на временных интервалах между выключением каждого тиристора и появлением на них положительного анодиого напряжения, по окончании процесса интегрирования одним интегратором приводят в начальное состояние другой интегратор, выделяют с выходов интеграторов

наибольший сигнал и с помощью его формируют уставку угла погасания, отличающийся тем, что, с целью улучшения гармонического состава выходного напряжения инвертора, подают наибольший сигнал с выходов интеграторов на группу по числу тиристоров элементов памяти, считывают последовательно с каждого элемента памяти записанные величины в моменты появления на соответствующих тиристорах

положительного анодного напряжения и выделяют из них наименьшую величину.

2.Устройство для осуществления способа по п. 1, содержащее для анодной и катодной групп тиристоров инвертора каналы, каждый из которых содержит три бистабильных триггера, первые входы которых соединены с датчиками обрыва тока, а вторые входы соединены с датчиками положительного анодного напряжения соответствующих тиристоров инвертора, интегратор, вход которого через элемент «ИЛИ соединен с выходами триггеров и второй элемент «ИЛИ, входы которого связаны с датчиком положительного анодного папряжения тиристоров инвертора, а выход соединен с управляющим входом интегратора другого канала, а также блок выбора максимальной величины, входы которого подключены к выходам интеграторов обоих каналов, отличающееся тем, что оно снабжено шестью элементами памяти с входами запоминания и стирания и блоком выбора минимальной величины, причем входы запоминания элементов памяти

соединены с выходом блока выделения максимальной величины, входы считывания элементов памяти связаны с датчиками положительного анодного напряжения соответствующих тиристоров инвертора, а выходы элементов памяти подключены к блоку выбора минимальной величины. Источники информации, принятые во внимание при экспертизе 1. Патент ФРГ № 1263623, кл. Н 02Р

13/18, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

| Способ управления непосредственным преобразователем частоты для регулируемого электропривода с широтно-импульсным регулированием (шир) выходного напряжения и непосредственный преобразователь частоты для регулируемого электропривода | 1978 |

|

SU858200A1 |

| Источник питания электрофильтра | 1983 |

|

SU1201807A1 |

| УСТРОЙСТВО ТЕПЛОВОЙ ЗАЩИТЫ ДВИГАТЕЛЯ | 2012 |

|

RU2499340C2 |

| Устройство для контроля времени выключения тиристоров | 1990 |

|

SU1725316A1 |

| Устройство для измерения временных параметров сфигмографических кривых | 1980 |

|

SU900219A1 |

| Устройство для пуска синхронной машины | 1984 |

|

SU1264291A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ ТИРИСТОРНОГО ПРЕОБРАЗОВАТЕЛЯ | 1971 |

|

SU296201A1 |

| Устройство для выделения импульсной последовательности,имеющей экстремальную частоту | 1983 |

|

SU1233268A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ И ЗАЩИТЫ РЕВЕРСИВНОГО ТИРИСТОРНОГО ПРЕОБРАЗОВАТЕЛЯ | 2001 |

|

RU2183896C1 |

Авторы

Даты

1979-08-30—Публикация

1978-05-25—Подача