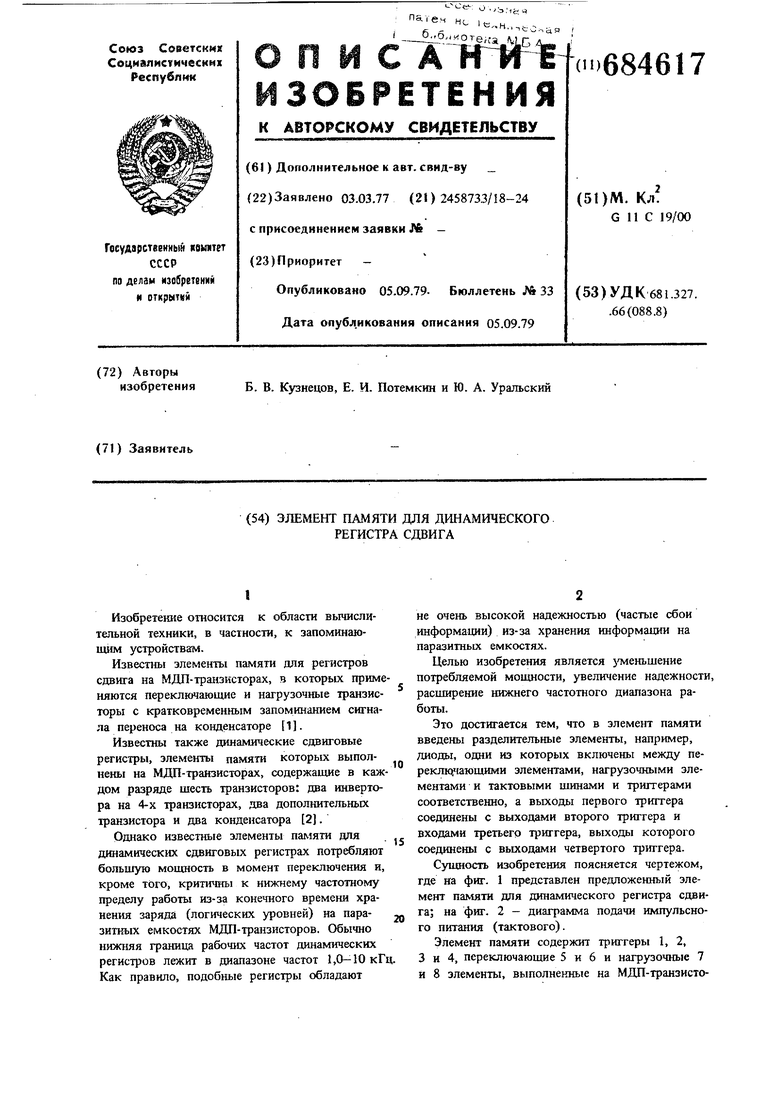

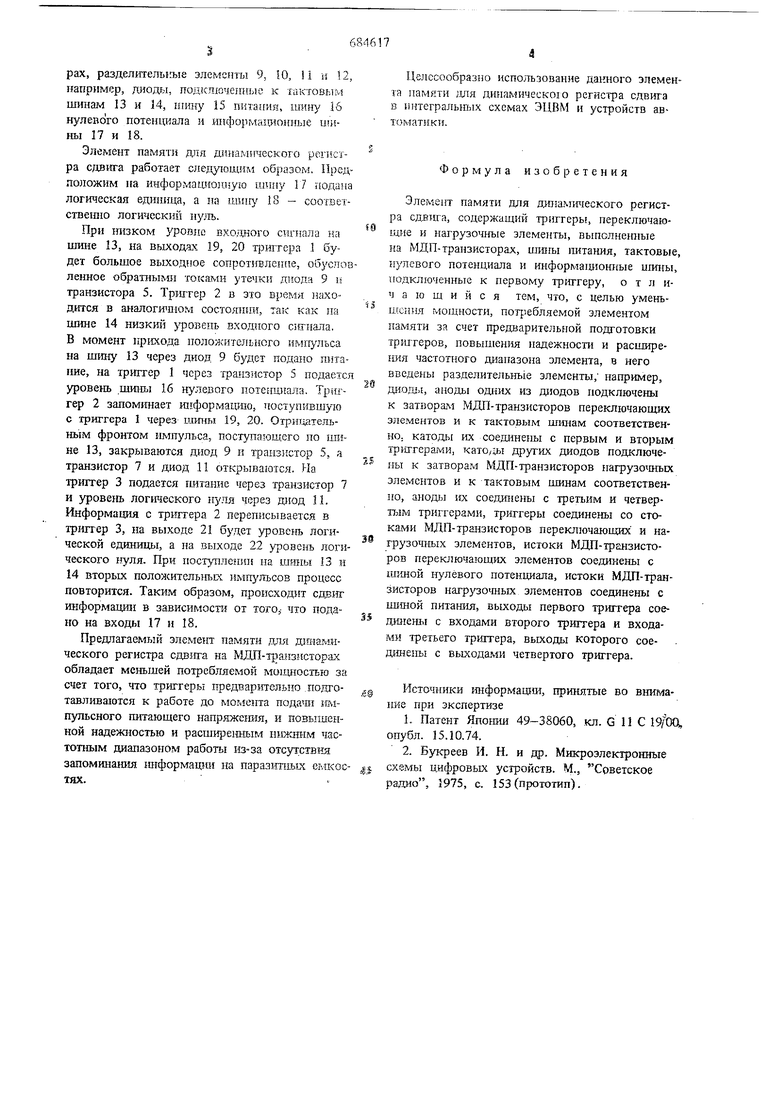

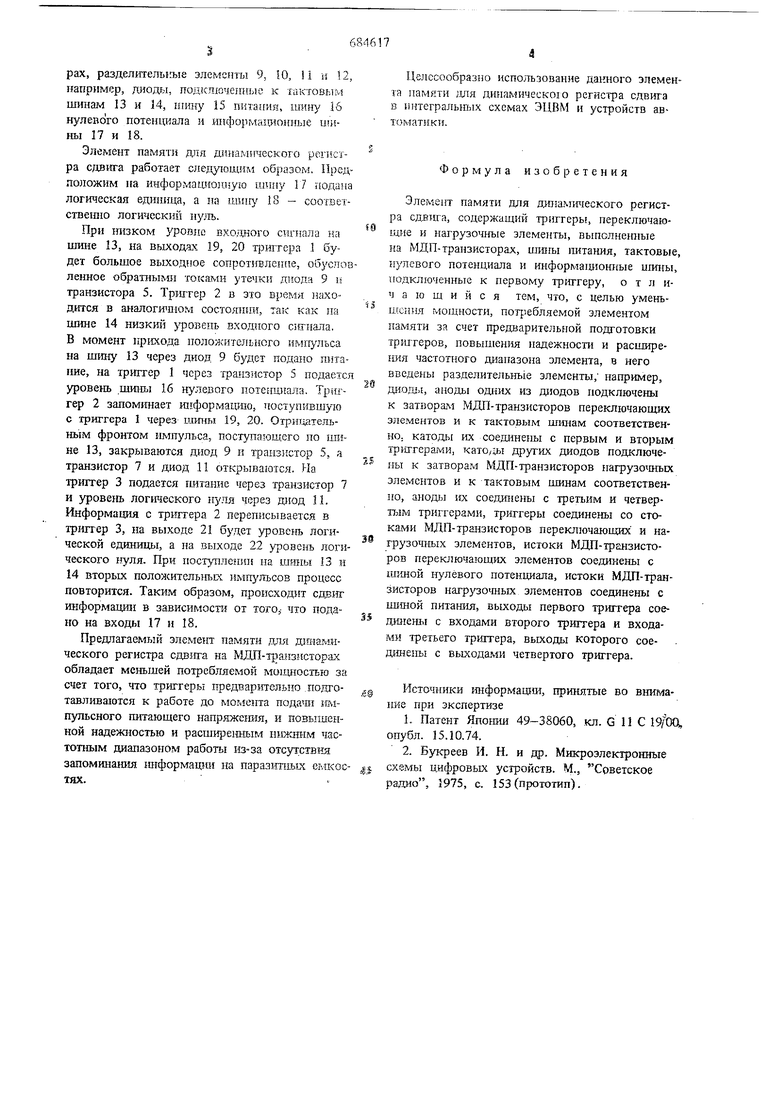

Изобретешь относится к области вычислительной техники, в частности, к запоминающим устройствам. Известны элементы памяти для регистров сдвига на МДП-транзисторах, в которых приме няются переключающие и нагрузочные транзисторы с кратковременным запоминанием сигнала переноса на конденсаторе 1 . Известны также динамические сдвиговые регистры, элементы памяти которых выполнены на МДП-транзисторах, содержащие в каж дом разряде шесть транзисторов: два инвертора на 4-х транзистс ах, два дополнительньк транзистора и два конденсатора 2. Однако известные элементы памяти для динамических сдвиговых регистрах потребляют большую мощность в момент переключения и, кроме того, критичны к нижнему частотному пределу работы из-за конечного времени хранешш заряда (логических уровней) на паразитных емкостях МДП-транзисторов. Обычно нижняя граница рабочих частот динамических регистров лежит в диапазоне частот 1,0-10 кГ Как правило, подобные регистры обладают не очень высокой надежностью (частые сбои информации) из-за хранения информации на паразитных емкостях. Целью изобретения является уменьшенное потребляемой мощности, увеличение надежности, расширение нижнего частотного диапазона работы. Это достигается тем, что в элемент памяти введены разделительные элементы, например, диоды, одни из которых включены между перекл10чающими элементами, нагрузочными элементами и тактовыми шинами и триггерами соответственно, а выходы первого триггера соединены с выходами второго триггера и входами третьего триггера, выходы которого соединены с выходами четвертого триггера. Сущность изобретения поясняется чертежом, где на фиг. 1 представлен предложенный элемент памяти для динамического регистра сдвига; на фиг. 2 - диаграмма подачи импульсного питания (тактового). Элемент памяти содержит триггеры 1, 2, 3 и 4, переключающие 5 и 6 и нагрузочные 7 и 8 злементы, выполненные на МДП-транзистоpax, разделительные элементы 9. 10, ii и 12, например, диоды, подключегагыс к тактовым шинам 13 и 14, шину 15 питания, imtiry 16 нулевого потенциала н ипформащюнные 17 и 18. Элемент памян для днналигаеского регистра сдвига работает следующим образом. Предположим на ннформацнозизую шпиу 17 гюдака логическая единица, а па 18 - соответственно логический нуль. При низком уровне входного сщцала на шине 13, на выходах 19, 20 трттера I будет большое выходное сопротивленпе, обуслов ленное обрагаыми токами утечки диода 9 н транзистора 5. Трштер 2 в это нжодится в ananorKinioM состоятгяи, так как на шине 14 низкий фовень входтюго citrnajia, В момент прихода ноложительного имгг/льса на шину 13 через диод 9 будет подано питаime, на триггер 1 через транзистор 5 подается уровень .шины 16 нулевого потеищгала. Триггер 2 запоминает информащсо, поступившую с триггера 1 через шины 19, 20. Отрицательным фронтом импульса, поступающего по uniне 13, закрываются диод 9 и транзистор 5, я транзистор 7 и диод 11 открываются. На триггер 3 подается гштание через транзистор 7 и уровень логического нуля через диод И. Информация с триггера 2 переписывается в ариггер 3, на выходе 21 бу.дет уровень логической единицы, а на выходе 22 уровень логи ческого нуля. При постз.Т1лени1 на шинь 13 и 14 вторых положительных импульсов нродесс повторится. Таким образом, происходит сдвиг информации в зависимости от того,- что подано на входы 17 и 18. Предлагаемый злемеш памяти для динамического регистра сдвига на МДП-транзисторах обладает меньшей потребляемой мовдюстыо за счет того, что триггеры предвар1Пельно .подготавливаются к работе до момента подаш saiпульсного питающего напряжеш-ш, и повышенной надежностью и расширенным HioKiniM частотным диапазоном работы из-за OTcyrciBiia запомина101я шгформащш на наразит11ых емкое тях. Целесообразно использование да1шого элемента памяти для динамическою регистра сдвига в янтегралыгых схемах ЭЦВМ и устройств автоматики. Формула изобретения Элемент памяти для ддшамического регистра сдвига, содержащий триггеры, переключающие и нагрузочные элементы, выполнеш1ые на МДП-транзисторах, шшгы 1титаьшя, тактовые, нулевого потенциала и информационные иш1{ы, подключенные к первому триггеру, о т л ичающийся тем, что, с целью уменьшения мощности, .ебляемой элементом памяти за счет предварительной подготовки трштеров, повышения надежности и расширения частотного диапазона элемента, в него введены разделительнь1е элементы, например, диод, аноды од11их из диодов подключены к затворам МДП-транзисторов переключающих элементов и к тактовым шинам соответственно. катод1 1 их соедине1ш с первым и вторым третгерами, като/;д 1 других диодов нодключеиы к затворам МДЦ-транзисторов нагрузо шых элементов и к тактовым шинам соответственно, аноды их соедш е1П)1 с третьим и четвертым триггерами, триггеры соединены со стоками МДЦ-транзисторов переключающих и нагрузочных элементов, истоки МДП-транзисторов переключающих элементов соединены с нулевого потенциала, истоки МДП-транзисторов нагрузочных элементов соединены с Ш1шой питания, выходы первого триггера соедш еш11 с входами второго триггера и входами третьего триггера, выходы которого соешт&11ы с выходами четвертого триггера. Источники информации, принятые во внимание при экспертизе 1.Патент Японш 49-38060, .кл. G 11 С 19/Оа опубл. 15.10.74. 2.Бу1феев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., Советское радио, 1975, с. 153(прототип).

ГИ1

13

ери г.7

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Запоминающий элемент | 1979 |

|

SU773738A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

г и а

14

tpus.2

Авторы

Даты

1979-09-05—Публикация

1977-03-03—Подача