1

Изобретение относится к вычисли. тельной технике, в часности к запоминающим устройствам цифровых вычислительных машин..

Известен запоминающий элемент йа МДП-транзисторах, содержащий триггер, управляющие МДП-транзистсры, разрядные и адресные шины i.

Известен также запоминающий элемент, содержащий триггер наМДП-тран- зисторах с нагрузочными МДП- ранзистором и диодом, включенными в развые плечи триггера |2.

Наиболее близким по технической сущности к предлагаемому является запоминающий элемент, содержащий триггер на МДП-транзисторах и управляющий МДП-транзистор, сток (исток) которого соединен с одним из плеч триггера, исток (сток) соединен с разрядной щиной, а затвор - с адресной шиной З Недостатком известных запоминающих элементов является значительное лотребление мощности.

Кроме того, статические запоминающие элементы на МДП-транзисторах требуют увеличенных геометрических размеров транзисторюв, что в случае интегрального исполнения увеличив ает площадь, занимаемую таким запоминающим элементом на кристалле. Как правило, такие схемы потребляют в момент переключения сравнительно большую мощность и обладают малой надежностью из-за частого пробоя подзатворного диэлектрика в мощных управляющ их транзисторах.

Целью изобретения является уменьшение потребляемой мощности.

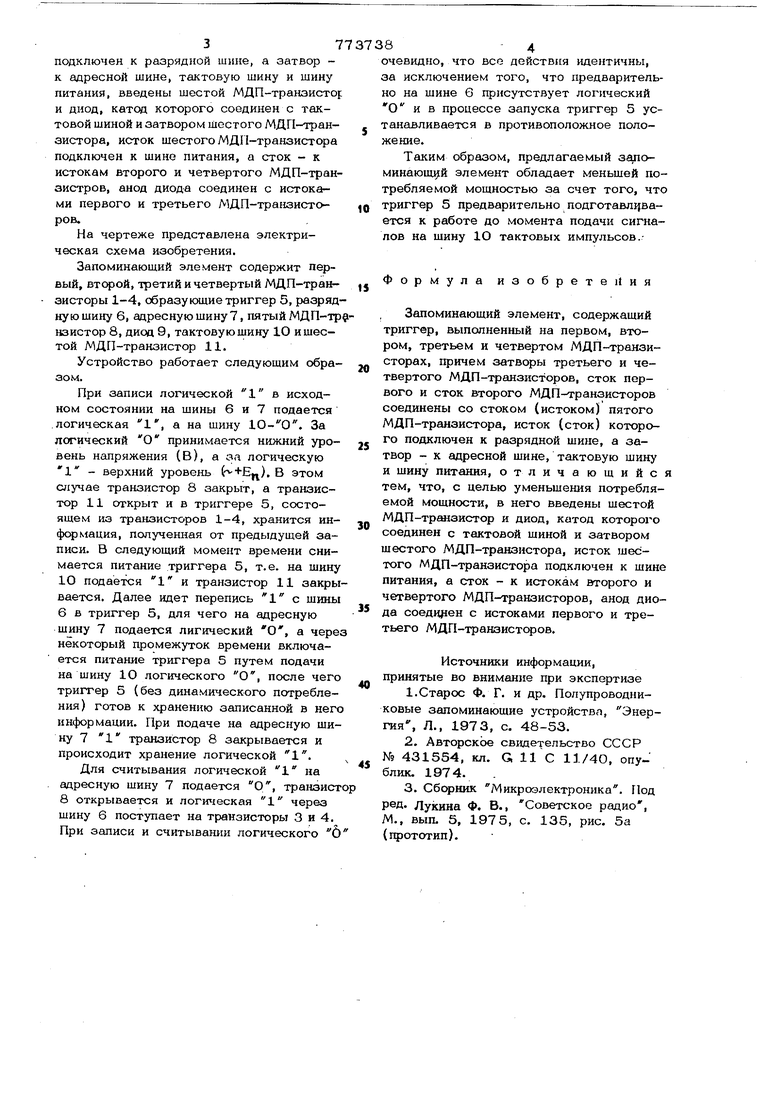

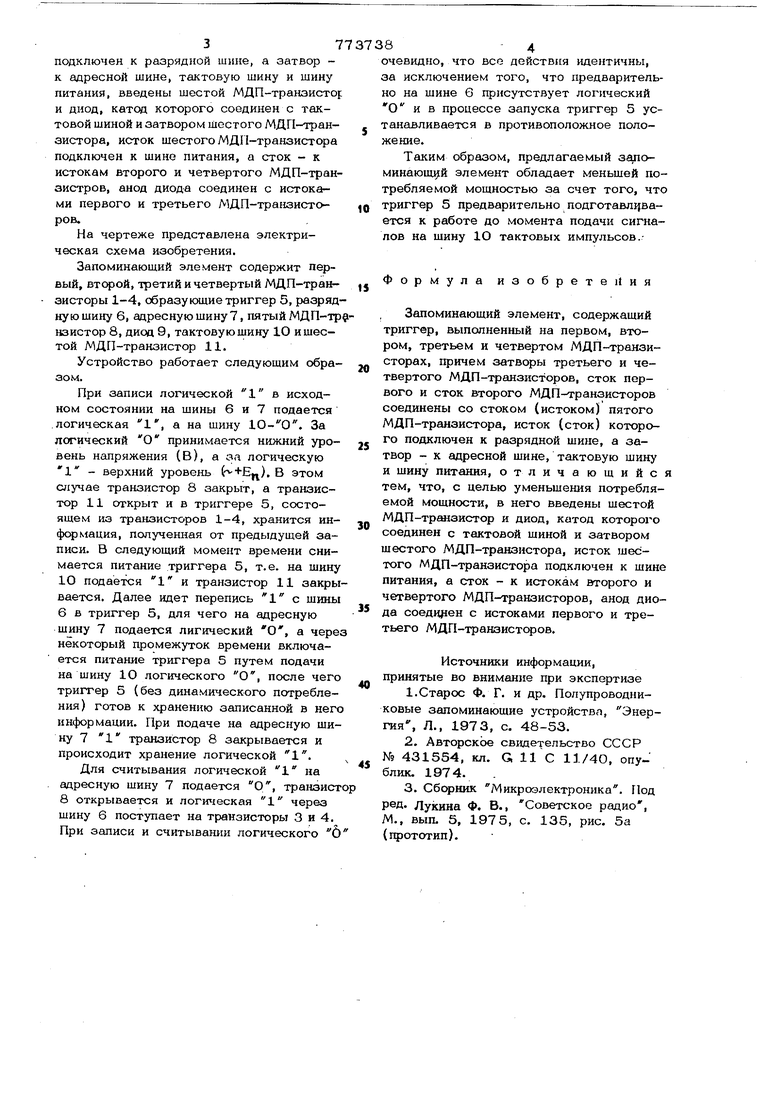

Поставленная цель достигается тем, что в запоминающий элемент, содержащий триггер, выполненный на первом, втором, третьем и четвертом МДП-транзисторах, причем затворы третьего и четвертого МДП-транзист(Чэов, сток первого и сток второго МДП-транзисторов соединены со стоком (истоком) пятого МДП-транзистора, исток (сток) которого подключен к разрядной шнне, а затвор к адресной шине, тактовую шину и шину питания, введены шестой МДП-транаисто1 и диод, катод которого соединен с тактовой шиной и затвором шестого МДП-транаистора, исток шестого МДП-транзистора подключен к шине питания, а сток - к истокам второго и четвертого МДП-транаистров, анод диода соединен с истоками первого и третьего МДП-транзисторов. На чертеже представлена электрическая схема изобретения. Запоминаюший элемент содержит первый, второй, третий и четвертый МДП-транаисторы 1-4, образующие триггер 5, разряд ную шину 6, адресную шину 7, пятый МДП-тр нзистор 8, диод 9, тактовуюшину 1О ишестой МДП-транзистор 11. Устройство работает следуюшим образом. При записи логической 1 в исходном состоянии на шины 6 и 7 подается .логическая 1, а на шину IO-О. За логический О принимается нижний уровень напряжения (В), а за логическую - верхний уровень (). В этом случае транзистор 8 закрыт, а транзистор 11 открыт и в триггере 5, состоящем из транзисторов 1-4, хранится информация, полученная от предыдущей записи, В следующий момент времени снимается питание триггера 5, т.е. на шину 1О подается 1 и транзистор 11 закры вается. Далее идет перепись I с шины 6 в триггер 5, для чего на адресную 7 подается лигический О , а чере некоторый промежуток времени включается питание триггера 5 путем подачи на шину 1О логического О, после чего триггер 5 (без динамического потребления) готов к хранению записанной в нег информации. При подаче на адресную шину 7 1 транзистор 8 закрывается и происходит хранение логической 1. Для считывания логической 1 на адресную шину 7 подается О, транзист 8 открывается и логическая 1 через шину 6 поступает на транзисторы 3 и 4. При записи и считывании логического 6 чевидно, что все действия идентичны, а исключением того, что предварительно на шине 6 присутствует логический О и в процессе запуска триггер 5 усанавливается в противоположное положение. Таким образом, предлагаемый запоминающуй элемент обладает меньшей потребляемой мощностью за счет того, что триггер 5 предварительно подготавл1}вается к работе до момента подачи сигналов на шину 1О тактовых импульсов.Формула изобретения Запоминаюший элемент, содержащий триггер, выполненный на первом, втором, третьем и четвертом МДП-транзисторах, причем затворы третьего и четвертого МДП-транзисторов, сток первого и сток второго МДП- ранзисторов соединены со стоком (истоком) пятого МДП-транаистора, исток (сток) которого подключен к разрядной шине, а затвор - к адресной шине, тактовую шину и шину питания, отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены шестой МДП-трШ13ИСтор и диод, катод которого соединен с тактовой шиной и затвором шестого МДП-трананстора, исток шестх го МДП-транзистора подключен к шине питания, а сток - к истокам второго и четвертого МДП-транаисторов, анод диода coeди eн с истоками первого и третьего МДП-транзисторов. Источники информации, принятые во внимание при экспертизе 1.Старое Ф. Г. и др. Полупроводниковые запоминающие устройства, Энергия, Л., 1973, с. 48-53. 2.Авторское свидетельство СССР № 431554, кл. G 11 С 11/40, опублик. 1974. 3.Сборник Микроэлектроника. Под ред. Лукина Ф. В., Советское радио , М., вып. 5, 1975, с. 135, рис. 5а (гфототип).

31

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| Многоканальный коммутатор | 1980 |

|

SU938406A1 |

| Элемент памяти для динамического регистра сдвига | 1977 |

|

SU684617A1 |

| Ячейка памяти для регистра сдвига | 1975 |

|

SU570108A1 |

| Квазистатическая ячейка памяти | 1975 |

|

SU598119A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| Асинхронный распределитель | 1987 |

|

SU1458968A1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-17—Подача