1

Изобретение относится к технике связи и может использоваться в аппаратуре передачи информации.

Известно устройство синхронизации по циклам, содержащее последовательно соединенные анализатор, первый элемент И и счетчик, а также второй элемент И и распределитель, выход которого подключен к другому входу первого элемента И, а вхбд соединен с выходом генератора тактовых импульсов 1).

Однако это устройство имеет большое время вхождения в синхронизм.

Цель изобретения - уменьшение времени вхождения в синхронизм.

Для этого в устройство синхронизации по циклам, содержащее последовательно соединенные анализатор, первый элемент И и счетчик, а также второй элемент И и распределитель, выход которого подключен к другому входу первого элемента И, а вход соединен с выходом генератора тактовых импульсов, введены последовательно соединенные первый и второй блоки запрета, первый делитель, дополнителы1ьш

счетчик, а также последовательно соединенные второй делитель и третий блок запрета, выход которого соединен с входом счетчика и входом второго делителя, второй вход которого соединен с выходом генератора тактовых импульсов

и вторым входом первого делителя, выход которого подключен к другому входу второго блока запрета, а третий вход первого делителя через второй элемент И соед1шен с выходом первого блока запрета, причем выход дополнительного счетчика соединен с выходом счетчика и подключенК другому входу распределителя, выход которюго подключен к другому входу первого блока запрета, другой вход которого подключен к выходу анализатора, а выход подключен к третьему входу второго делителя, другой выход которого подключен к другому входу второго элемента И, при этом выход первого блока запрета подключен к другому входу третьего блока запрета, а выход

второго блока запрета подключен к друтому входу дополнительного счетчика, причем выход второго делителя подключен к другому входу счетчика.

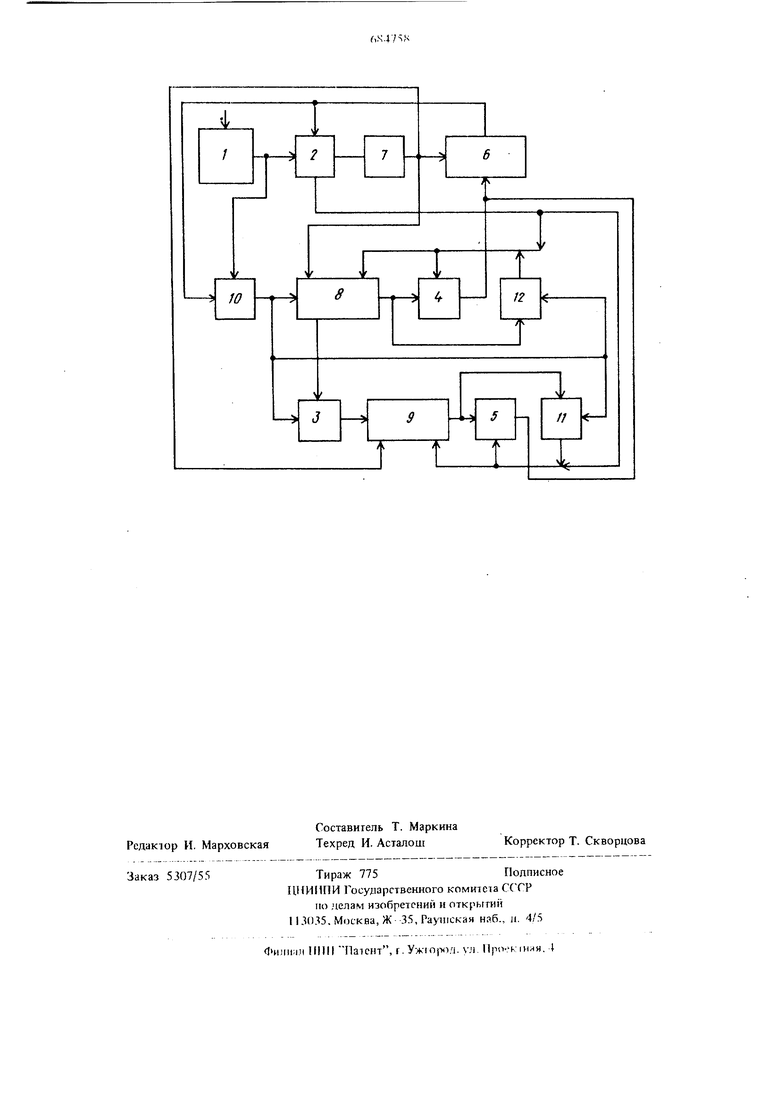

На чертеже изображена арук1у 1ная элск1риеская схема уетронс1ва.

Устройство сцнх.толизации но циклам содерит анализатор 1, элементы И 2. 3, счетчики , 5, распределитель 6, генератор 7 1актоиых мпульсов, делители 8, 9, блоки запрета 10-12. Устройство работает следующим образом. Информация, закодированная блочными (п, k) кодами, поступает в анализатор 1, на выходе которого с тактовой частотой появляются :я сигналы 1 при соответствии и О при несответствии п-разряд 1ой последовательности двоичных символов закону построения кода. Эти сигналы поступают на вход элемента И 2 и на вход блока 10 запрета, на другие входы KOTOpbix поступают сигналы, соответствующие -ой фазе распределителя6(К14п).

Если распределитель 6 сфазирован, то элемент И 2 вьщает сигнал Сброс, по которому устанавливаются в исходное состояние делители 8, 9 и счетт шки 4, 5, а на выходе блока 10 запрета сигнал будет отсутствовать. Если распределитель 6 не сфазирован, то сигналы соответствия с выхода анализатора 1 проходят через блок 10 запрета и запускают делитель 8, который начинает делить в п раз тактовую частоту, пос1упающую с генератора 7 на вход делителя 8.

Через п тактов делитель 8 выдает первый сигнал на вход счетчика 4 и на вход блока запрета 12, на вход которого поступают сигналы соответствия с выхода блока 10 запрета, которые запрещают (при их наличии) сброс делителя 8 и счетчика 4.

Таким образом, при наличии сигналов соответствия на J.-фазе распределителя 6, задаваемой делителем 8, счетчик 4 подсчитывает их число и при достижении определенного порога, например серии Г импульсов соответствия, выдает сигнал на вход распределителя 6, фазируя его.

. При отсутствии подтверждения сигналов соответствия импульс с выхода делителя 8 проходит через блок запрета 12 и устанавливает делитель 8 и счетчик 4 в исходное состояние. Во время работы делителя 8 с выхода его на вход элемента И 3 поступает разрешающий сигнал, задержанный на один такт относительно запуска делителя 8. Поэтому, если кроме первого сигнала соответствия, выделяемого на J--oй фазе распределителя 6, на последующих фазах распределителя 6 выделится второй сигнал соответствия, то он проходит через элемент И 3 и запускает делитель 9, с выхода

1

которой) заиуекатся счсшик 5, К( считас , идущие i:niiiajii,i ccxniSLMciiiHti и при дпс1ижении опредсленкого гк)Х)1а, например, серии г сигналов соответствия, В1 |дает

импульс на вход распределителя 6, фазируя с го.

При отсутствии подтверждения сигналов соответствия по дополнительному каналу выделени.ч фазы сигнал с выхода делителя 9 прохо;шт

через блок II запрета и устанавливает делитель 9 и 5 в исходное состояние.

Формула изобретения

Устройство синхронизации по циклам, содержащее последовательно соединенные анализатор, первый элемент И и счетчик, а также второй элемент И и распределитель, выход которого подключен к другому входу первого элемент-а И, а вход соединен с выходом генератора тактовых импульсов, отличающееся тем, что, с целью уменьшения времени вхождения в синхронизм, введены последова-« тельно соединенные первый и второй блоки запрета, первый делитель, дополнительный счетчик, а также последовательно соединенные второй делитель и третий блок запрета, выход которого соединен с входом счетчика и входом второго делителя, второй вход которого соединен с вь ходом генератора тактовых импульсов и вторым входом первого делителя, выход которого подключен к другому входу второго блока запрета, а третий вход первого делителя через второй элемент И соединен с выходом первого блока запрета, причем выход дополнительно о счетчика соединен с выходом счетчика и подключен к другому входу распределителя, выход которого подключен к другому входу первого блока запрета, другой вход которого подключен к выходу анализатора, а выход подключен к третьему входу второго делителя, другой выход которого подключен к другому входу второго элемента И, при этом выход первого блока запрета подключен к другому входу третьего блока запрета, а выход второго блока запрета подключен к другому входу дополнительного счетчика, причем выход второго делителя подключен к другому входу счетчика.

Исто1шики информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 4987.52, кл. Н 04 L 7/08, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1983 |

|

SU1172053A1 |

| Устройство поэлементной синхронизации | 1981 |

|

SU987834A1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Способ передачи сигналов точного времени по линиям связи с переменным временем распространения и устройство для его реализации | 1979 |

|

SU858058A1 |

| Устройство для асинхронной передачицифРОВОй иНфОРМАции пО СиНХРОННОМуКАНАлу СВязи | 1978 |

|

SU807495A1 |

| Устройство групповой тактовой синхронизации | 1982 |

|

SU1022325A2 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Устройство для измерения интегральной функции распределения времени вхождения в синхронизм | 1973 |

|

SU477550A1 |

| Способ управления циклоконвертором и устройство для его осуществления | 1983 |

|

SU1137557A1 |

Авторы

Даты

1979-09-05—Публикация

1978-02-16—Подача